Makefile的简介

Makefile 是和 make 命令一起配合使用的.

很多大型项目的编译都是通过 Makefile 来组织的, 如果没有 Makefile, 那很多项目中各种库和代码之间的依赖关系不知会多复杂.

Makefile的组织流程的能力如此之强, 不仅可以用来编译项目, 还可以用来组织我们平时的一些日常操作. 这个需要大家发挥自己的想象力.

Makefile的通用结构

# 以‘#’开头的行表示注释

#定义变量VAR,强制赋值为test

VAR=test

#在VAR之前定义的值后面再追加app这个值,这时该变量值扩展为testapp

VAR+=app

#如果之前VAR没有被定义,则定义并使用testapp;否则使用之前的值。

VAR?=testapp

#第一条目标为总的目标

#依赖可以是文件(目录)或为其他目标

#动作可以是Linux命令,动作的那一行必须以TAB键开头

target: depend1 depend2 depend3 …

【TAB】 action1

【TAB】action2

target1;

【TAB】action1

【TAB】action2

Mkfile的简单示例

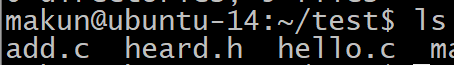

首先我们需要在linux下创建一个文件夹,里面需要写两个.c文件和一个头文件

hello.c文件代码

#include <stdio.h>

#include "heard.h"

int main (int argc, char **argv)

{

int a=5;

int b=6;

int c;

c=add(&a,&b);

printf("%d\n",c);

printf("hello world\n");

return 0;

}

add.c的文件代码

#include <stdio.h>

int add(int *a, int *b);

int add(int *a, int *b)

{

int c;

c=(( *a)+( *b));

return c;

}

heard.h的头文件

int add(int *a, int *b);

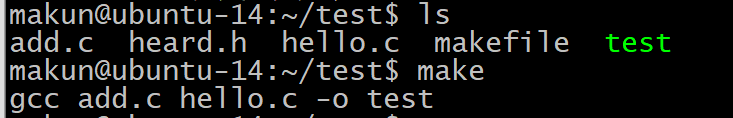

在没有学习makefile之前我们编译的时候需要编译运行的时候需要输入

gcc hello.c gcc add.c -o test

如果我们每次运行都要输入这一行,显得很麻烦,如果我们使用makefile的使用会使这个变得更加简单起来,

vim makefile

#定义变量

APP_NAME= test

cc=gcc

#这里的all是整个makefile文件的第一个目标,也就是总的目标,当我们输入make的命令时就是完成这个目标

all:

${cc} add.c hello.c -o ${APP_NAME}

#clean是一个单独的目标,该目标没有被总的目标all依赖或执行,所以默认该目标不会被执行,如果想执行该目标,则可以在Linux命令行下输入make clean来执行

clean:

rm -f ${APP_NAME}

当我们敲make的时候,就完成没有学makefile的操作。

当我们敲make clean的时候,test就会被删除

上面所讲到的东西都是关于makefile的简单使用,如果想要了解更多知识点,可以推荐大家一篇博客,供大家学习

Makefile的详细介绍