I / O管理

文章目录

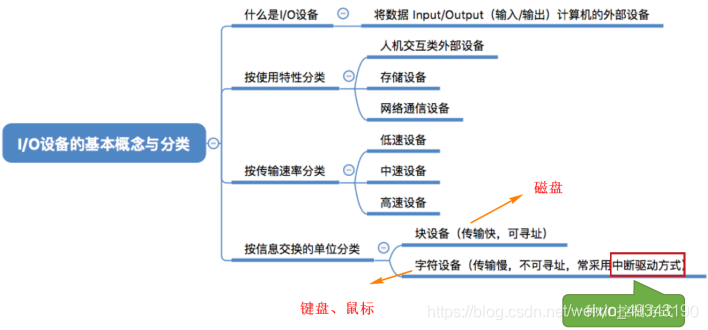

一、I/O设备的基本概念和分类

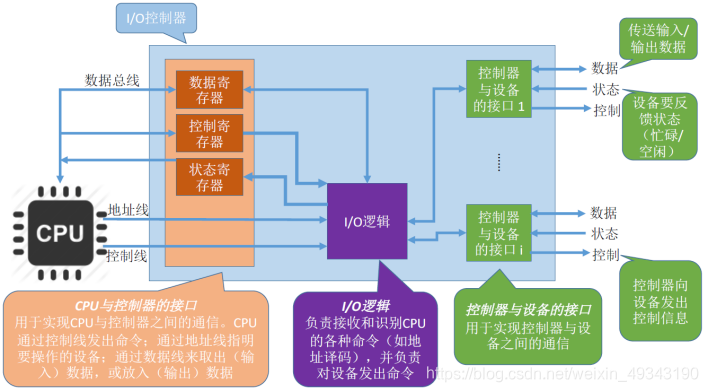

二、I/O控制器

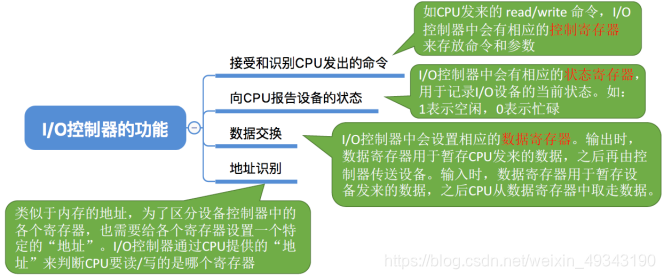

1. I/O控制器的介绍和功能

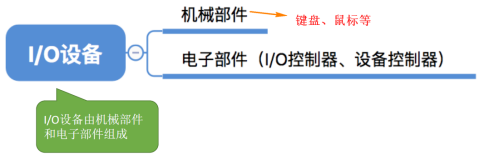

(1) I/O控制器的介绍

CPU无法直接控制I/O设备的机械部件,故需要I/O控制器作为中介,CPU控制I/O控 制器,I/O控制器控制设备的机械部件

(2) I/O控制器的功能

2. I/O控制器的组成

三、I/O控制方式

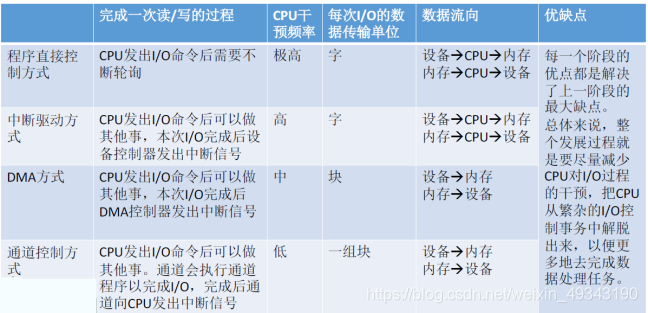

用什么样的方式来控制I/O设备的数据读/写

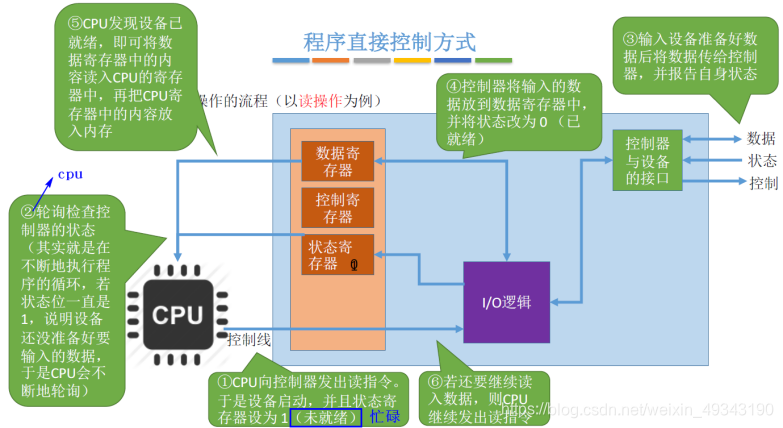

- 程序直接控制方式

(1) CPU干预的频率

非常频繁,I/O操作开始之前、完成之后需要CPU介入,并且在等待I/O完成的过程中CPU 需要不断的轮询检查

(2) 数据传送的单位:字

(3) 数据的流向

读操作:I/O设备 → 寄存器 → 内存

写操作:内存 → 寄存器 → I/O设备

2. 中断驱动方式

引入中断机制;在CPU发出读/写命令之后,将等待I/O的进程阻塞,先切换到别的进程;当I/O 完成后,控制器会向CPU发送一个中断信号,CPU会处理中断,完成读/写操作

(1) CPU干预的频率

每次I/O操作开始之前、完成之后需要CPU介入

等待I/O完成的过程中CPU可以切换到别的进程执行

(2) 数据传送的单位:字

(3) 数据的流向

读操作:I/O设备 → 寄存器 → 内存

写操作:内存 → 寄存器 → I/O设备

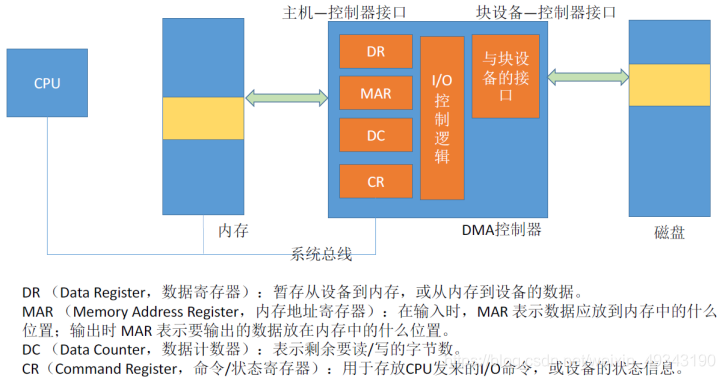

3. DMA方式(直接存储器存取)

(1) 数据的传送单位是块

(2) 数据的流向是从设备直接放入内存,或者从内存中直接到设备,无需CPU干预

(3) 仅在传送数据块的开始和结束时才需要CPU的干预

(4) CPU告诉DMA此次要进行的操作、操作的数据量、数据存放的位置等信息

(5) DMA会根据CPU的要求完成操作,I/O完成之后才向CPU发送中断信号

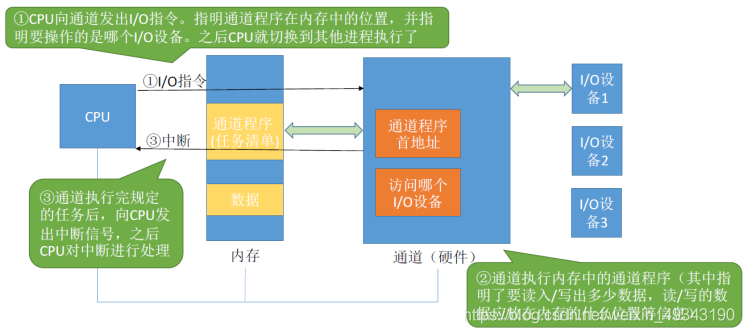

4. 通道控制方式

通道是一种硬件,可以理解为”性能较差的CPU”,可识别并执行通道指令

(1) CPU干预的频率

频率很低,通道会根据CPU的指示执行相应的通道程序,只有完成一组数据块的读/写后才 需要发出中断信号,请求CPU干预

(2) 数据传送的单位:一组数据块

(3) 数据的流向

读操作:I/O设备 → 内存

写操作:内存 → I/O设备

5. 知识回顾

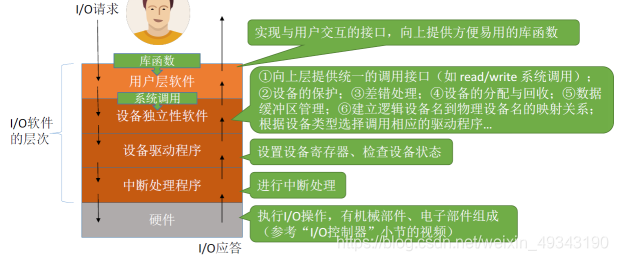

四、I/O软件层次结构

设备独立性软件:与设备的硬件特性无关的功能几乎都在这一层实现

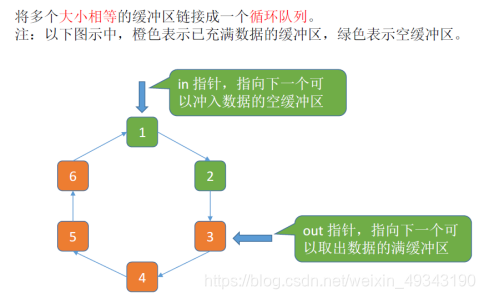

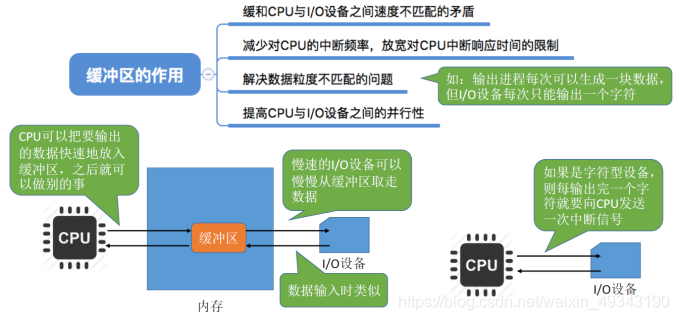

五、缓冲区管理

1. 缓冲区作用

注意:缓冲区数据非空时,不能往缓冲区冲入数据,只能从缓冲区把数据传出;当缓冲区为空 时,才可以往缓冲区冲入数据;缓冲区满了之后,才能将数据取出

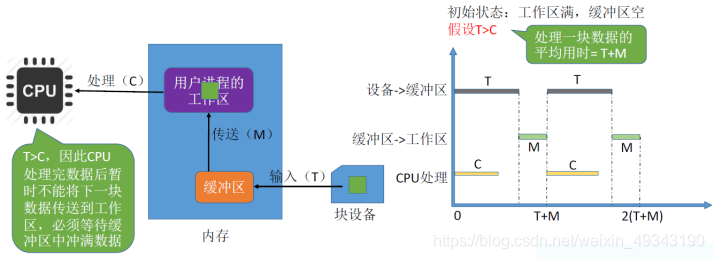

2. 单缓冲

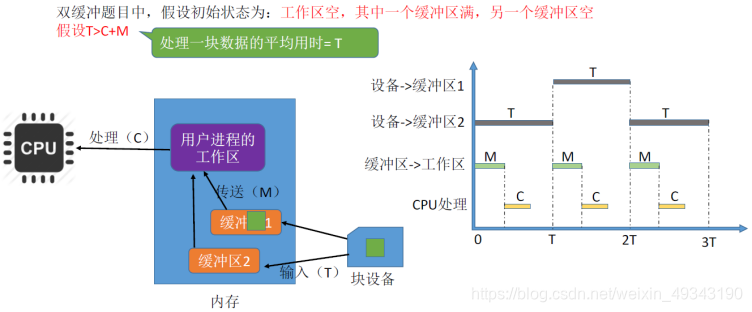

3. 双缓冲

4. 循环缓冲区