正版链接:https://blog.csdn.net/meenr/article/details/117549977

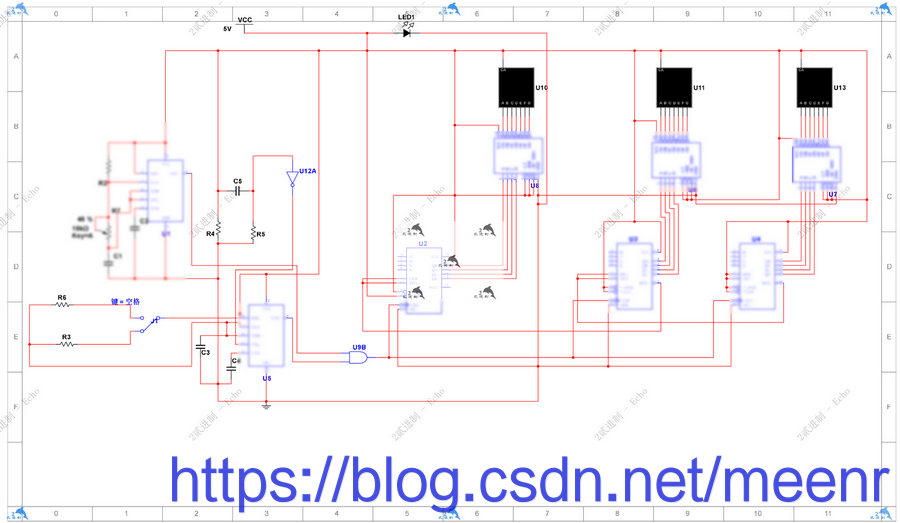

最简单电路实现两个量程档位的数字电容测量仪

仿真图等资料在文末

目录

1 设计指标及要求

1.1 设计要求

电路板能够正常工作,仿真能够正常使用,实现功能,达到设计要求:

(1)可测量容量在1nF至1uF范围内的电容;

(2)三位显示;

扩展要求:可测量容量在1nF至1000uF范围内的电容。能够分别测量两个量程的电容,数码管显示数据与实际电容数据误差在允许范围内。

1.2 实现效果

实际测量两个量程内的电容时,数码管显示出的测量数值与待测电容实际值基本相同,能够分别测量纳法量程:1nF—1000nF和微法量程:1uF—1000uF两个量程的电容,能够清零置数。

2 系统方案设计

2.1 设计方案一

应用基本思想:把较难测量的物理量转变成精度较高且较容易测量的物理量。转换的原理是由于单稳态触发器的输出脉宽tw与电容C成正比,可利用数字频率计的知识,把此脉冲作闸门时间和标准频率脉冲相“与”,得到计数脉冲,该计数脉冲送至计数一锁存一译码一显示系统就可得到电容量的数值。

2.2 设计方案二

像测量R一样,测量电容C的最经典方法是电桥法,如图1所示。只是电容C要用交流电桥测量。电桥的平衡条件是:

2.3 方案选择

本设计中用振荡器产生一定周期的矩形脉冲作为计数器的CP脉冲也就是标准频率。同时把待测电容C转换成宽度为tw的矩形脉冲,转换的原理是单稳态触发器的输出脉宽tw与电容C成正比。这种转换就是把模拟量转换成数字量,频率f是数字电路中很容易处理的数字量,这种数字化处理一方面便于仪表智能化,另一方面也避免了有指针读数引起的误差。

3 系统硬件电路设计

3.1 整体电路说明及系统框图

共五个模块:

- 数码管及译码器

- 计数器

- 单稳态触发器

- 多谐振荡器

- 量程档

3.2 单元电路介绍

3.2.1 数码管及译码器

一位共阴极数码管及译码器。三个译码器输入端分别对应接三个计数器的输出端、输出端连接限流电阻后分别接入三个数码管,数码管公共端一端接地。译码器其他功能扩展端,3、4、5脚接Vcc。来自计数器的计数信号传递给译码器,译码器转换为输出高电平有效的七段字符显示器的驱动信号,数码管显示相应数字。

3.2.2 计数器

- 异步清零功能

只要(CR的非)有效电平到来,无论有无CP脉冲,输出为“0”。在图形符号中,CR的非的信号为CT=0,若接成七进制计数器,这里要特别注意,控制清零端的信号不是N-1(6),而是N(7)状态。其实,很容易解释,由于异步清零端信号一旦出现就立即生效,如刚出现0111,就立即送到(CR的非)端,使状态变为0000。所以,清零信号是非常短暂的,仅是过度状态,不能成为计数的一个状态。清零端是低电平有效。

- 同步置数功能

当(LD的非)为有效电平时,计数功能被禁止,在CP脉冲上升沿作用下D0~D3的数据被置入计数器并呈现在Q0~Q3端。若接成七进制计数器,控制置数端的信号是N(7)状态,如在D0~D3置入0000,则在Q0~Q3端呈现的数据就是0110。

3.2.3 单稳态触发器

定时器构成的单稳态触发器由芯片构成的单稳态触发器电路及工作波形如图所示。图中R,C为外接定时元件,输人的触发信号ui接在低电平触发端。稳态时,输出uo为低电平,即无触发器信号(ui为高电平)时,电路处于稳定状态——输出低电平。在ui负脉冲作用下,低电平触发端得到低于(1/3)Vcc,触发信号,输出uo为高电平,放电管VT截止,电路进入暂稳态,定时开始。在暂稳态期间,电源+Vcc→R→C→地,对电容充电,充电时间常数T=RC,uc按指数规律上升。当电容两端电压uc上升到(2/3)Vcc后,6端为高电平,输出uo变为低电平,放电管VT导通,定时电容C充电结束,即暂稳态结束。电路恢复到稳态uo为低电平的状态。当第二个触发脉冲到来时,又重复上述过程。工作波形图如图7所示。

可见,输人一个负脉冲,就可以得到一个宽度一定的正脉冲输出,其脉冲宽度tw取决于电容器由0充电到(2/3)Vcc,所需要的时间。可得:

3.2.4 多谐振荡器

由芯片构成的多谐振荡器,多谐振荡器是芯片应用的基本电路,是指电路没有稳定状态(即方波发生器),只有两个暂稳态,其功能是产生一定频率和幅度的矩形波信号,其输出状态不断在“1”和“0”之间变换。

在加电状态下,由于电容C上电压不能突变,故芯片处于置位状态,uo=1,放电管TD截止(7脚与地断开),Vcc通过R1,R2对电容C进行充电,当uc上升到时,uo=0,TD导通,电容C端电压通过R2和放电管TD对地进行放电,uc下降。当uc下降到时,uo又由0变为l,TD截止,Vcc又经R1和R2对C充电。如此重复上述过程,在输出端uo产生了连续的矩形脉冲,如图8所示。其中,R1,R2和C是定时元件,它们决定了电路的充放电时间。

4 系统调试

4.1 调试现象

- 实测电容计算误差

成品完成后,通过测量几个量程内的标准电容来进行校准,保证误差在允许范围。测量470uF电容时得到的数值是448uF,误差大小为4.68%;测量100nF电容时得到的数值是100nF误差大小为0%。符合设计要求。下面列举测量470uF和100nF标准电容时的实际数值照片。

4.2 设计问题

1.数码管的选择

共阳的数码管接Vcc,共阴的数码管接GND。

2.在数码管与译码器之间没有加限流电阻

资料获取

感兴趣的读者可参照以下方式获取本文相关资料。优先推荐途径一,若遇途径一失效,请再尝试途径二。

途径一

优先推荐该途径

第一步:扫描下方二维码,或打开微信搜索并关注“ 2贰进制 ”公众号;

第二步:回复相应内容即可获取本文相关资料。

途径二

优先推荐途径一,该途径管理可能不能秒回

扫描下方二维码,加入学习交流QQ群“ 480558240 ”,联系管理员获取包括但不限于本篇内容的更多学习资料。

2贰进制–Echo 2020年11月

我认同兴趣是最好的老师,但是除了兴趣其次是侮辱,所以如果您觉得本文还不错,请点赞+评论+收藏,要是关注那更是对我极大地羞辱了,您的羞辱便是我前进的动力!

如果本文对你有所帮助,解决了您的困扰,可以通过赞赏来给予我更大支持:

此致

感谢您的阅读、点赞、评论、收藏与打赏。