实验一 基于FPGA的计数器设计

1. 实验目的:

(1) 掌握QuartusⅡ软件的设计流程;

(2) 学习原理图设计方法和波形仿真方法。

2. 实验任务:

(1) 基本任务:采用原理图法设计一个十进制计数器,完成波形功能仿真和时序仿真。

(2) 拓展任务1:采用原理图法设计一个六进制计数器,完成波形功能仿真和时序仿真。

(3) 拓展任务2:通过编译、仿真等手段,在所提供的Lab1_mistake观察常见错误现象并记录。

3.实验步骤

基本任务:

(1)新建工程(包括quartus的下载与使用,具体可以看实验报告)

(2)设计电路

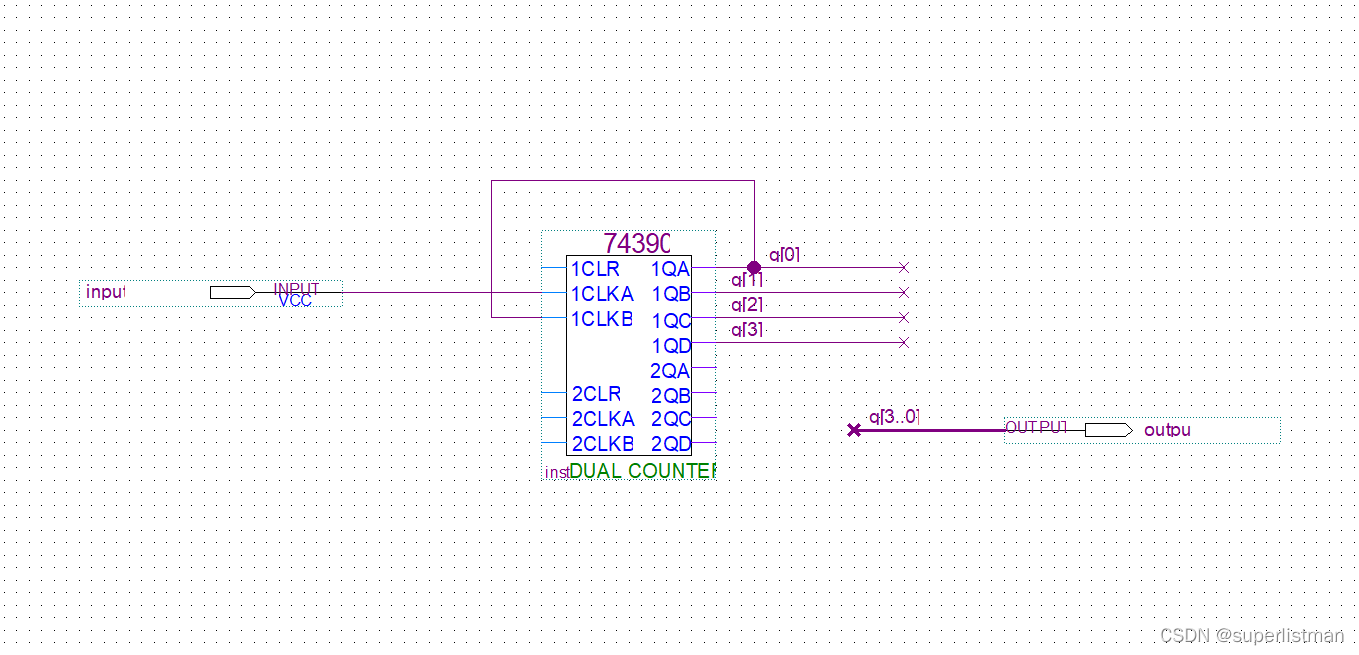

思路:利用集成的74390芯片。根据该芯片的功能表,将QA与CLKB相连为模10计数功能。通过总线将输出端QA,QB,QC,QD送到output端(最后会有工程文件下载连接)

拓展任务1:

(1)设计思路

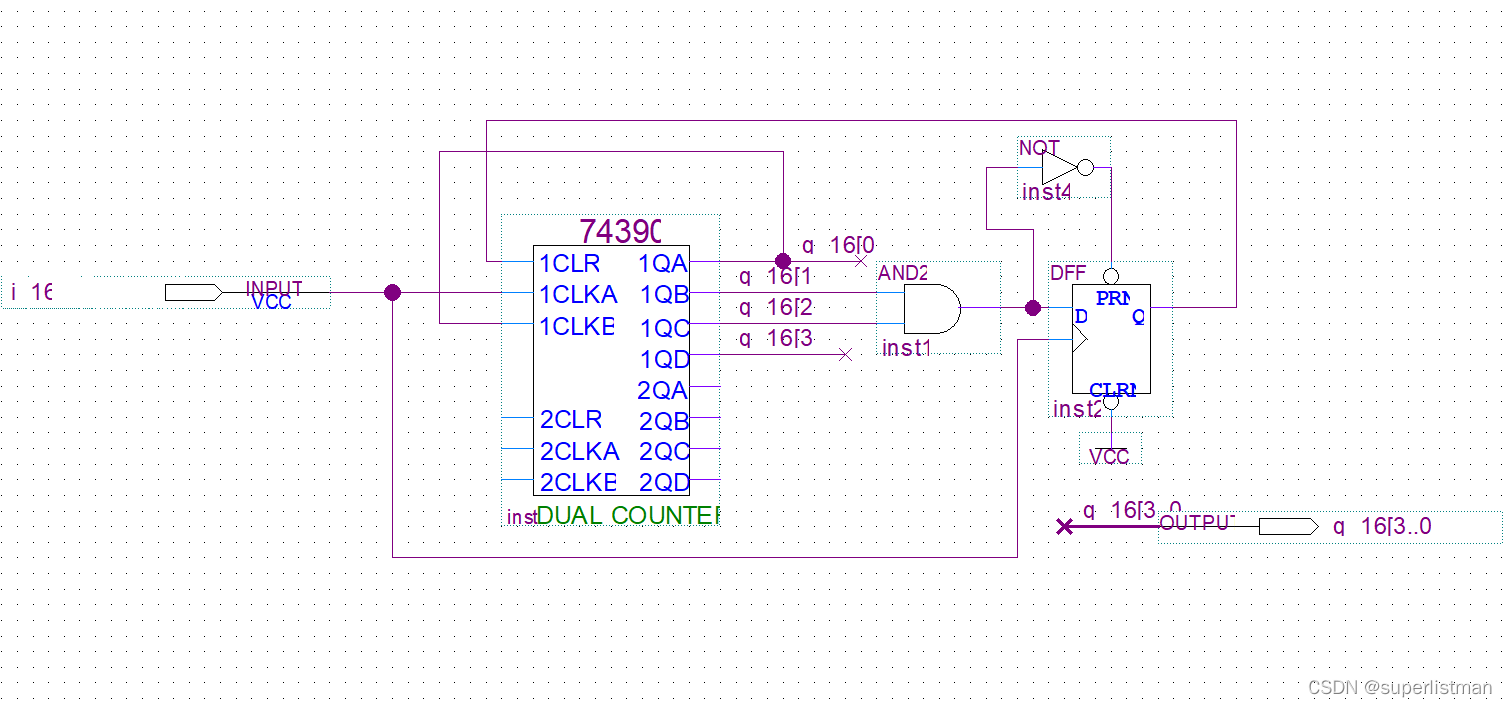

以基本任务设计的模10计数器为基础,模6计数器只要将模10计数器计数到6的时候清零,重新从0开始计数。

根据模10计数器的真值表可知QB与QC同时为1时,将QA,QB通过双输入与非门输出到清零端(1CLR)

我后面的电路是一个防止竞争冒险现象的电路,是当时我们的附加题,实际上只要将AND2与非门的输出端直接连接到1CLR就行了。

(2)电路设计

拓展任务2

通过编译、仿真等手段,在所提供的Lab1_mistake观察常见错误现象并记录。

(仅供参考,题目可能不一样)

Mistake1:文件命名为123,错误,文件名首字母不能为数字

Mistake2:文件名中有空格,错误

Mistake3:总线的命名错误,多了一个点

Mistake4:总线的命名错误,少了一个点

Mistake5:总线的命名错误,大括号应该改为中括号

Mistake6:输出端的连线没有设置为总线的格式

Mistake7:q[3]没有命名

Mistake8:在74390芯片位置重叠放置了两个芯片(真的坑,找了好久)

Mistake9:没有输入时钟信号端

Mistake10:q[0]到q[3]没有命名到线路上,所以颜色不对(不信可以移动一下线路试试看)

Mistake11:输出端命名错误应该为q[3。。0](用句号代替点号了,不知道为什么打不出来)

Mistake12:q[2]被命名为了p[2]端点

Mistake13:文件命名错误,首字母不能为数字

Mistake14:选用的不是74390芯片(这个)

Mistake15:1CLK的命名首字母不能有数字+QA,QB不小心连在一起了

Mistake16:芯片的命名insit2于其他的重名了

工程文件下载连接

链接:https://pan.baidu.com/s/1Povko2ABq8P-DHPH1XzmIw

提取码:2021