1 引言

第四章存储器管理的最后两节内容,同时是本章内容的重点。

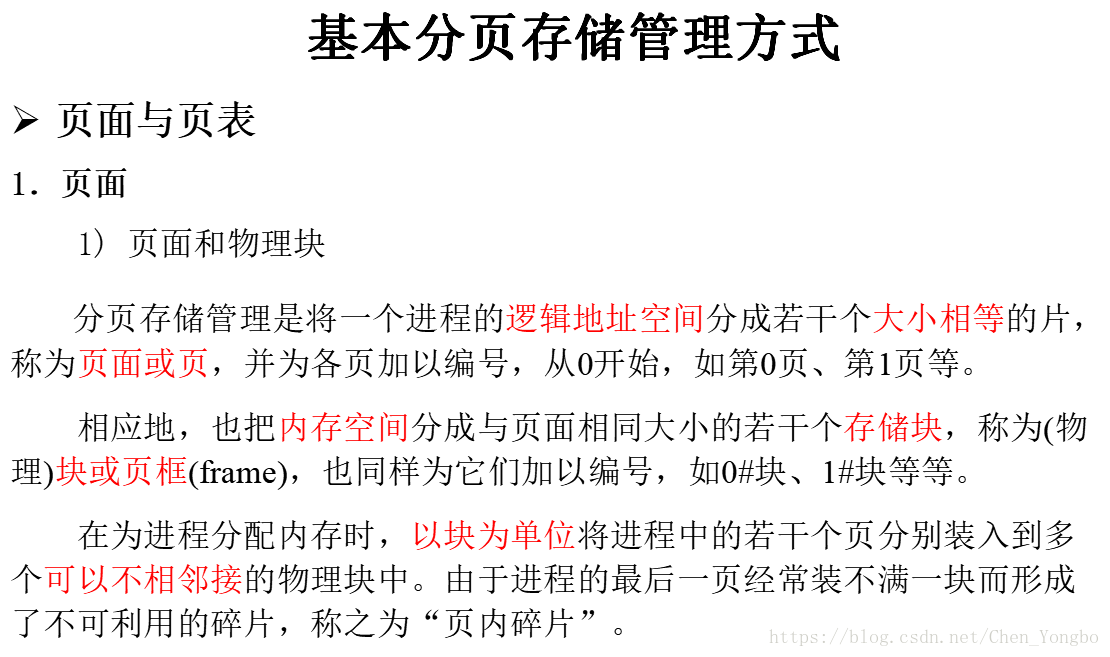

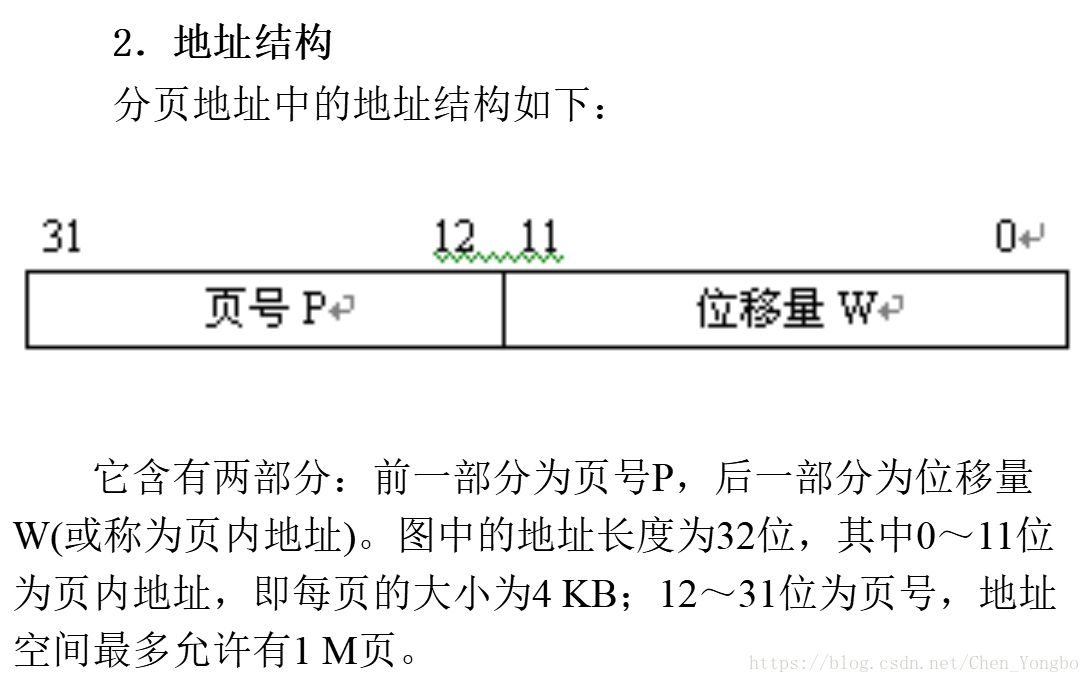

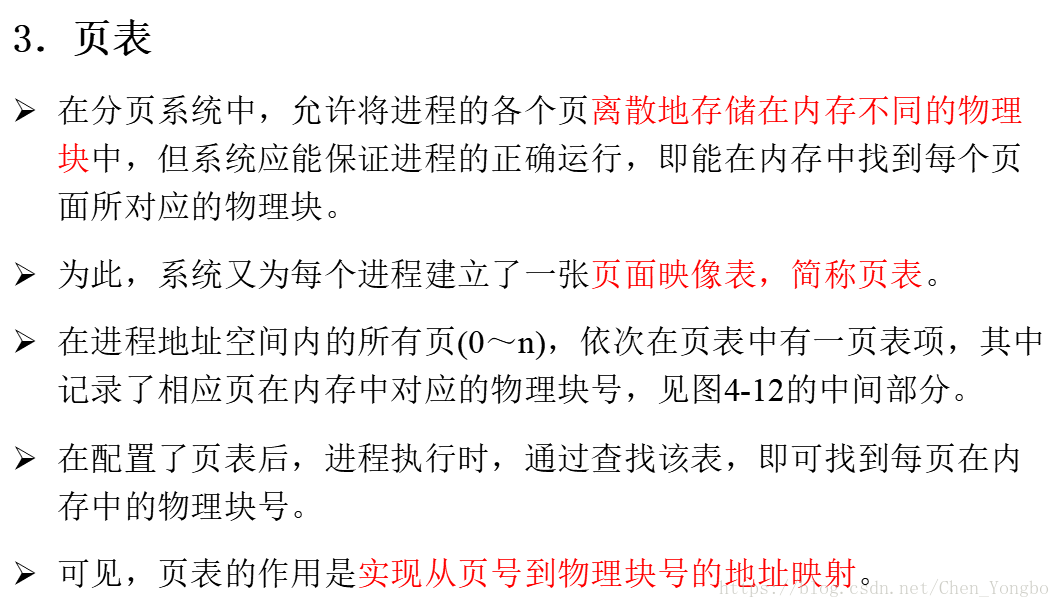

2 基本分页存储管理方式

3 基本分段存储管理方式

2.段表

在前面所介绍的动态分区分配方式中,系统为整个进程分配一个连续的内存空间。

而在分段式存储管理系统中,则是为每个分段分配一个连续的分区。

而进程中的各个段可以离散地移入内存中不同的分区中。为使程序能正常运行,亦即,能从物理内存中找出每个逻辑段所对应的位置,应像分页系统那样,在系统中为每个进程建立一张段映射表,简称“段表”。

每个段在表中占有一个表项,其中记录了该段在内存中的起始地址(又称为“基址”)和段的长度。

段表可以存放在一组寄存器中,这样有利于提高地址转换速度,但更常见的是将段表放在内存中。

3.地址变换机构

为了实现从进程的逻辑地址到物理地址的变换功能,在系统中设置了段表寄存器,用于存放段表始址和段表长度TL。

在进行地址变换时,系统将逻辑地址中的段号与段表长度TL进行比较。若S>TL,表示段号太大,是访问越界,于是产生越界中断信号;

若未越界,则根据段表的始址和该段的段号,计算出该段对应段表项的位置,从中读出该段在内存的起始地址,然后,再检查段内地址d是否超过该段的段长SL。若超过,即d>SL,同样发出越界中断信号;若未越界,则将该段的基址d与段内地址相加,即可得到要访问的内存物理地址。

像分页系统一样,当段表放在内存中时,每要访问一个数据,都须访问两次内存,从而极大地降低了计算机的速率。

解决的方法也和分页系统类似,再增设一个联想存储器,用于保存最近常用的段表项。

由于一般情况是段比页大,因而段表项的数目比页表项的数目少,其所需的联想存储器也相对较小,便可以显著地减少存取数据的时间,比起没有地址变换的常规存储器的存取速度来仅慢约10%~15%。

4.分页和分段的主要区别

由上所述不难看出,分页和分段系统有许多相似之处。比如,两者都采用离散分配方式,且都要通过地址映射机构来实现地址变换。但在概念上两者完全不同,主要表现在下述三个方面。

(1) 页是信息的物理单位,分页是为实现离散分配方式,以消减内存的外零头,提高内存的利用率。或者说,分页仅仅是由于系统管理的需要而不是用户的需要。段则是信息的逻辑单位,它含有一组其意义相对完整的信息。分段的目的是为了能更好地满足用户的需要。

(2) 页的大小固定且由系统决定,由系统把逻辑地址划分为页号和页内地址两部分,是由机器硬件实现的,因而在系统中只能有一种大小的页面;而段的长度却不固定,决定于用户所编写的程序,通常由编译程序在对源程序进行编译时,根据信息的性质来划分。

(3) 分页的作业地址空间是一维的,即单一的线性地址空间,程序员只需利用一个记忆符,即可表示一个地址;而分段的作业地址空间则是二维的,程序员在标识一个地址时,既需给出段名,又需给出段内地址。

4.6.3 信息共享

分段系统的一个突出优点,是易于实现段的共享,即允许若干个进程共享一个或多个分段,且对段的保护也十分简单易行。

在分页系统中,虽然也能实现程序和数据的共享,但远不如分段系统来得方便。

可重入代码(Reentrant Code)又称为“纯代码”(Pure Code),是一种允许多个进程同时访问的代码。

为使各个进程所执行的代码完全相同,绝对不允许可重入代码在执行中有任何改变。

因此,可重入代码是一种不允许任何进程对它进行修改的代码。

但事实上,大多数代码在执行时都可能有些改变,例如,用于控制程序执行次数的变量以及指针、信号量及数组等。

为此,在每个进程中,都必须配以局部数据区,把在执行中可能改变的部分拷贝到该数据区,这样,程序在执行时,只需对该数据区(属于该进程私有)中的内容进行修改,并不去改变共享的代码,这时的可共享代码即成为可重入码。

4.6.4 段页式存储管理方式

1.基本原理

段页式系统的基本原理,是分段和分页原理的结合。

即先将用户程序分成若干个段,再把每个段分成若干个页,并为每一个段赋予一个段名。

图4-21示出了一个作业地址空间的结构。该作业有三个段,页面大小为4 KB。

在段页式系统中,其地址结构由段号、段内页号及页内地址三部分所组成。

2.地址变换过程

在段页式系统中,为了便于实现地址变换,须配置一个段表寄存器,其中存放段表始址和段表长TL。

进行地址变换时,首先利用段号S,将它与段表长TL进行比较。若S<TL,表示未越界,于是利用段表始址和段号来求出该段所对应的段表项在段表中的位置,从中得到该段的页表始址,并利用逻辑地址中的段内页号P来获得对应页的页表项位置,从中读出该页所在的物理块号b,再利用块号b和页内地址来构成物理地址。

在段页式系统中,为了获得一条指令或数据,须三次访问内存。

第一次访问是访问内存中的段表,从中取得页表始址;

第二次访问是访问内存中的页表,从中取出该页所在的物理块号,并将该块号与页内地址一起形成指令或数据的物理地址;

第三次访问才是真正从第二次访问所得的地址中,取出指令或数据。

显然,这使访问内存的次数增加了近两倍。为了提高执行速度,在地址变换机构中增设一个高速缓冲寄存器。每次访问它时,都须同时利用段号和页号去检索高速缓存,若找到匹配的表项,便可从中得到相应页的物理块号,用来与页内地址一起形成物理地址;若未找到匹配表项,则仍须再三次访问内存。

4 结束语

又出现了BUG,不能上传图片。