关于Linux中Makefile 文件的使用

大学有阵子做嵌入式的时候觉得Makefile简直高不可攀~~

教程大多数都在试图把许多细节都讲清楚~~没有跟教程死磕3天的劲头真的不容易搞懂Makefile

而且写Makefile需要一点点gcc编译器的储备知识。对于在linux上刚上手的开发者的确有点绕。

所以我在这里做了个最简版的Makefile,看懂这个,你大体能知道Makefile该怎么写~~~~其他细节,只能“大行不顾细谨”了

从这里下载Makefile最简版本:

http://download.csdn.net/detail/sera_ph/7111665

里面的文件为 DandL.txt Makefile outlib.c outlib.h testmake.c

其中main函数位于testmake.c中

testmake.c 中调用了由outlib.h声明outlib.c定义的一个函数。

使用gcc将这个最简单的工程编译链接的shell命令,在DandL.txt中

gcc -c 的意思是将(.c文件)源文件编译,生成目标文件(.o文件)~~(源文件的#include预处理就能找到对应的头文件(.h文件))

gcc 目标文件 -o testmake的意思是将目标文件链接,生成可执行文件。testmake是可执行文件的名字。

这些就是你需要知道的gcc储备知识

Makefile就是针对这3个代码文件的最简版本

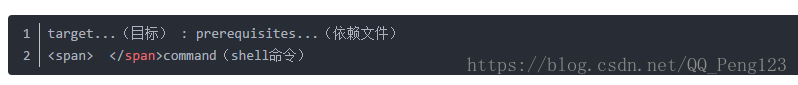

Makefile的基本语法如下:

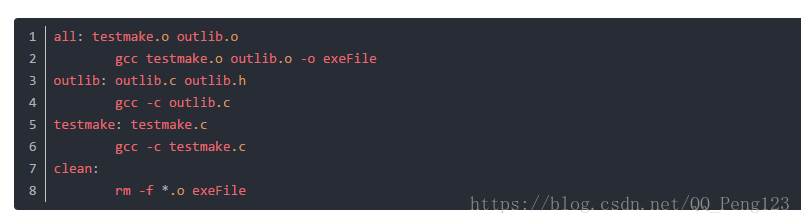

这些通过我写的Makefile很容易理解:

很明显,我们能看到,这个Makefile包含4个基本语句。

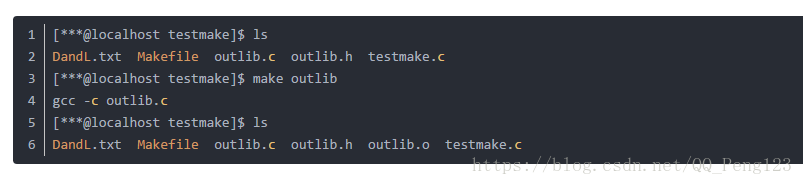

当在当前文件夹下,输入make outlib时,就相当于执行target为outlib的那语句的command

执行结果如下:

其中,make all和make clean是Makefile最常用的功能,一般要注意检查一下。

当你掌握这些~你已经出师可以自己写Makefile~当然,还有许多高端的技巧等你学习探索。

此篇文章转载一位大佬的文章,感觉写的还是比较深刻的。