常用的6个函数,结构体:

-

USART 初始化结构体(USART_InitTypeDef)

-

USART 时钟初始化结构体(USART_ClockInitTypeDef)

-

串口使能函数void USART_Cmd(USART_TypeDef* USARTx, FunctionalState NewState)

-

数据发送函数void USART_SendData(USART_TypeDef* USARTx, uint16_t Data)

-

数据接收函数uint16_t USART_ReceiveData(USART_TypeDef* USARTx)

-

中断状态位获取函数ITStatus USART_GetITStatus(USART_TypeDef* USARTx, uint16_t USART_IT)

USART 初始化结构体(USART_InitTypeDef)

初始化结构体定义在 stm32f10x_usart.h 文件中,初始化库函数定义在 stm32f10x_usart.c 文件中,编程时我们可以结合这两个文件内注释使用。

typedef struct { uint32_t USART_BaudRate; // 波特率 uint16_t USART_WordLength; // 字长 uint16_t USART_StopBits; // 停止位 uint16_t USART_Parity; // 校验位 uint16_t USART_Mode; // USART 模式 uint16_t USART_HardwareFlowControl; // 硬件流控制 } USART_InitTypeDef;

结构体成员:

1) USART_BaudRate:波特率设置。一般设置为 2400、9600、19200、115200。标准库函数会根据设定值计算得到 USARTDIV 值,从而设置 USART_BRR 寄存器值。

2) USART_WordLength:数据帧字长,可选 8 位或 9 位。它设定 USART_CR1 寄存器的 M 位的值。如果没有使能奇偶校验控制,一般使用 8 数据位;如果使能了奇偶校验则一般设置为 9 数据位。

3) USART_StopBits:停止位设置,可选 0.5 个、1 个、1.5 个和 2 个停止位,它设定 USART_CR2 寄存器的 STOP[1:0]位的值,一般我们选择 1 个停止位。

4) USART_Parity : 奇 偶 校 验 控 制 选 择 , 可 选 USART_Parity_No( 无校验 ) 、 USART_Parity_Even( 偶校验 ) 以 及 USART_Parity_Odd( 奇 校 验 ) , 它 设 定 USART_CR1 寄存器的 PCE 位和 PS 位的值。

5) USART_Mode:USART 模式选择,有 USART_Mode_Rx 和 USART_Mode_Tx,允许使用逻辑或运算选择两个,它设定 USART_CR1 寄存器的 RE 位和 TE 位。

6) USART_HardwareFlowControl:硬件流控制选择,只有在硬件流控制模式才有效,可选有⑴使能 RTS、⑵使能 CTS、⑶同时使能 RTS 和 CTS、⑷不使能硬件流。

USART 时钟初始化结构体(USART_ClockInitTypeDef)

使用同步模式时需要配置 SCLK 引脚输出脉冲的属性,标准库使用一个时钟初始化结构体 USART_ClockInitTypeDef 来设置,该结构体内容也只有在同步模式才需要设置。

typedef struct { uint16_t USART_Clock; // 时钟使能控制 uint16_t USART_CPOL; // 时钟极性 uint16_t USART_CPHA; // 时钟相位 uint16_t USART_LastBit; // 最尾位时钟脉冲 } USART_ClockInitTypeDef;

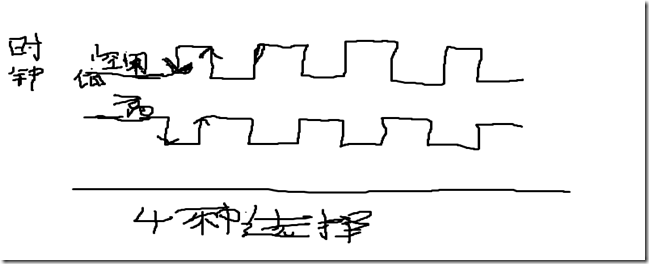

极性和相位是配合这使用:极性表示串口空闲时候是高电平还是低电平,相位指的是第一个边缘采集数据还是第二个边缘采集数据.

结构体成员:

1) USART_Clock:同步模式下 SCLK 引脚上时钟输出使能控制,可选禁止时钟输出 (USART_Clock_Disable)或开启时钟输出(USART_Clock_Enable);如果使用同步模式发送,一般都需要开启时钟。它设定 USART_CR2 寄存器的 CLKEN 位的值。

2) USART_CPOL:同步模式下 SCLK 引脚上输出时钟极性设置,可设置在空闲时 SCLK 引脚为低电平(USART_CPOL_Low)或高电平(USART_CPOL_High)。它设定 USART_CR2 寄存器的 CPOL 位的值。

3) USART_CPHA:同步模式下 SCLK 引脚上输出时钟相位设置,可设置在时钟第一个变化沿捕获数据(USART_CPHA_1Edge)或在时钟第二个变化沿捕获数据。它设定 USART_CR2 寄存器的 CPHA 位的值。USART_CPHA 与 USART_CPOL 配合使用可以获得多种模式时钟关系。

4) USART_LastBit:选择在发送最后一个数据位的时候时钟脉冲是否在 SCLK 引脚输 出 , 可 以 是 不 输 出 脉 冲 (USART_LastBit_Disable) 、 输 出 脉 冲 (USART_LastBit_Enable)。它设定 USART_CR2 寄存器的 LBCL 位的值。

串口使能函数

void USART_Cmd(USART_TypeDef* USARTx, FunctionalState NewState)

数据发送函数

void USART_SendData(USART_TypeDef* USARTx, uint16_t Data)

数据接收函数

uint16_t USART_ReceiveData(USART_TypeDef* USARTx)

中断状态位获取函数

ITStatus USART_GetITStatus(USART_TypeDef* USARTx, uint16_t USART_IT)