前言:由于引起芯片发生故障的制造缺陷原因多种多样,为了便于分析和判断故障,需要将故障的特征进行抽象和分类,把呈现同样效果的故障归并成同一种故障类型,并使用同一种描述方法,这种故障描述方式称为故障模型。当前VLSI 设计中常用的故障模型:固定型故障模型(stuck-at fault model)、时延故障模型(delay fault model) 和基于电流的故障模型(current-based fault model)

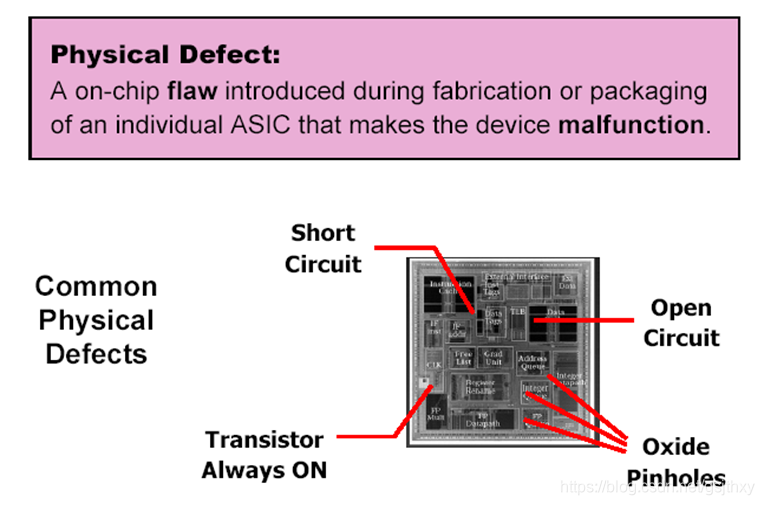

一、What is a Physical Defect?

二、CMOS 工艺中常见的制造缺陷或曰物理缺陷对地和对电源的短路

- 对地和对电源的短路

- 由尘埃引起的连线断路

- 金属穿通引(Metal Spike-through)体管源或漏的短路

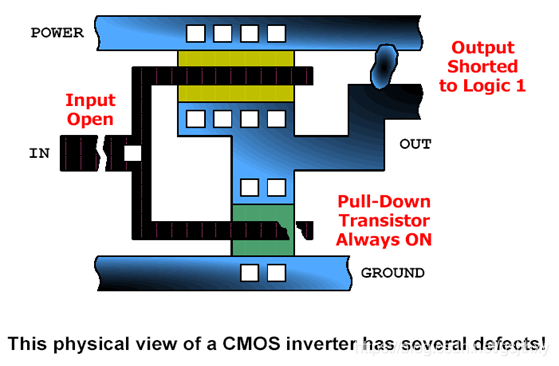

三、Physical Defects à Fault Model

- 不管是对封装好的成品还是对尚未封装的“裸片”(die),要将探针伸入芯片结构内部进行测试,无论从技术或是经济角度都是根本不可行的。对芯片的测试只有通过有限的输入/输出管脚(I/O pin) 来完成。

- 需要通过对芯片内部制造缺陷引起的电路故障建立逻辑上的模型,从而通过测量电路在输入输出管脚上行为,来判断芯片内部是否存在制造缺陷Physical Defects(制造缺陷) à Fault Model(故障模型)

四、Fault Model(故障模型)

1、固定型故障模型(stuck-at fault model),如下图所示:

2、时延故障模型(delay fault model) ,如下图所示:

3、基于电流的故障模型(current-based fault model),如下图所示:

常见的两类基于电流的故障模型:

(1)pseudo-stuck-at 故障模型:主要建立在SA 故障模型上:在单纯的SA模型中,观察代表逻辑值1 或者0 的电压值;而 在pseudo-stuck-at 故障模型中,则是先将故障效应加到指定点,然后观察电源对整个芯片输出的电流大小。

(2)Toggle故障模型

五、:Propagate Fault Effect