5G通信、硬件加速技术已经成为现代通信技术的重要研究对象,在科研、技术应用等方面都发挥着举足轻重的作用,全球范围内都在关注和研究此问题。

在2019年末,我在寻找毕业设计题目的时候,无意间发现此技术方案和IDEA,给了我很大的兴趣,通过竞赛的方式提出了现在前沿的技术发展方向。因此,本篇文章主要分享研究的idea,同时也给出了大量的参考资料和国内外重要的文献。

在此呼吁,对此问题感兴趣的可以联系我,寻找共同学习的伙伴。

张伟,扬州大学16级电子信息和商务英语双学位,在校期间获得国省级奖项26项,申请专利4项,软件著作权7项,两篇SCI论文在投,全国FPGA设计大赛二等奖,中国高校机器人大赛二等奖。

- Wei Zhang. “A Survey of FPGA Based CNNs Accelerators”. SCI: Chinese Journal of Electronics (CJE). (Under reviewed)

- Wei Zhang. “A Design of 3D Dynamic Display System Based on Voice Control”. Chinese Journal of Electron Devices. (Under reviewed)

- Kaige Gao, Wei Zhang, Chunlin Liu, et al. “Strain induced ferroelectric and pyroelectric in (4-(Aminomethyl)pyridinium)2MnCl4•2H2O”. SCI: Journal of Crystal Growth.(Under reviewed)

- Xiaoying Den, Wei Zhang, Xiaofeng Yang, Weifeng Chen. A Webcam Embedded with Real-time Environment Information [P]. CN209608763U, 2019-11-08.

- Xiaofeng Yang, Wei Zhang, Xiaoying Deng, Weifeng Chen, et al. A Reading-aid Device for the Bling Based on Raspberry Pi [P]. CN209281692U, 2019-08-20.

- Zijia Wang, Wei Zhang, Xiaofeng Yang, Wei Wang, et al. A System for All-purpose Campus Card United with Business Member Based on IOT and RFID Technology [P]. CN208722234U, 2019-04-09.

下文中的赛题背景和设计思路提示来源于IEEE杯竞赛官网,如若侵权,联系即删。

IEEE杯 赛题背景介绍和设计思路提示

1. 赛题背景

自LTE(可以称为准4G)以来,为了提高载波的单位频宽数据传输率,多采用OFDM与QAM调制方式,但带来的问题是经调制后的信号波形PAPR(峰值对平均值的功率比: Peak-to-Average Power Ratio)高,在LTE中,典型值为6.7dB。这造成了通常的功放(PA)平均能量转换效率非常低。为了解决这个问题,一种常用的方法是被称为包络跟踪(Envelope Tracking,即ET)的PA,这是在1952年Kahn [6]提出的EER (Envelope Elimination Restoration)方法上稍加改进得到的,其主要的特征是让PA的供电电源电压随输入信号的幅度包络而变化(即跟踪)。

(1) 5G通信特征:三大应用场景

(2) 5G NR (New Radio) 载波频段:1 – 100GHz

2. 设计思路提示

(1) 参考文献[^1](港科大2017年ISSCC文章)

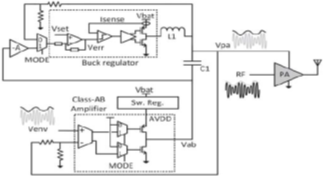

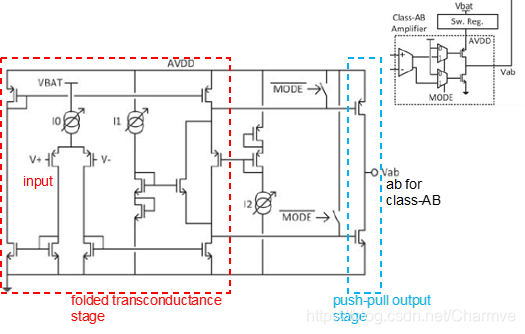

(2) 在ET电路中需要用到线性PA,该工作采用一个高效率的电源电压调制器(supply modulator)与一个全集成的CMOS PA。

(3) 模式开关(mode-switching)PA

线性工作区(低输出功率,固定电源电压)

开关工作区(高输出功率)

(4) 电源电压调制器由两个放大器组成

线性放大器(放大高频率信号)

开关放大器(25MHz,3电平,2.4V),低频信号

(5) AC耦合电路将两路放大器的输出合成

3. 参考文献和补充知识点

(1) 港科大2017年ISSCC文章解读:电源电压调制器 (Supply Modulator)

(2) Mode-Switching PA

(3) 港科大同一组的先前工作介绍

Xun Liu, Cheng Huang, and Philip K. T. Mok, “A 50MHz 5V 3W 90% Efficiency 3-Level Buck Converter with Real-Time Calibration and Wide Output Range for Fast-DVS in 65nm CMOS,” VLSI Circuits, 2016.

(4) Block Diagram of EER-PA as First Proposed

L. R. Kahn, Proc. IRE, 1952 (EER: Envelope Elimination & Restoration)

(5) Practical Block Diagram (Kahn cont’d)

(6) EER Block Diagram

(7) Previous Work by M. Hassan of UCSD

Muhammad Hassan1 , Peter M. Asbeck1 , Lawrence E. Larson (UCSD), “A CMOS Dual-Switching Power-Supply Modulator with 8% Efficiency Improvement for 20MHz LTE Envelope Tracking RF Power Amplifiers,” ISSCC 2013, p. 366.

To evaluate the performance with an RF power amplifier, a commercially available two-stage GaAs HBT PA is used. The performance of the ET power amplifier is measured using a 20MHz LTE signal at 2.535GHz. For test purposes, the envelope signal as well as I and Q baseband signals are generated in the digital domain.

(8) 参考文献

-

a) X. Liu, et al. (香港科技大学), “A 2.4V 23.9dBm 35.7%-PAE -32.1dBc-ACLR LTE-20MHz Envelope-Shaping-and-Tracking System with a Multiloop-Controlled AC-Coupling Supply Modulator and a Mode-Switching PA,” ISSCC, pp. 38-39, Feb. 2017.

-

b) C. Ho, et al. (联发科), “An 87.1% Efficiency RF-PA Envelope-Tracking Modulator for 80MHz LTE-Advanced Transmitter and 31dBm PA Output Power for HPUE in 0.153μm CMOS,” ISSCC, pp. 431-433, Feb. 2018.

-

c) P. Riehl, et al. (联发科), “An AC-Coupled Hybrid Envelope Modulator for HSUPA Transmitters with 80% Modulator Efficiency, ISSCC, pp. 364-3366, Feb. 2013.

-

d) Behzad Razavi, RF Microelectronics, 2nd ed., Prentice Hall, 2011.

Ch. 12 Power Amplifiers, 12.7 Polar Modulation (pp. 790-802) -

e) Thomas Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed., Cambridge University Press, 2004. (中译本,CMOS射频集成电路设计,第二版,电子工业出版社,2006)

Ch. 15 RF Power Amplifiers, 15.7 Modulation of Power Amplifiers (pp. 512-540) -

f) Leonard R. Kahn, “Single-Sideband Transmission by Envelope Elimination and Restoration,” IEEE Proc. IRE. p. 803, 1952.

-

g) D. Su and W. McFarland, “An IC for Linearizing RF Power Amplifiers Using Envelope Elimination and Restoration,” IEEE JSSC, Vol. 33, No. 12, p. 2252, Dec. 1998

(9) 补充参考要点

- a) There is considerable interest in applying envelope tracking to CMOS RF power devices.

- b) CMOS power amplifiers have been a poor choice for modern high PAR modulation techniques because they have inherently poor linearity, which requires them to be backed off to reduce distortion.

- c) When CMOS amplifiers operate at higher RF power levels, distortion clips the peaks of the waveforms.

- d) Devices using Nujira’s technique have achieved high efficiency with equal performance in other areas to that of GaAs

(10) Evolution of Kahn’s EER (Envelope Elimination & Restoration)

- a) The original technique introduced by Kahn was dubbed envelope elimination and restoration for its use of an analog envelope detector and a limiter to eliminate the envelope from the input signal, and later restore it at the output by varying the PA’s supply voltage.

- b) With advancements in digital technology, envelope detector and limiter have been replaced by a digital signal processor (DSP), which generates amplitude and phase waveforms from the in-phase/quadrature (I/Q) input signals.

- c) From Ph.D. thesis of F. Pavlo, Georgia Tech, 2009

(11) ET vs. EER

- a) To overcome this issue, envelope tracking (ET) technique is used. As in EER amplifiers, ET modulates the drain of the PA, however now the RF signal in the phase path is not hard-limited, but rather has full amplitude modulation.

- b) A linear RF PA is then used for amplification, while its supply voltage follows the modulated waveform.

- c) While envelope tracking amplifiers are easier to implement than their EER counterparts, they provide smaller efficiency benefits.

(12) AC-Coupled Class-AB & Buck Converter Envelope Tracking P. Riehl of MediaTek, ISSCC ‘13

(13) Class AB PA in Riehl’s

(14) Circuitry for Envelope Detector

Razavi’s book on RF Microelectronics 2nd ed. (Figs. 12.45)

题目官方链接:http://univ.ciciec.com/col.jsp?id=162

4. 杯赛题目

题目1:面向4G/5G通信的高能效CMOS功率放大器设计

参赛要求: 本科生组/无限制组

赛题内容:

本赛题是5G通信CMOS射频前端电路系列设计之三(前二题分别是2017年的宽带LNA设计与2018年的覆盖28/39GHz的PLL设计),主题是采用包络跟踪(Envelope Tracking)电路程式的射频功率放大器(PA)设计,强调的性能指标为满足一定的射频信号功率输出条件下,尽可能地提高能量转换效率(PAE:power added efficiency)。

设计要求及指标:

- 采用65nm CMOS工艺(及相应的PDK)

- 射频载波频率为LTE Band 41的2.535GHz,带宽20MHz,调制方式16QAM,包络信号与基带I/Q信号由数字电路产生(参考Muhammad Hassan, Peter M. Asbeck, Lawrence E. Larson (UCSD), “A CMOS Dual-Switching Power-Supply Modulator with 8% Efficiency Improvement for 20MHz LTE Envelope Tracking RF Power Amplifiers,” ISSCC 2013, p. 366.)

- 不采用包络跟踪(ET),同时能达到同样输出功率和能效的其他结构和方案亦可。但网表必须是晶体管级别的,也应当采用65nm工艺。

- 包括跟踪部分的电路,如果不能做到晶体管级别,可采用行为级模型代替并实现混合仿真。行为级模型要说明如何校准和补偿结果的正确性。

- 输出信号功率要求不低于23dBm,PAE>35%,给出ACLR (Adjacent Channel Leakage Ratio),Vdd=2.4V(建议电压)

- 以上结果可以从整个系统电路的前仿得到,器件/元件模型由PDK得到。

作品提交:

- 模拟工具建议采用Cadence SpectraRF Workshop,特别是其中的ENVLP(指envelope)与ACPR(指邻近信道功率比)的软件程序来进行分析与设计验证。

- 提交完整设计文档和设计数据,包括电路/系统设计分析

评分规则: - 网表(netlist)设计与模拟,包括文档说明:70分

- 模拟结果(前仿)及分析:25分

- 文献调研与评价: 5分

- 说明:相同设计结果的情况下,晶体管级别的设计评分应当优于行为级模型的设计。

(总计:100分)

注意事项

- 参加企业命题杯赛的作品,杯赛出题企业有权在同等条件下优先购买参加本企业杯赛及单项奖获奖团队作品的知识产权。

- 大赛组委会对参赛作品的提交材料拥有使用权和展示权。

题目2:Arm 片上系统设计挑战赛

参赛要求: 本科生组/无限制组

赛题内容:

利用Arm Cortex-M3 DesignStart处理器在可编程逻辑平台上构建片上系统,实现图像采集,图像处理和人机交互功能,观察并优化系统的性能。

使用ArmCortex-M3 DesignStart Eval提供的处理器IP,在你的可编程逻辑平台上构建简单的Cortex-M3片上系统。

系统应至少包含:

- ArmCortex-M3 DesignStart处理器;

- 利用片上或板上资源实现的ROM与RAM;

- 与芯片外部引脚连接的GPIO外设。

- 使用KeilμVision工具编写并生成软件程序,实现GPIO输出引脚跟随GPIO输入引脚变化。将对应的输入、输出引脚连接至板上开关与LED,确认程序正确运行。

如上图,在FPGA中编写图像传感器的接口和数据缓存,作为Cortex-M3片上系统的一个外设,并编写软件程序,将图像传感器的采集结果显示在开发平台自带的液晶屏上。

在Cortex-M3上编写软件程序,识别摄像头拍摄到的车牌中的5位数字并显示在LCD屏上。可以在FPGA中设计硬件加速器,帮助Cortex-M3加快图像识别的速度。

利用以上实现的系统,进行20张图像识别挑战赛:

- 测试图片由“模型车牌生成器”生成;参赛队自制20张不同的车牌,保持原大小复制到白底Power Point中,每页一张。模型车牌由XX.YYYYY组成,其中YYYYY为5位纯数字,此次识别就仅限于这个5个数字。

- 测试时,启动PPT演示计时功能,摄像头拍摄屏幕上的“模型车牌”(拍摄位置由参赛队自由选择),识别并在LCD屏上显示其中的5位数字,同时给出识别完成信号(蜂鸣或亮灯),人工切换到下一张测试,所有测试完成后计时停止。计时停止后,参赛队在LCD屏上显示所有识别结果供裁判核对正确率。

- 最终得分以速度排序,时间越短的参赛队成绩越好。但识别错误3张以上取消比赛成绩。在3张错误以内,每错一张时间罚5秒。

设计报告:

- 作品展板(团队介绍、项目心得体会、项目研发情况、技术创新点、后续工作)

- 作品PPT(团队介绍、项目心得体会、项目研发情况、技术创新点、后续工作)

- 系统设计方案

- 功能仿真及测试结果图

- 系统展示图片、或视频

- 设计数据:系统原理图、软硬件代码,仿真和测试结果;

评分规则:

| 内容 | 分值 | 评分要求 |

|---|---|---|

| 1. 完成Cortex-M3片上系统的基础设计 | 20分 | 1. 正确获得Arm Cortex-M3DesignStart Eval IP,正确使用内部总线连接存储器与外设; 2. 在硬件平台上实现系统,并正确编译、下载软件程序, 现场编程调试,通过按键改变LED等的闪烁方式或频率证实系统运行情况; |

| 2. 完成图像传感器芯片的数字接口设计,并作为与Cortex-M3片上系统的外设 | 20分 | 1. 详实规范的设计文档 2. 编写软件成功实现图像采集; 3. 数字接口设计的功能仿真结果等可视化成果; |

| 3. 图像识别算法的实现 | 30分 | 1. 图像识别算法的详实设计方案 2. 图像处理协处理器的功能仿真结果等可视化成果 |

| 4. 现场演示 | 30分 | 1. 现场演示图像识别功能 2. 追求更高的识别正确率和速度 |

本题目可选用MPS2开发,但不限于此平台,队伍可自行选择使用类似的硬件平台开发。但所使用板卡的官方售价不得高于MPS2,且FPGA主芯片限于Altera的Cyclone、Max系列,和Xilinx的Spartan、Artix系列。不得采用其他中高端系列FPGA芯片。

关注微信公众号:迈微电子研发社,获取更多精彩内容。

知识星球:社群旨在分享AI算法岗的秋招/春招准备攻略(含刷题)、面经和内推机会、学习路线、知识题库等。