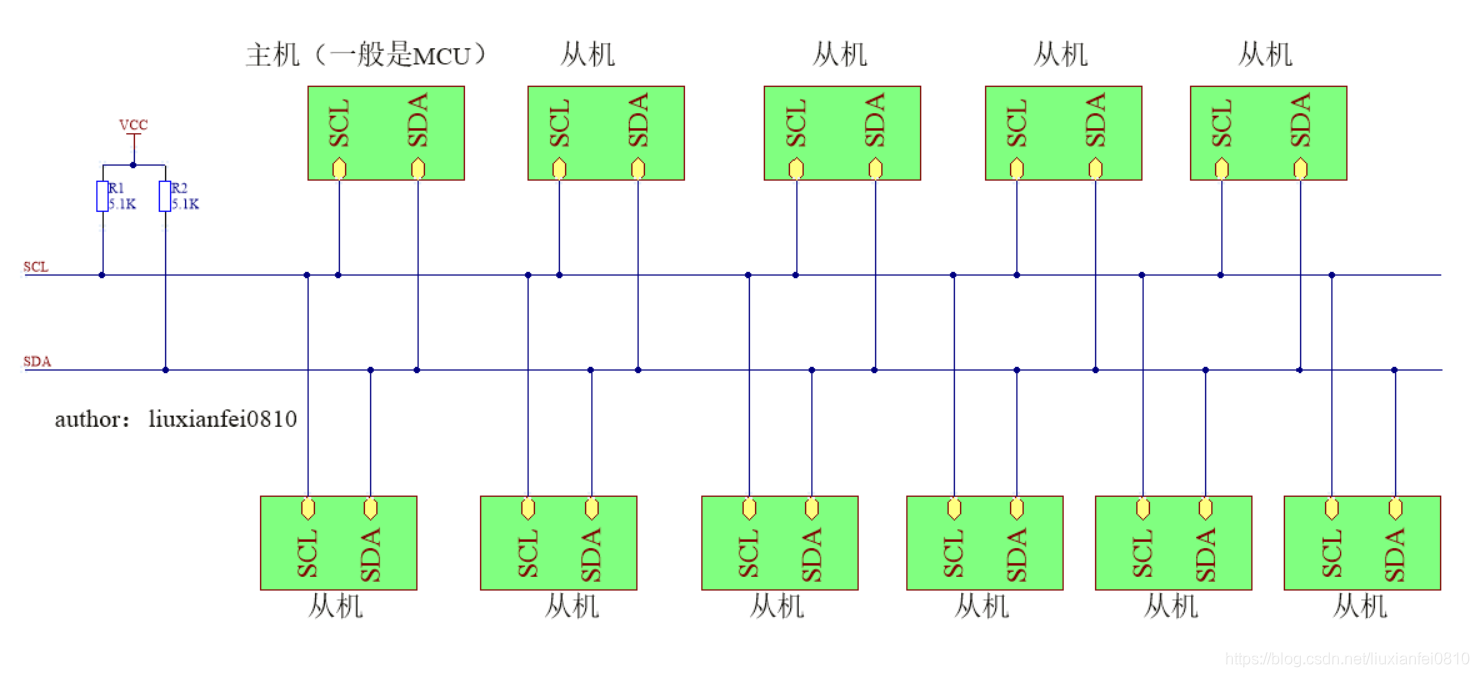

一,IIC串行总线系统基本结构如下图:

备注:标准IIC普通模式下,数据的传输速率为100kbps,高速模式下可达400kbps,总线扩展的器件数量是由电容负载确定,IIC总线上每一个节点器件的接口都有一定的等效电容,电容量越大,传输延迟越高。

二,IIC协议和24C02器件介绍

见此文:

IIC和24C02介绍

24C02实物图:

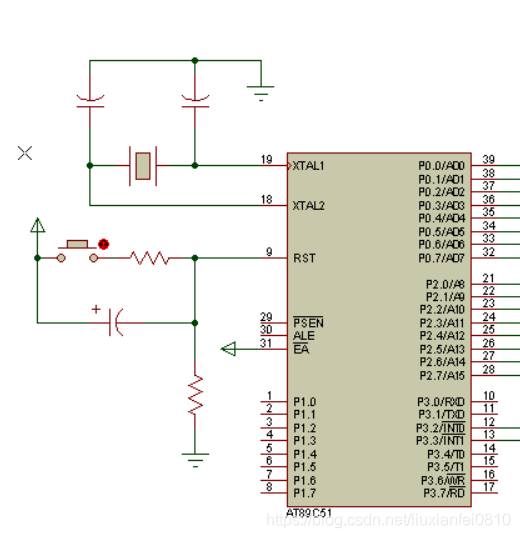

51单片机最小系统:原理图和实物图

(实际使用时,须在P0口外接上拉电阻)

3,24C02程序源码:

SDA BIT P2.4

SCL BIT P2.3

WORDADRR EQU 66H ;WORDADRR EQU 30H

DATEADDR EQU 66H

SLAVE_W EQU 0XA0

SLAVE_R EQU 0XA1

ORG 0000H

LJMP MAIN

ORG 0030H

MAIN:

MOV A,#SLAVE_W

MOV R7,#08H

MOV R1,#WORDADRR

LOOP:

MOV @R1,A

INC A

INC R1

DJNZ R7,LOOP

;赋值用于测试

LCALL WRITEDATA

MOV 72H,#100

Q3:

MOV 71H,#100

Q1:

MOV 70H,#47

Q0:

DJNZ 70H,Q0

NOP

DJNZ 71H,Q1

MOV 70H,#46

Q2:

DJNZ 70H,Q2

NOP

DJNZ 72H,Q3

MOV 70H,#48

Q4:

DJNZ 70H,Q4

;delay

ACALL READ_8

LJMP RETURN

WRITEDATA:

ACALL IICSTART ;8字节发送

MOV A,#SLAVE_W

ACALL IICSEND

ACALL ACK

JNB ACC.4 ,D1

LJMP ERR

D1:

MOV A,#WORDADRR

ACALL IICSEND

ACALL ACK

JNB ACC.4,D2

LJMP ERR

D2:

MOV R0,#DATEADDR

MOV R6,#08H

D4:

MOV A,@R0

ACALL IICSEND

ACALL ACK

JNB ACC.4,D3

LJMP ERR

D3:

INC R0

DJNZ R6,D4

ACALL STOP

RET

READ_8:

ACALL IICSTART ;序列读8字节

MOV A,#SLAVE_W ;从机地址+W

ACALL IICSEND

ACALL ACK

JNB ACC.4,D5

LJMP ERR

D5:

MOV A,#WORDADRR

ACALL IICSEND

ACALL ACK

JNB ACC.4,D6

LJMP ERR

D6:

ACALL IICSTART

MOV A,#SLAVE_R ;从机地址+R

ACALL IICSEND

ACALL ACK

JNB ACC.4,D7

LJMP ERR

D7:

MOV R0,#51H

MOV R6,#07H

D9:

ACALL RECIEVE

MOV @R0 ,A

ACALL DATA0ORACK

D8:

INC R0

DJNZ R6,D9

ACALL RECIEVE

MOV @R0,A

ACALL DAT1ORNACK

ACALL STOP

RET

IICSEND:

MOV R7,#08H

L0:

RLC A

JC L1

ACALL L0

AJMP L2

L1:

ACALL DAT1ORNACK

L2:

DJNZ R7,L0

RET

RECIEVE:

MOV R7,#08H

BACK1:

SETB SDA

SETB SCL

NOP

NOP

NOP

NOP

MOV C,SDA

RLC A

CLR SCL

DJNZ R7,BACK1

RET

IICSTART:

SETB SCL

SETB SDA

NOP

NOP

NOP

NOP

CLR SDA

NOP

NOP

NOP

NOP

CLR SCL

RET

STOP:

CLR SDA

SETB SCL

NOP

NOP

NOP

NOP

SETB SDA

NOP

NOP

NOP

NOP

NOP

CLR SCL

CLR SDA

RET

ACK:

SETB SCL

SETB SDA

NOP

NOP

NOP

NOP

NOP

MOV A,P2

JNB ACC.4,L4

AJMP ACK

L4:

CLR SCL

NOP

RET

DATA0ORACK:

CLR SDA

SETB SCL

NOP

NOP

NOP

NOP

CLR SCL

SETB SDA

RET

DAT1ORNACK:

SETB SDA

SETB SCL

NOP

NOP

NOP

NOP

CLR SCL

CLR SDA

RET

ERR:

AJMP RETURN

RETURN:

END