今天也是生草的一天啊wwww!

凑!

我从下午一点吃完饭拿到板子开始贴片,一直调到下午18点吃饭前才解决所有的问题。总结一下还是自己tooyoung没有什么调试USB外设的经验。

首先来介绍一下本项目。 大概在18年年底我们实验室量产过一批J-LINK OB。不用说这东西肯定是盗版的大家都明白。随着JLINK驱动版本的更新,在某个特定的时间或者是驱动版本往后我们的JLINK开始被识别出来是盗版的。仿真跑着跑着突然就disconnect了,十分操蛋。

这东西已经够垃圾的了,就不开源了。网上大佬这么多,发出来还要被喷hhh。不过这个也不是我画的,是以前学长画的。当时刚画完还有bug被我当场实锤。

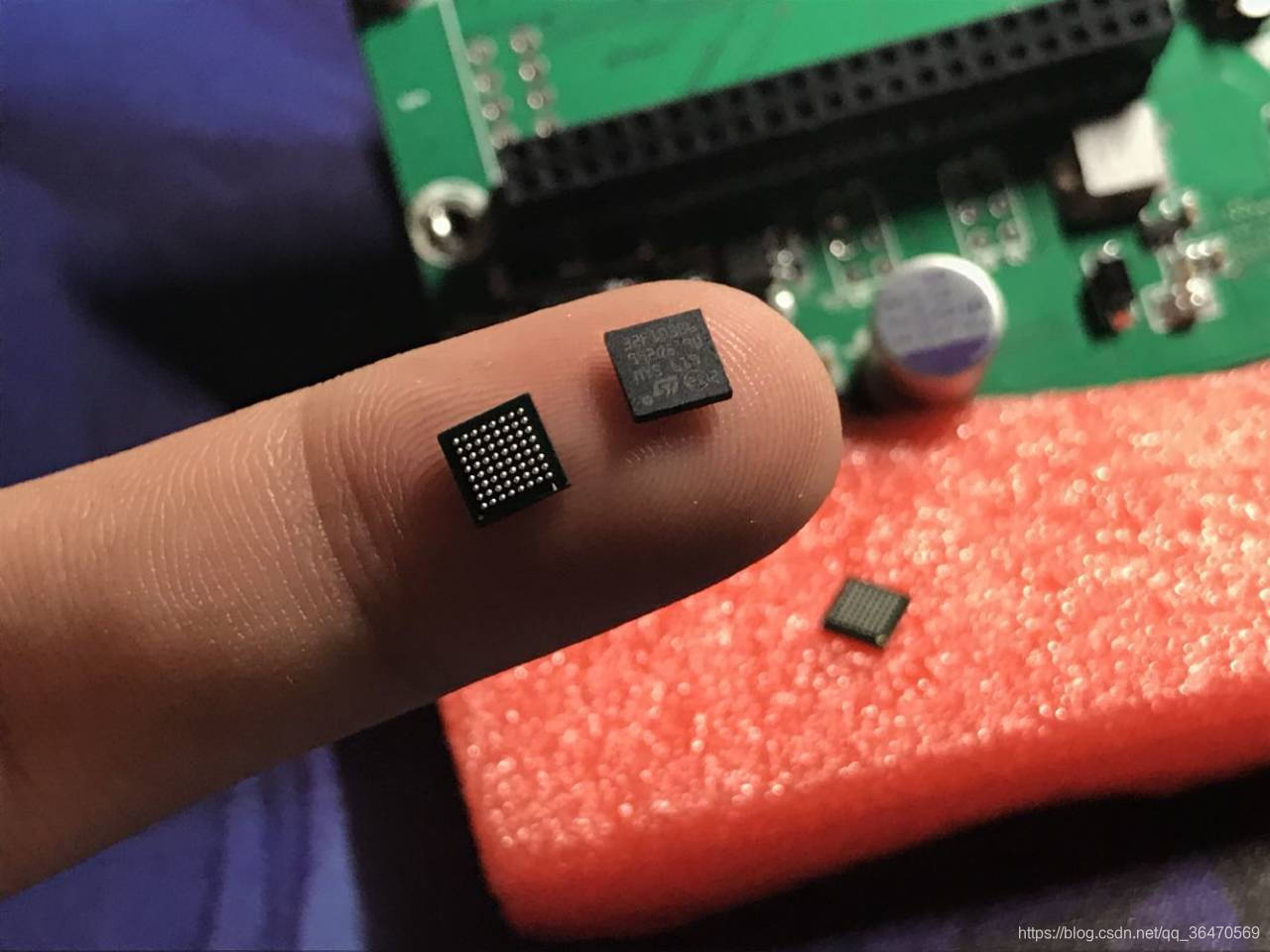

那仿真器好用的其实也就那几个,ST-LINK的话我想大家平时可能还要调其他的一些芯片,适用性就没那么广泛了,再加上ST-LINK仿真贼慢,肯定不会用那种东西的。虽然现在V3已经出了,但是那个STM32的主控(好像是H7?)那种东西是BGA封装的。焊接倒是没有什么大问题因为我们有回流焊机。但是PCB就是很大问题了。STM32个人感觉BGA的球特别特别小,它不像Xilinx系列之类的会使用0.5mm或者0.55mm的大球,STM32的那种球挺小的,我买过一批F103

我也不知道我为啥要买这种东西。。。具体有多小呢?

这个emmm,以后再说吧等能有本事稳定画出BGA板子,自然就会上这个了~

JLINK的话其实还有一种盗版的V9,但是貌似也有固件不稳定的问题?还有一些MagicProbe?

接着说DAP。

于是我的群(斯哈研究所)里的大佬们就行动起来,合作出一些好用的仿真器。于是我们就想到DAP了。跑到CSDN上拔了一堆文章出来,然后又是github上一顿猛搜,最终凑出来一个工程,是可以直接在keil编译的那种。

我是专攻硬件的,我也不懂固件是怎么实现的。。所以后面一些软件都会交给群里的其他一些朋友来写~

先做CMSIS-DAP,能做多小做多小。以前老学长还在的时候就喜欢把东西做的特别小。尤其是博文大佬!就是传说中杭电信工最强软件!

(我TT今天就是学长的小迷妹!)

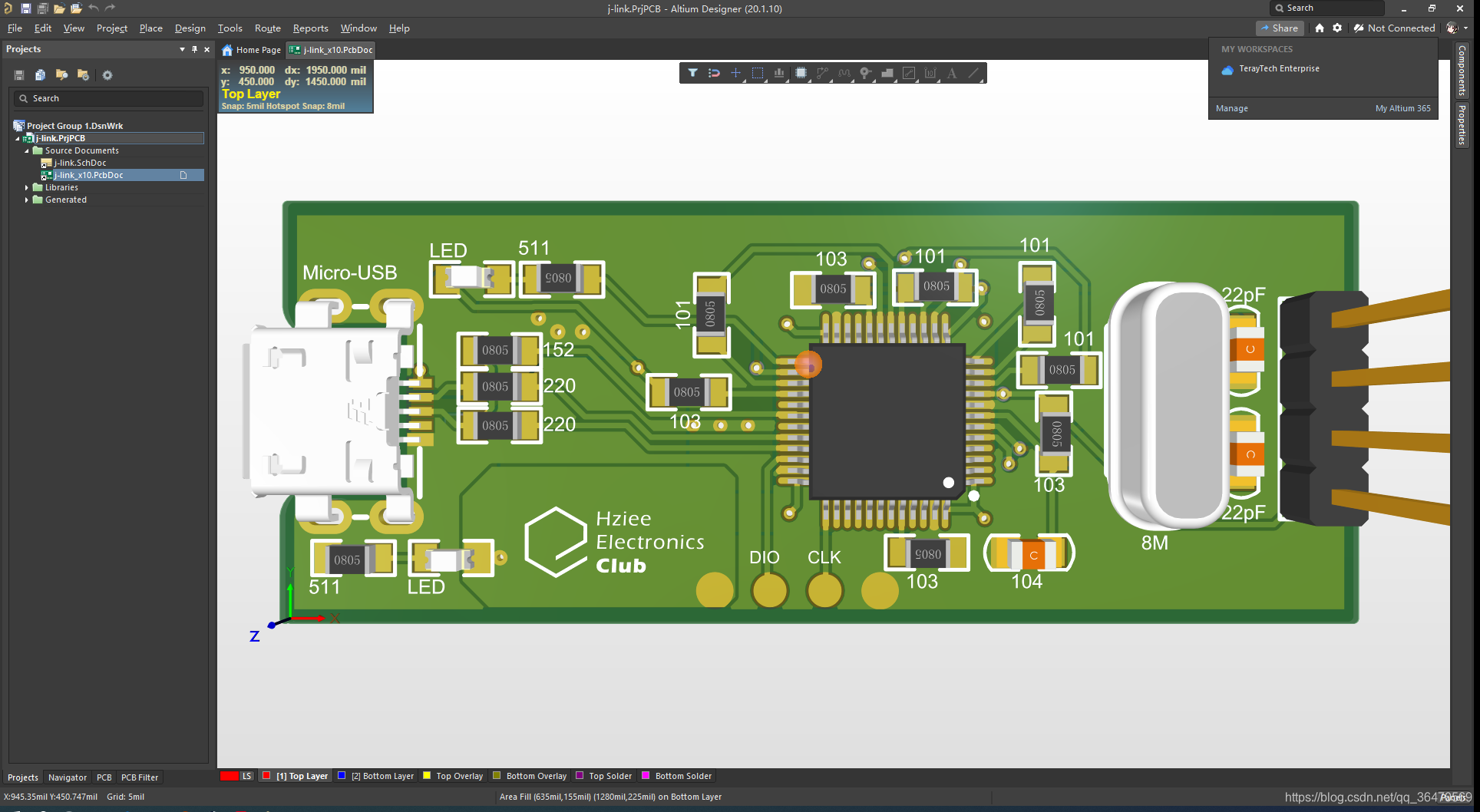

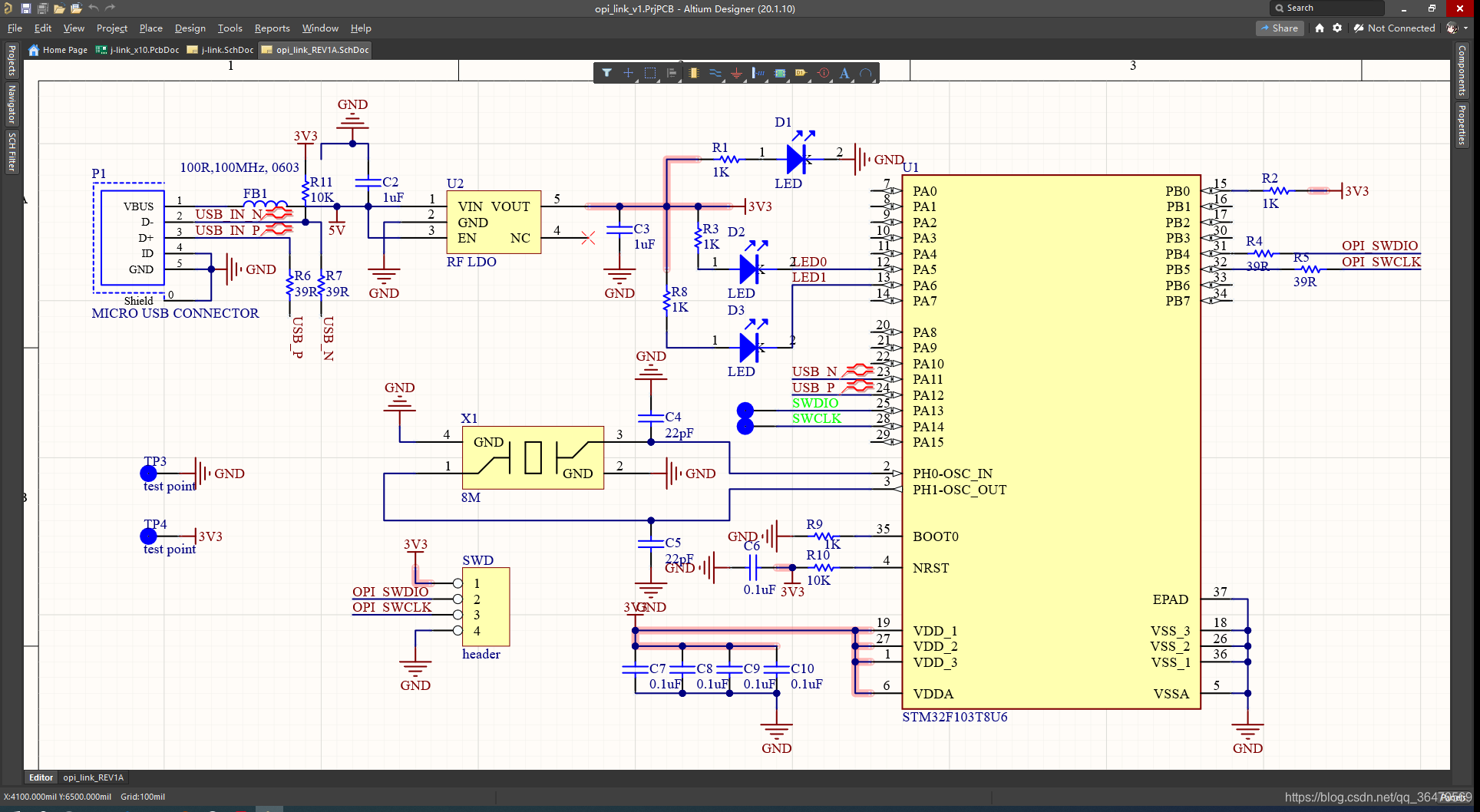

DAP的话,之前网上有dalao把项目从NXP平台(好像是KL20)给移植到STM32F1上去了,所以整个就变得特别简单了,硬件电路也没有什么东西的。直接上图

为了模仿学长,尽可能的把板子画的小,在这里我使用github上的dalao @konosubakonoakua使用的主控,因为看过来看过去果然还是这个比较合适hhh

起名字的话当时我在群里有问大家怎么看,好像也没什么特别靠谱的名字,于是我就自作主张了,就叫欧派link吧。hhhhh (Opi-Link)

如果你比较仔细,你应该已经发现这张图的USB画的其实是有问题的。就是这个问题让我debug了好几个小时。我一直以为是自己的焊接有问题,谁知道最后发现是USB D-的信号线被我给拉高了。。。

修改以后即正常。正式版的应该很快就发布到Github去。

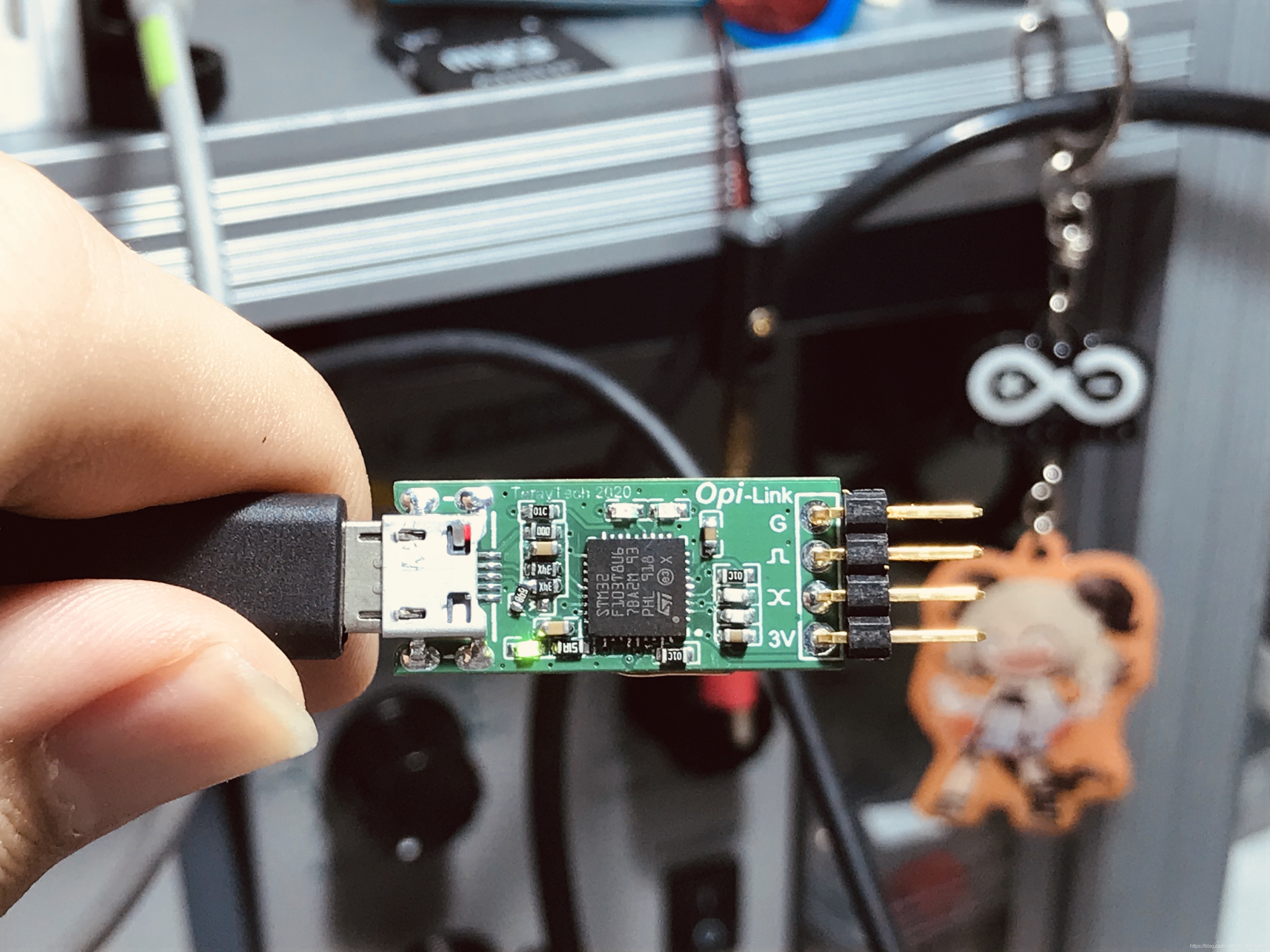

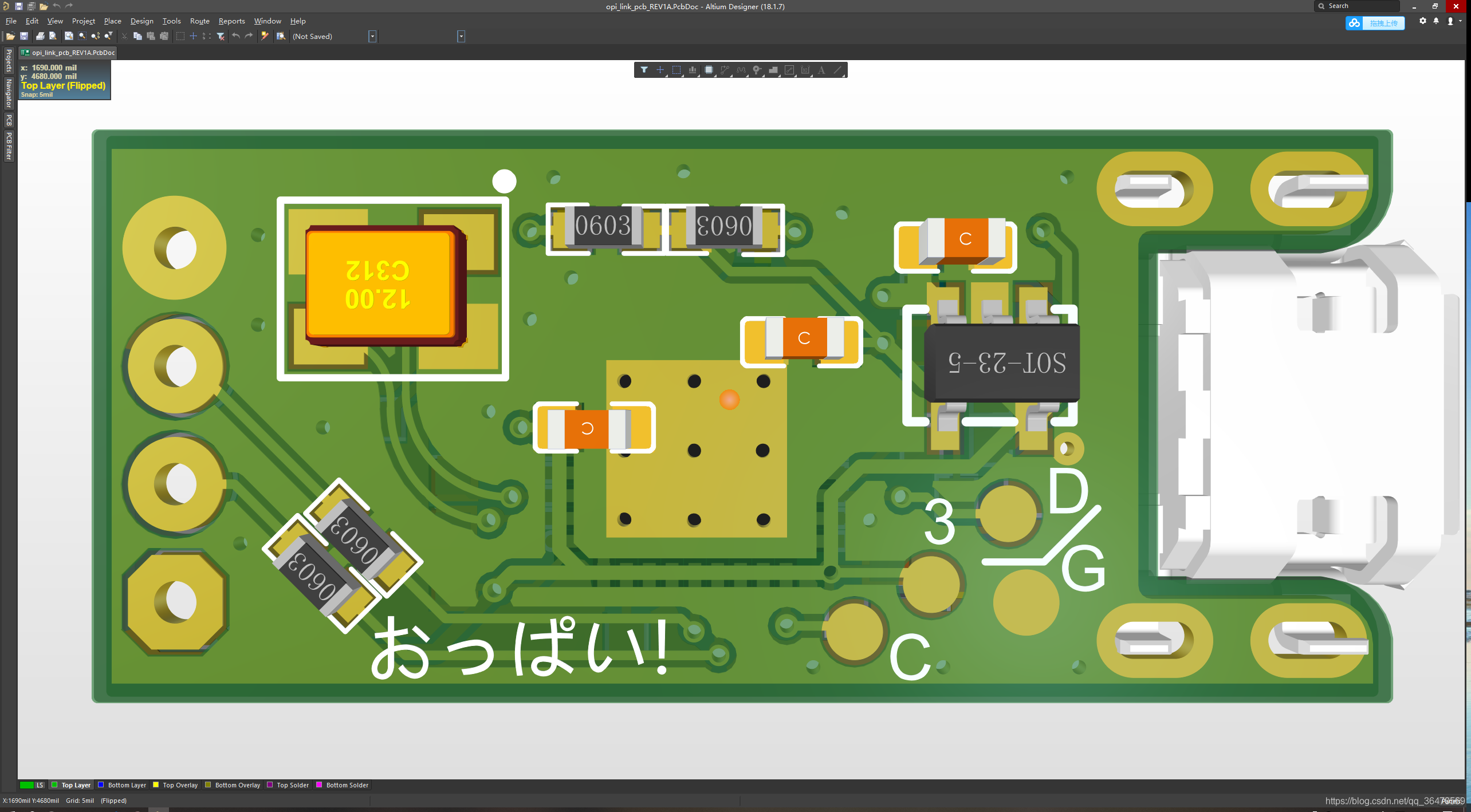

做好了以后的实物就是这个样子的~

(反面有些神奇的内容~)

可以看到左侧的电阻位置做了修改,就是D-上的拉高重新回到D+上去,即正常。

在debug的过程中,顺便学习了一波USB连接的知识。现总结一下。

首先在debug的过程中,做的第一件事肯定就是将自己的原理图和别人的做对比,我对比了我在github上下载到的图,发现并没有什么两样。。。反而一模一样,就因为这个卡了好几个小时,实在是蠢哭了

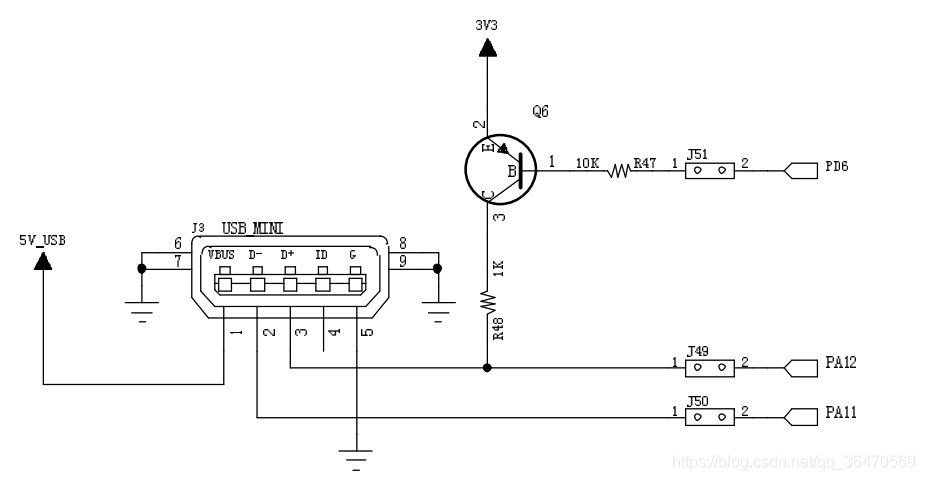

除了对比别人做的DAP的图纸,我还查了一大堆有关STM32 USB的资料,发现有的同学画的板子上还有一颗三极管,同时我拆了一个逐飞的DAPLink,发现上面也有一个三极管,而且是正好连接在D+线上的。

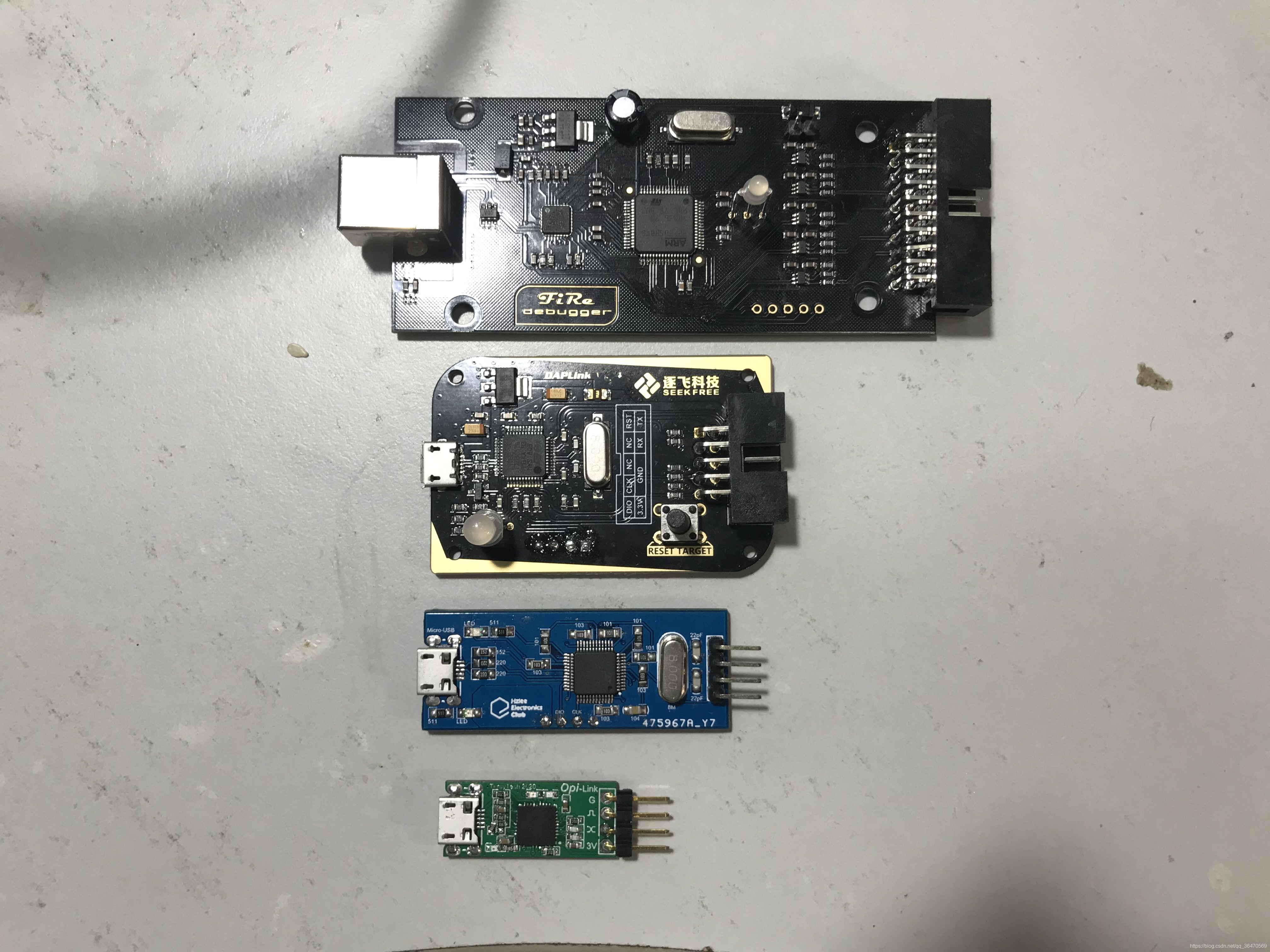

从上到下分别为野火的高速DAP仿真器,逐飞DAPLink,实验室自产JLINK-OB,和DIY的Opi-Link

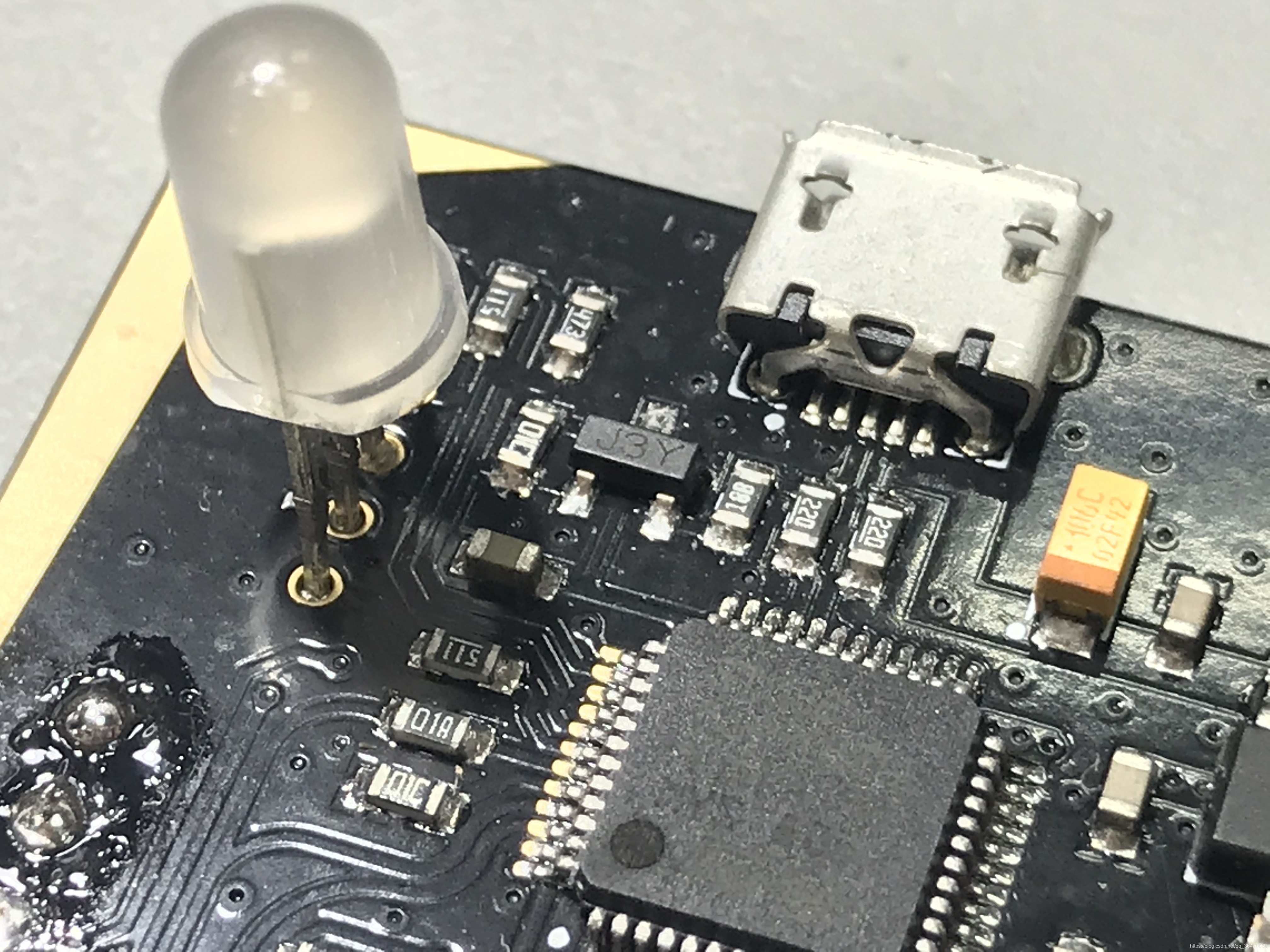

下面我们就来简单分析一下逐飞DAPLink的硬件电路上的三极管。

从图中可以看到,USB的左边信号线旁边过了一颗电阻,连接到三极管J3Y的第二脚。其第三脚连接到供电,图中可以看到旁边有个电容。第一脚连接到一颗01C也就是10K电阻,并且旁边有个过孔推测这里就是控制三极管的引脚了。

之所以会有这样的一个电路,其实不是检测usb接口是否接入了设备。而是为了让这个USB设备具备了重新枚举的功能,可以在使用过程中重新被电脑识别。

在USB通信过程的第一步,主机集线器监视着每个端口的信号电压,当有新设备接入时便可觉察。(集线器端口的两根信号线的每一根都有15kΩ的下拉电阻,而每一个设备在D+都有一个1.5kΩ的上拉电阻(如果没有上拉电阻,就会像图中一样为了重枚举功能添加一颗三极管)。当用USB线将PC和设备接通后,设备的上拉电阻使信号线的电位升高,因此被主机集线器检测到。一旦USB主机检测到了USB D+信号线由低电平转向高电平,就会开始枚举)

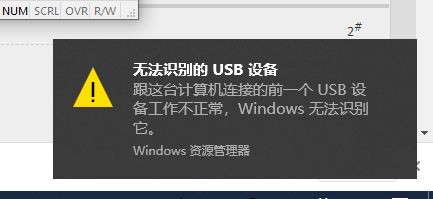

这也就解释了为什么网上有些STM32 USB通信出错的时候,将USB初始化提前即可解决问题。因为如果主机在从机USB外设还没有完成初始化之前开始枚举,从机就不可能发送正确的信息返回主机,在多次枚举之后无响应,USB主机就会自动弹出报错了。

我看了这些资料之后,修改了一下代码,把USB外设初始化提前到了时钟初始化之后,但是问题仍然没有解决hhh

我也没想到居然是自己图画错了,结果白白浪费了好几个小时

在重新连接D+的上拉电阻之后,问题恢复,USB设备可以正常读取。但是很显然我设计的这种DAPLINK是不具备再次枚举的功能的,也就是说如果设备掉线了可能需要拔掉电源重新插上,不过这样也是可以正常工作的,问题不大。

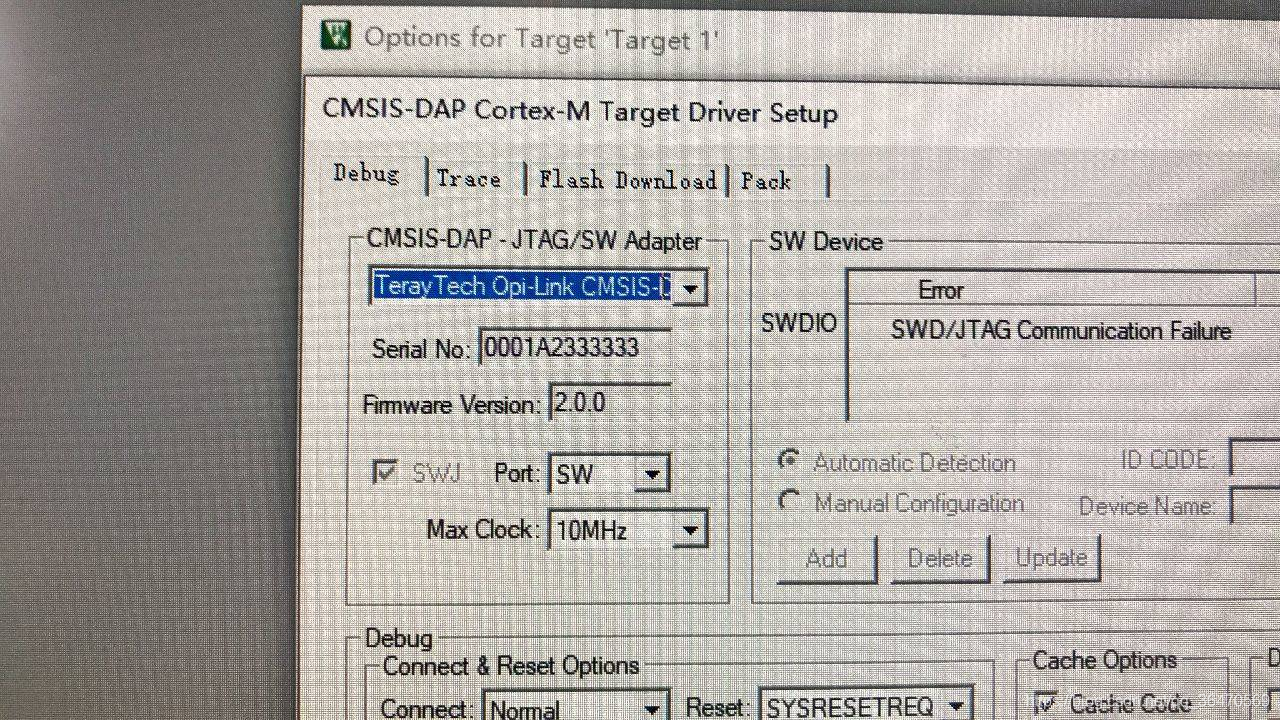

我很喜欢DAP的其中一点就是开源的话可以乱改名字hhhh 还有序列号2333333

但是没想到这DAP也是个傲娇呢,如果你把它后面的CMSIS-DAP的字段删除,就会出现设备管理器可以读取到,但是KEIL不能读取到的怪毛病,想想之前看到的逐飞DAP,野火DAP,好像都是包含有CMSIS-DAP字段的。或许可以通过修改驱动什么的解决这个问题呢?等着以后有大佬来探索吧~

后期会继续推出Opi-Link HS(高速版),先画个饼。期末考试了挺忙的,考完再和dalao们研究。

以上desu。