Multisim的支路及总线设计

1、实验原理

最近在使用multisim设计时,用到了总线和支路设计,这里记录一下,方便以后查阅相关操作。其中主要是总线的使用和支路连接器的使用。

2、实验操作

(1)总线的使用

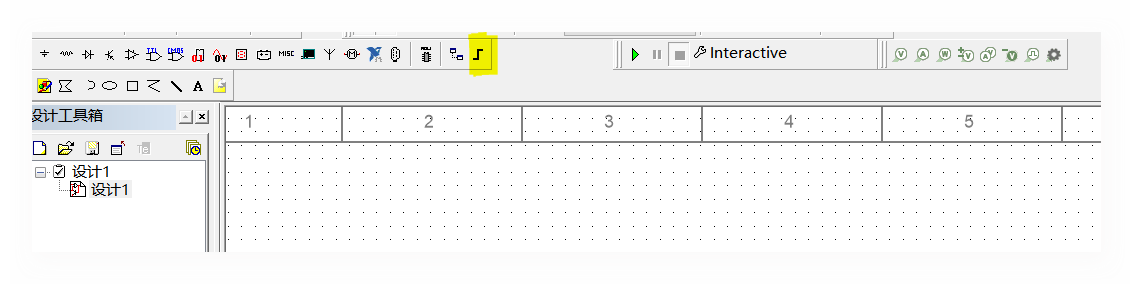

图中黄色标记的就是总线的快速绘制工具。

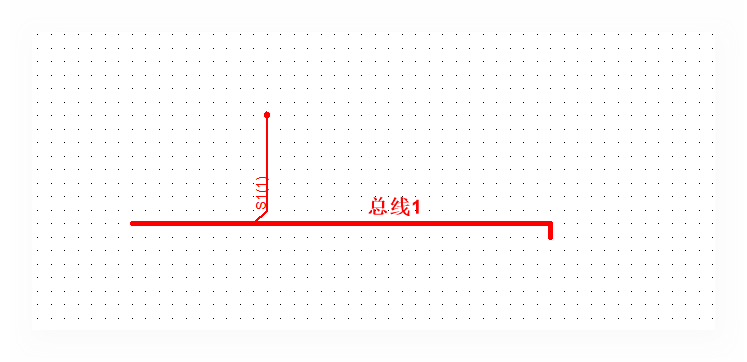

绘制总线直接在空的地方绘制,不用接入器件。总线的支线绘制则是总器件出发连接到总线。这个时候就是弹出命名窗口。这个命名就是这条支路的命名。最后这条支线会显示线名字和连接在总线中的名字。这两个名字的作用范围不同。括号内的是线的名字,作用于整个电路,外面的是支线的名字,作用于总线。使用总线的好处就是可以使用总线中的代号连接,放置出现错误连接。在大型设计中,命名可能有上百个,一旦出现误连,查找是极其困难的。

(2)支电路的使用

对于一个复杂的电路系统而言,不可能将每一个设计都综合在一张图纸上。这时候就需要使用一个顶层,将每个具有特定功能的电路组织起来,实现模块化的设计。在顶层调用支电路时,就需要使用支电路操作。

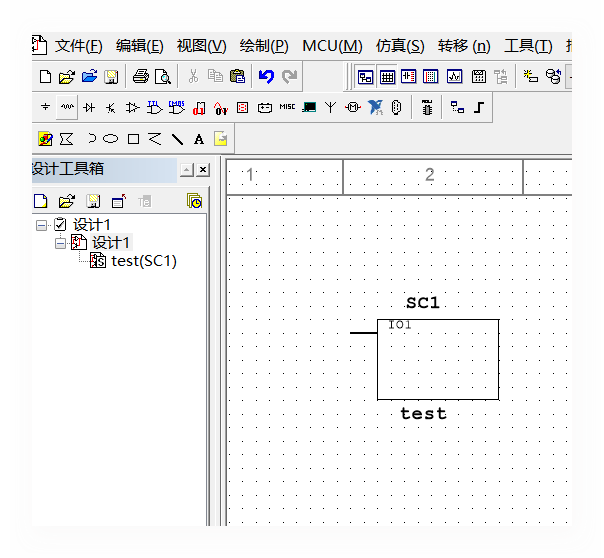

绘制》绘制支电路

这个操作就可以实现支电路的绘制。初始的支电路是空的,只有名字,没有端口。在设计工具箱中展开设计可以看到命名好的支电路。将支电路打开。同样在绘制》连接器中可以添加合适的连接器。保存后就会在顶层电路中加入引脚。

这个操作只是将电路浓缩,而不是封装。所以对于支电路内的端口命名,主电路也是可以访问的。如果想实现封装,需要使用层次块。这里就不介绍了。注意,支电路的连接器是可以和别的支电路同名的,不会连接在一起。这里可以理解为连接器只是作用在主电路符号中的特定引脚,而不参与电路结构。

3、实验总结

这里简单的总结了一下Multisim的规模较大的设计方法。介绍了两种处理引线较多和电路功能较多的电路实现方法。