计算机组成原理

第一章

主机:CPU + 主存储器

CPU: 运算器 + 控制器

主存储器,也叫 主存,内存

外设: I/O设备 + 辅助存储器

I/O设备: 输入设备 + 输出设备

辅助存储器,也叫 辅存,外存

计算机的功能部件:

- 存储器

- 运算器

- 控制器

- 输入设备

- 输出设备

主存储器

主存储器:存储体+MAR(地址寄存器)+MDR(数据寄存器)

- MAR(地址寄存器)存放我们想要访问的单元的地址

- MDR(数据寄存器)存放我们从某个单元取出的代码,或者是想要存入的代码

- 时序控制逻辑能够控制对存储器的访问步骤

在地址寄存器和存储体之间,隔着 译码器&驱动器

这里讲一下存储器的基本结构

见图:

这是一个***存储元***

上述是读出数据,同理写进去数据,那么就是从右往左.

存储体是由许多存储单元构成

存储单元是由许多存储元构成

这下面图中一行就是存储单元

红线是连在一起的,绿线也是连在一起的,所以读写一个存储单元,只需要读一次,不需要分多个存储元来读.

来看这个图,一个Byte就是8位(bit),因为是八个存储元构成.

绿色圈起来的就是存储字

一个存储单元存储的位数,叫做存储字长

译码器:能够把地址寄存器的地址翻译成目标单元的具体序列号

这里还结合了译码器,这是三位的.可以有000–111一共8个数

(后续补充译码器相关)

运算器

功能:对数据进行加工处理,完成算数运算和逻辑运算

算术运算: 加减乘除等

逻辑运算:与,或,非,异或,同或,移位等

构成:

- 乘商寄存器(MQ)

- 累加器(ACC)

- 算术逻辑单元**(ALU)**

- 操作数寄存器(X)

- 变址基址寄存器(PSW)

(其中ALU是核心部分)

控制器

构成:

- CU(控制单元) 分析指令,给出控制信号

- IR(指令寄存器) 存放当前正在执行的指令

- PC(程序计数器) 存放当前 欲执行的指令的地址,有自动加1的能力,这样可以形成下一条指令的地址

计算机的工作流程–取数指令

接下来看看这些概念

操作码用来表示操作的性质,地址码用来表示操作数在存储器的位置

数据寄存器既可以存数据,又可以存指令.

CPU区分指令和数据的依据,就是根据指令周期的不同阶段.

(意思就是,A步骤取出来的就是数据,B步骤取出来的就是地址)

取数指令分为三步:

- 取指令

- 分析指令

- 取数

具体步骤如下:

(下方的标号1-9可以对应下图)

取指令:

- 把PC里面的数据传送到MAR(地址寄存器) (PC) -> MAR

- 根据MAR里面的指令去存储体内找到指令 M(MAR)

- 把得到指令(具体内容)传送给MDR(数据寄存器) M(MAR) -> MDR

- 把得到的指令传送给(指令寄存器) (MDR) -> IR

分析指令

- 将指令发送给CU,即发送过去处理 OP(IR) -> CU

(这样CU才能发出各种其它操作指令)

执行 取数指令

- 将地址码传送给MAR(地址寄存器) Ad(IR) ->MAR

- 根据地址在存储体内寻找 M(MAR)

- 将得到的地址码给MDR(数据寄存器) M(MAR) -> MDR

- 将MDR中的地址码给累加器 (MDR) ->ACC

I/O设备

构成

- 输入设备

- 输出设备

计算机系统的层次结构

一条汇编语言,对应一条机器语言.

层次结构是 5层

微程序机器M0–> 传统机器M1 --> 虚拟机器M2(操作系统机器) --> 虚拟机器M3(汇编语言机器) --> 虚拟机器M4(高级语言机器)

微程序机器层M0

M1

上面是硬件,下面是软件

M2混合层

M3

M4

M0.M1都可以称为裸机4

计算机性能指标

性能指标:

-

容量

- 系统支持最大容量

- 实际容量

- 地址映射

-

速度

- 机器字长

- CPU时钟周期与主频

- CPI

- CPU执行时间

- MIPS , MFLOPS…

- 数据通路带宽

- 吞吐率

- 响应时间

容量

译码器输入是地址,输出是对应的存储单元

如果MAR(地址寄存器)的位数是n,那么对应存储单元的个数是 2^n

- 给出地址寄存器(假设是a)是为了计算有多少个存储单元的,

- 再给出数据寄存器位数(假设是8位), 那么就是可以计算总容量了 (根据上面的假设得到总容量 2^a * 8)

速度

- 机器字长: 计算机能够直接处理的二进制数的位数(一般等于内部寄存器的大小)

决定了运算精度,也决定了运算速度 - 存储字长: 存储单元存储的二进制代码的长度

- 指令字长:一个指令中包含的二进制位数,

指令字长一般是存储字长的整数倍

存储字长和指令字长都是字节的整数倍

CPU时间:运行一个程序所花费的时间

-

CPU时钟周期:就是最小的一个重复的单元

-

CPU时钟频率(主频)= 1 / CPU时钟周期

-

CPI: 执行一条指令所需的CPU时钟周期 数目(便于理解的角度上说: 也就是说要多个周期才能执行完一个指令)

(一个周期完成多个指令也是可以的,所以这里就是方便理解说的错话)

某条指令消耗的时间=CPI * CPU时钟周期

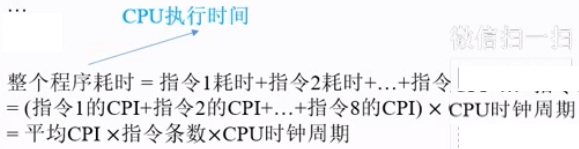

一个程序由多个指令组成,所以计算一个程序的总耗时(也就是CPU执行时间),就要把多个指令的耗时相加

CPI是一条指令耗费的周期数,( 1 / CPI ) 是一周期完成的指令条数

MIPS:每秒执行多少百万条指令

-

MIPS = 指令条数 / (执行时间 * 10^6) = 主频 /(CPI 10^ 6)*

(这个主频/CPI是有点难搞的 f / (CPI * )10^6) = 1 / ( T * CPI * 10^6 )= 1 / (一条指令耗费的时间 * 10^6) = 1秒能执行的指令数 / 10 ^ 6 = 每秒执行的百万指令条数 -

MIPS= (一周期完成的指令条数 * 时钟频率 ) / ( 10^6 )

以上两个条是一样的,就是CPI取反一下(1 / CPI)

数据通路带宽:

定义:数据总线一次能并行传送信息的位数

吞吐量

指的是在单位时间内处理请求的数量

它取决于信息能够多快地输入内存,CPU多快地取指令,数据能够多快地从内存中取出或者存入, 以及所得结果能多快地从内存中送给一台外部设备.

系统吞吐量主要取决于主存的存取周期

响应时间

指的是: 用户向计算机发送一个请求 , 到系统对该请求做出相应并获得它所需要的结果的等待时间.

通常包括 CPU时间(运行一个程序所花费的时间) , 等待时间 (用于磁盘访问,存储器访问 , I/O操作, 操作系统开销等时间)