IF阶段:

IF2ID_IR=IMEM[PC];

IF2ID_NPC,PC=(EXE2MEM_Branch&&(EXE2MEM_ALUOut==0))?EXE2MEM_BranchPC:PC+4;

ID阶段:

ID2EXE_NPC=IF2ID_NPC;

ID2EXE_Rs=RegFile[IF2ID_IR[25:21]];

ID2EXE_Rt=RegFile[IF2ID_IR[20:16]];

ID2EXE_Imm=signed_extended(IF2ID_IR[15:0]);

ID2EXE_rt=IF2ID_IR[20:16];

ID2EXE_rd=IF2ID_IR[15:11];

以及8个控制信号:

ID2EXE_RegDst;

ID2EXE_RegWrite;

ID2EXE_ALUSrc;

ID2EXE_Branch;

ID2EXE_MemRead;

ID2EXE_MemWrite;

ID2EXE_MemtoReg;

ID2EXE_ALUOp;

EXE阶段

EXE2MEM_ALUOut=ID2EXE_Rs op ID2EXE_Rt or

EXE2MEM_ALUOut=ID2EXE_Rs +ID2EXE_Imm or

EXE2MEM_ALUOut=ID2EXE_Rs-ID2EXE_Rt

EXE2MEM_BranchPC=ID2EXE_NPC+(ID2EXE_Imm<<2)

EXE2MEM_RegRd=(ID2EXE_RegDst)?ID2EXE_rd:ID2EXE_rt;

EXE2MEM_Rt=ID2EXE_Rt;

以及5个控制信号

EXE2MEM_Branch=ID2EXE_Branch;

EXE2MEM_MemRead=ID2EXE_MemRead;

EXE2MEM_MemWrite=ID2EXE_MemWrite;

EXE2MEM_MemtoReg=ID2EXE_MemtoReg;

EXE2MEM_RegWrite=ID2EXE_RegWrite;

MEM阶段

MEM2WB_RegRd=EXE2MEM_RegRd;

MEM2WB_ALUOut=EXE2MEM_ALUOut;

if(EXE2MEM_MemRead=1)

MEM2WB_LDM=DMEM[EXE2MEM_ALUOut];

if(EXE2MEM_MemWrite=1)

DMEM[EXE2MEM_ALUOut]=EXE2MEM_Rt;

MEM2WB_RegWrite=EXE2MEM_RegWrite;

MEM2WB_MemtoReg=EXE2MEM_MemtoReg;

WB阶段

if(MEM2WB_RegWrite)

RegFile[MEM2WB_RegRd]=(MEM2WB_MemtoReg)?

MEM2WB_LDM:MEM2WB_ALUOut;

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07/19 19:57:45

// Design Name:

// Module Name: MIPS

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MIPS(

input clk,

input rst

);

reg [31:0] RegFile[0:31];

reg [31:0] IMEM[0:255];

reg [31:0] DMEM[0:255];

integer i;

initial

begin

for(i=0;i<256;i=i+1)

DMEM[i]<=i;

end

initial

begin

for(i=0;i<256;i=i+1)

RegFile[i]<=i;

end

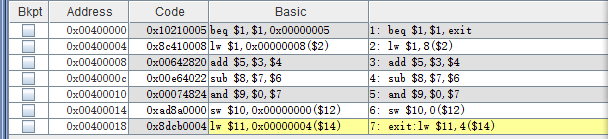

initial

begin

IMEM[0]=32'h10210005;

IMEM[4]=32'h8c410008;

IMEM[8]=32'h00642820;

IMEM[12]=32'h00e64022;

IMEM[16]=32'h00074824;

IMEM[20]=32'had8a0000;

IMEM[24]=32'h8dcb0004;

end

//IF2ID

reg [31:0]IF2ID_IR;

reg [31:0]IF2ID_NPC;

reg [31:0]PC;

//ID2EXE

reg [31:0] ID2EXE_NPC;

reg [31:0] ID2EXE_Rs;

reg [31:0] ID2EXE_Rt;

reg [31:0] ID2EXE_Imm;

reg [4:0] ID2EXE_rt;

reg [4:0] ID2EXE_rd;

reg ID2EXE_RegDst;

reg ID2EXE_RegWrite;

reg ID2EXE_ALUSrc;

reg ID2EXE_Branch;

reg ID2EXE_MemRead;

reg ID2EXE_MemWrite;

reg ID2EXE_MemtoReg;

reg [1:0] ID2EXE_ALUOp;

//EXE2MEM

reg [31:0] EXE2MEM_ALUOut;

reg [31:0] EXE2MEM_BranchPC;

reg [31:0] EXE2MEM_Rt;

reg [4:0] EXE2MEM_RegRd; //寄存器堆写地址

reg EXE2MEM_Branch;

reg EXE2MEM_MemRead;

reg EXE2MEM_MemWrite;

reg EXE2MEM_MemtoReg;

reg EXE2MEM_RegWrite;

//MEM2WB

reg [31:0] MEM2WB_ALUOut;

reg [31:0] MEM2WB_LDM;

reg [4:0] MEM2WB_RegRd;

reg MEM2WB_MemtoReg;

reg MEM2WB_RegWrite;

//*****************************************************************************//

//IF阶段

always@(posedge clk,posedge rst)

if(rst)

begin

PC<=32'd0;

IF2ID_IR<=32'd0;

IF2ID_NPC<=32'd0;

end

else

begin

IF2ID_IR<=IMEM[PC];

if(EXE2MEM_Branch&&(EXE2MEM_ALUOut==0))

begin

PC<=EXE2MEM_BranchPC;

IF2ID_NPC<=EXE2MEM_BranchPC;

end

else

begin

PC<=PC+32'd4;

IF2ID_NPC<=PC+32'd4;

end

end

//ID阶段

always@(posedge clk,posedge rst)

if(rst)

begin

ID2EXE_MemRead<=1'b0; //关闭存储器读使能

ID2EXE_MemtoReg<=1'b0; //来自ALUOut

ID2EXE_MemWrite<=1'b0; //关闭存储器写使能

ID2EXE_Branch<=1'b0; //不是分支

ID2EXE_RegDst<=1'b0; //目的寄存器为rt

ID2EXE_RegWrite<=1'b0; //关闭寄存器堆写使能

ID2EXE_ALUSrc<=1'b0; //ALU操作数来自rt

ID2EXE_ALUOp<=2'b00; //ALU控制码

end

else

case(IF2ID_IR[31:26])

6'b000000:begin

ID2EXE_RegDst<=1'b1;

ID2EXE_ALUSrc<=1'b0;

ID2EXE_MemtoReg<=1'b0;

ID2EXE_RegWrite<=1'b1;

ID2EXE_MemRead<=1'b0;

ID2EXE_MemWrite<=1'b0;

ID2EXE_Branch<=1'b0;

ID2EXE_ALUOp<=2'b10;

end

6'b100011:begin

ID2EXE_RegDst<=1'b0;

ID2EXE_ALUSrc<=1'b1;

ID2EXE_MemtoReg<=1'b1;

ID2EXE_RegWrite<=1'b1;

ID2EXE_MemRead<=1'b1;

ID2EXE_MemWrite<=1'b0;

ID2EXE_Branch<=1'b0;

ID2EXE_ALUOp<=2'b00;

end

6'b101011:begin

ID2EXE_RegDst<=ID2EXE_RegDst;

ID2EXE_ALUSrc<=1'b1;

ID2EXE_MemtoReg<=ID2EXE_MemtoReg;

ID2EXE_RegWrite<=1'b0;

ID2EXE_MemRead<=1'b0;

ID2EXE_MemWrite<=1'b1;

ID2EXE_Branch<=1'b0;

ID2EXE_ALUOp<=2'b00;

end

6'b000100:begin

ID2EXE_RegDst<=ID2EXE_RegDst;

ID2EXE_ALUSrc<=1'b0;

ID2EXE_MemtoReg<=ID2EXE_MemtoReg;

ID2EXE_RegWrite<=1'b0;

ID2EXE_MemRead<=1'b0;

ID2EXE_MemWrite<=1'b0;

ID2EXE_Branch<=1'b1;

ID2EXE_ALUOp<=2'b01;

end

default:begin

ID2EXE_RegDst<=1'b0;

ID2EXE_ALUSrc<=1'b0;

ID2EXE_MemtoReg<=1'b0;

ID2EXE_RegWrite<=1'b0;

ID2EXE_MemRead<=1'b0;

ID2EXE_MemWrite<=1'b0;

ID2EXE_Branch<=1'b0;

ID2EXE_ALUOp<=2'b00;

end

endcase

always@(posedge clk,posedge rst)

if(rst)

begin

ID2EXE_Rs<=32'd0;

ID2EXE_Rt<=32'd0;

ID2EXE_Imm<=32'd0;

ID2EXE_NPC<=32'd0;

ID2EXE_rt<=5'd0;

ID2EXE_rd<=5'd0;

end

else

begin

ID2EXE_Rs<=RegFile[IF2ID_IR[25:21]];

ID2EXE_Rt<=RegFile[IF2ID_IR[20:16]];

ID2EXE_Imm<={

{

16{

IF2ID_IR[15]}},IF2ID_IR[15:0]};

ID2EXE_NPC<=IF2ID_NPC;

ID2EXE_rt<=IF2ID_IR[20:16];

ID2EXE_rd<=IF2ID_IR[15:11];

end

//EXE阶段

always@(posedge clk,posedge rst)

if(rst)

begin

EXE2MEM_BranchPC<=32'd0;

EXE2MEM_ALUOut<=32'd0;

EXE2MEM_Rt<=32'd0;

EXE2MEM_RegRd<=5'd0;

end

else

begin

EXE2MEM_BranchPC<=ID2EXE_NPC+(ID2EXE_Imm<<2);

EXE2MEM_Rt<=ID2EXE_Rt;

EXE2MEM_RegRd<=(ID2EXE_RegDst)?ID2EXE_rd:ID2EXE_rt;

case(ID2EXE_ALUOp)

2'b00: //lw or sw

begin

EXE2MEM_ALUOut<=ID2EXE_Rs+ID2EXE_Imm;

end

2'b10: //R型

case(ID2EXE_Imm[5:0]) //funct功能码

6'b100000:

EXE2MEM_ALUOut<=ID2EXE_Rs+ID2EXE_Rt;

6'b100010:

EXE2MEM_ALUOut<=ID2EXE_Rs-ID2EXE_Rt;

6'b100100:

EXE2MEM_ALUOut<=ID2EXE_Rs&ID2EXE_Rt;

6'b100101:

EXE2MEM_ALUOut<=ID2EXE_Rs|ID2EXE_Rt;

6'b101010:

EXE2MEM_ALUOut<=(ID2EXE_Rs<ID2EXE_Rt)?1'b1:1'b0;

default:

EXE2MEM_ALUOut<=EXE2MEM_ALUOut;

endcase

2'b01: //beq

begin

EXE2MEM_ALUOut<=ID2EXE_Rs-ID2EXE_Rt;

end

default:

EXE2MEM_ALUOut<=EXE2MEM_ALUOut;

endcase

end

always@(posedge clk,posedge rst)

if(rst)

begin

EXE2MEM_RegWrite<=1'b0;

EXE2MEM_MemRead<=1'b0;

EXE2MEM_MemWrite<=1'b0;

EXE2MEM_MemtoReg<=1'b0;

EXE2MEM_Branch<=1'b0;

end

else

begin

EXE2MEM_RegWrite<=ID2EXE_RegWrite;

EXE2MEM_MemRead<=ID2EXE_MemRead;

EXE2MEM_MemWrite<=ID2EXE_MemWrite;

EXE2MEM_MemtoReg<=ID2EXE_MemtoReg;

EXE2MEM_Branch<=ID2EXE_Branch;

end

//MEM阶段

always@(posedge clk,posedge rst)

if(rst)

begin

MEM2WB_ALUOut<=32'd0;

MEM2WB_LDM<=32'd0;

MEM2WB_RegRd<=5'd0;

end

else

begin

MEM2WB_ALUOut<=EXE2MEM_ALUOut;

MEM2WB_RegRd<=EXE2MEM_RegRd;

if(EXE2MEM_MemRead)

MEM2WB_LDM<=DMEM[EXE2MEM_ALUOut];

else if(EXE2MEM_MemWrite)

DMEM[EXE2MEM_ALUOut]<=EXE2MEM_Rt;

end

always@(posedge clk,posedge rst)

if(rst)

begin

MEM2WB_RegWrite<=1'b0;

MEM2WB_MemtoReg<=1'b0;

end

else

begin

MEM2WB_RegWrite<=EXE2MEM_RegWrite;

MEM2WB_MemtoReg<=EXE2MEM_MemtoReg;

end

//WB阶段

always@(posedge clk,posedge rst)

if(rst)

;

else if(MEM2WB_RegWrite)

if(MEM2WB_MemtoReg==1'b1)

RegFile[MEM2WB_RegRd]<=MEM2WB_LDM;

else

RegFile[MEM2WB_RegRd]<=MEM2WB_ALUOut;

endmodule

以下是测试代码:

仿真已通过!