小白阶段的FPGA开发者往往把自己的模块写完就丢,没有保存并且复用的习惯,随着FPGA的学习过程的展开,学会复用自己的设计,能够减轻工作,所以这是一个必备的技能。

首先IP核其实就和单片机芯片的函数库一样,是已经封装好底层,具有一定功能的模块,XLINX公司在VIVADO中已经给我们提供了丰富的ip核,接下来我们说一下如何打包并且调用自己的IP核

此文章基于xlinx artix7 xc7a35t 芯片以及vivado2018.3

一、打包IP核:

我们以一个74ls163为例,首先贴一下代码:

接下来贴一下仿真代码:

约束代码根据你开发板的不同会有不同,这里不贴了。

这样完成了整个项目之后,

在tool-create and package new ip 下根据他的指引一步步打包好IP。

在vivado2018.3中打包ip功能以及被完善得非常好了,需要我们设置的地方已经很少了。

点击next

next

next

finish

点击 package ip

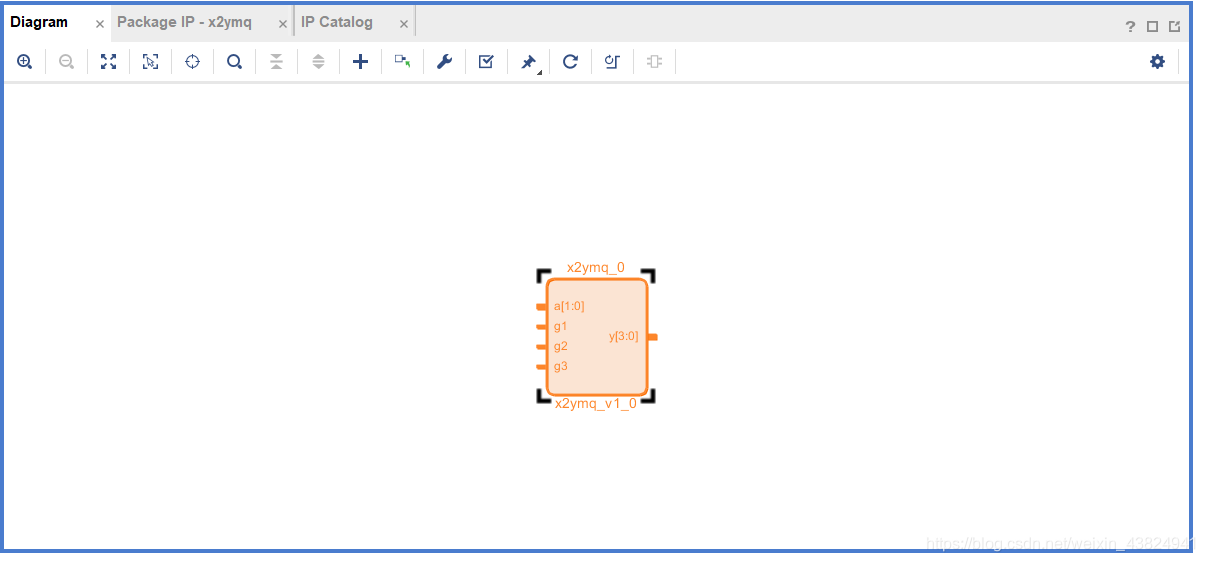

然后,在block design里面,我们可以在画布上搭积木似的调用已有的IP核来进行电路的搭建:

在新建的文件里,想要调用Ip:

右键点击,出现IP setting 这个选项,然后

在这个界面里将IP核的路径添加进去就行了。这里建议专门建立一个IP核文件夹来归类我们的IP核。

这期就更新到这里,谢谢观看!