Automatic Generation of Multi-precision Multi-arithmetic CNN Accelerators for FPGAs

最近arXiv上挂出来一篇文章,采用FPGA实现MobileNet V1,并且完全是不借助片外资源,用的是on-chip memory,没有利用off-chip RAM。整个模型在FPGA的内部有限资源上实现的。能够使得帧率在3000 FPS,这个是最近我看到的一个很快的实现速度了。整个网络采用了多精度实现,而且是软硬件结合的方式。整个实现流程如图所示。

文中也提到了常规算法,在FPGA上实现所采用的方式,即将计算展开,叫做roll-unroll, flatten。本文采用的flattened streaming cores来进行计算。整个卷积的计算采用的寄存器实现,能够高效的进行操作。这个工程量还是非常大的。下图展示了常规卷积的实现过程,一个周期cycle计算每一层output的c'个通道上的每一个点的值。采用移位或者乘法器的方式实现。第二个分图展示的是depthwise convolution的计算过程,对每一层单独使用一层filter。这个表示也是standard convolution和depthwise convolution的原理解释。

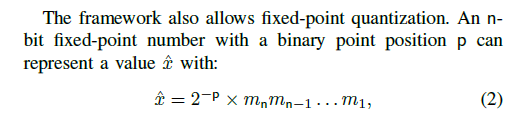

对于多精度,多bit数的执行,将activation的值,设置为8 bit 定点数,只是说定点量化的整数和小数,是可以varying from convolution layer。每一层各有不同,是 一个贪心搜索算法来搜索得到的。

同时,作者也单独把BN层来进行量化,这里是16位 定点数。

整体实现难度很大,需要仔细的去看实现细节。在真实实现过程中,问题还是很多。各种配置文件。c++写一些比较上层难以优化和实现的算法和代码。下端verilog写卷积的模板文件,以及可分离卷积,这些规则极强,大量for循环计算的模块,Verilog效率高。混合精度的实现,需要利用寄存器来发挥优势,而浮点数据的操作,就要消耗更多资源,这时候需要用上层一点的类似于HLS来实现。整个流水的设计,需要紧密的在每一层上做好时钟计算和设计,上一层的网络输出结果,以如何的方式,直接接入下一层的计算。整个流水排开之后,才能达到所叙述的3000fps。单独处理一张图片,应该是不能达到的。

具体实现过程还有很多细节,作者的最优权重搜索算法,如何对应不同的input size,模型大小,做扩展,而且是可配置的,这些在FPGA实现上,算是一个优点。因为其他的FPGA实现的方法,都是写完一个,就定死,不方便在重新改写模型的大小,因为里面涉及时序,涉及流水的对齐。这个软件定义模型,然后在硬件综合生成电路,再转换为bit流的方式,可以加快各种模型原型实现的速度。总体不错。如果想更仔细的看里面的各种细节,查看原文吧。