转自:https://blog.csdn.net/yundanfengqing_nuc/article/details/108223603

文章目录

Concat

这个IP的实现的就是位拼接的功能,如下图所示。这里要将4个1bit的数据拼接为一个4bit数据。因此,Number of Ports设置为4,输入端口的位宽都设置为1。

Slice

Slice的功能正好和Concat功能相反。该IP是从一个多位宽的数据中提取1位或多位,如下图所示。输入数据是32位,现在从中取低4位,故Din From一栏填3,Din Down To一栏填0,此时Dout Width会自动更新为4。

Constant

这个IP的功能很简单,就是输出一个固定常数,位宽可定制,如下图所示。这里我们需要输出一个1bit的常数0,故Const Width设置为1,Const Val设置为0。

Utility Reduced Logic

这个IP实现的是位缩减功能,比如,对于8bit数据,其位缩减与就是各位相与,如下图所示,可支持与、或、异或。

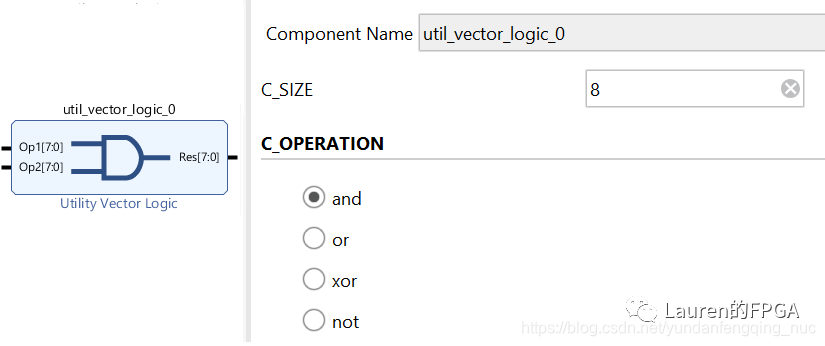

Utility Vector Logic

该IP实现的是按位操作的逻辑运算,比如两个8bit数据按位与,如下图所示。可支持与、或、异或、取反等。如果选择取反,则只有一个输入端口。

IBUFDS、IBUFGDS和OBUFDS

IBUFDS、IBUFGDS和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 是差分输入的时候用,OBUFDS是差分输出的时候用,而IBUFGDS则是时钟信号专用的输入缓冲器。

BUFG、差分转单端之IBUFDS和IBUFDS_GTE2区别

BUFG

BUFG是把局部时钟转为全局时钟,减少时钟延迟。

IBUFDS

在使用差分时钟转单端时,对于普通的bank,可以使用IBUFDS。

IBUFDS_GTE2

对于高速bank,需要使用IBUFDS_GTE2,如果仍然使用IBUFDS,此时在编译或者生成bit时报错,提示该时钟约束有问题,正常差分时钟的电平是不需要约束的,约束完后可以生成bit,但是转出的单端时钟不能使用。

IBUFDS_GTE2原语如下

IBUFDS_GTE2 #(

.CLKCM_CFG("TRUE"), // Refer to Transceiver User Guide

.CLKRCV_TRST("TRUE"), // Refer to Transceiver User Guide

.CLKSWING_CFG(2'b11) // Refer to Transceiver User Guide

)

IBUFDS_GTE2_inst (

.O(clk_156_25M), // 1-bit output: Refer to Transceiver User Guide

.ODIV2(), // 1-bit output: Refer to Transceiver User Guide

.CEB(1'b0), // 1-bit input: Refer to Transceiver User Guide

.I(Q0_CLK1_GTREFCLK_PAD_P_IN), // 1-bit input: Refer to Transceiver User Guide

.IB(Q0_CLK1_GTREFCLK_PAD_N_IN) // 1-bit input: Refer to Transceiver User Guide

);