进入大三下学期了,备战考研的同时也打算整理拓展所学的技能,到时候无论是通过考研初试接着参加复试还是考研失利找工作都能排得上用场。

数字电路这一块最近见识到了UCSD(加州大学)的国际一流水准的课程,深受震惊,所以打算从这里开始,但这个教程还是属于提纲性的,不会把用到的每个东西都解释清楚,但我会告诉大家需要哪些知识。

本系列打算开如下几章:

组合逻辑和同步时序设计

异步时序电路设计 实战:十六人投票器(multisim仿真后自制电路)

FSM(有限状态机)和HLSM(高级状态机)(上板实验)

memory和他们的Verilog实现(仿真和上板实验)

AD/DA转换和它们的Verilog实现(仿真和上板实现)

当然其中有些东西我会随着我的需求来改变,例如ADC这里我会根据我的射频系统学习的要求来做,敬请大家期待。

一.组合逻辑电路

组合逻辑电路,是指输入决定输出,没有记忆(没有储存功能,上一刻的状态不影响下一刻的状态)的数字电路。

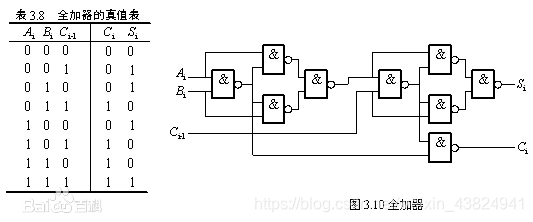

要掌握组合逻辑电路设计需要的基本知识有:基本门电路(与、或、非和它们的组合运算)及其运算关系、用于数字电路的布尔代数(主要是卡诺图化简法的运用)。

组合逻辑电路设计的前提是分析,分析的步骤如下:

1、根据电路图,层层写出逻辑关系,最后得到电路输出和输入变量的关系表达式

2、对上一步得到的表达式进行化简,如果关系过于复杂则要使用代数化简或者卡诺图化简法

3、列真值表,说明电路的功能

设计组合逻辑的步骤则如下:

1、根据实际问题抽象出几个元素:输入、输出变量、逻辑要求(类似于函数的自变量、因变量、函数关系)

2、根据上一步中的几个元素,列出真值表

3、根据真值表,对函数进行化简和变换

4.选择合适的器件,画出电路图

这里有两个需要注意的点:

(1)在卡诺图中一定要注意,自变量两个相邻的状态只能差一个变量,比如输入AB,我们在列举它的四种取值时的排布是00、01、11、10,而不是按照二进制的大小来的

(2)化简的结果是不唯一的,实际工程中,我们常常受到一些限制,所以我们要清楚,即使是最简的逻辑函数,也是可以进行互相变换的,常见的与或、与非与非、或非、或非或非、与或非都可以互相转换,以满足不同的工程实际需求

如何认识常见的组合逻辑运算芯片?

这是一个常见的问题,实际上芯片可以理解为一个设计好并且集成完毕的组合逻辑模块,我们最关心的实际上是译码器(比如74ls138)和数据选择器(比如74ls151),因为他们都可以给出输入变量的全部最小项,而任意逻辑函数都可以表示为最小项之和,所以这决定了他们的重要地位。

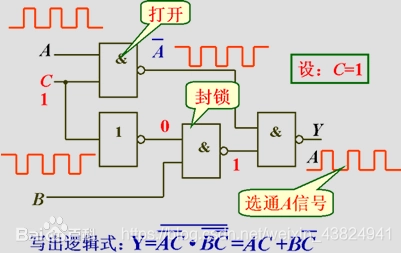

在这里有两种情况,第一是MUX的选择变量数等于逻辑函数输入变量数,第二是MUX选择变量数少于逻辑函数输入变量,前者只需要在所需最小项对应位置输入1,反之输入0就行了,后者则需要选定MUX选择变量上限个的选择变量,进行函数比对或者卡诺图化简,在某些数据选通口加上多出来的逻辑函数输入变量。

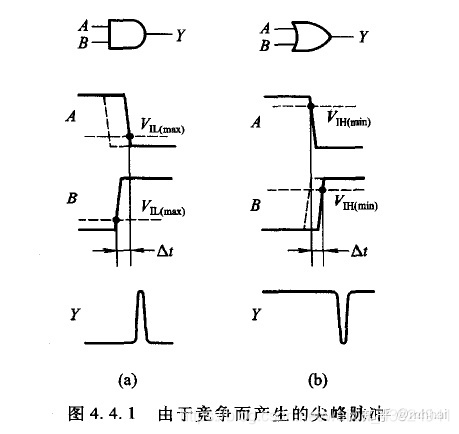

还有一个比较重要的事情是竞争和冒险,竞争是指同一时间2个输入信号向相反方向跳变,冒险则是电路出现了非预期的动作的现象。可以这么说,竞争和冒险没有任何必然关系!,某些同学可能认为竞争是冒险的充分条件,但其实竞争不一定引起冒险,还有一些同学认为竞争是冒险的必要条件,其实也不是!实际工程情况是非常复杂的,即使出现了冒险现象,也不能说一定是竞争引起的,这就是工程和理论的区别!

判断竞争的最简单方式是查看表达式中有没有出现某个变量和它自身反变量的与、或运算。而解决方法是引入冗余项或者添加电容器,但在工程上,这都无疑牺牲了数字电路的工作速度,这是不能容忍的。所以我们在工程中其实更多采取选通的办法。

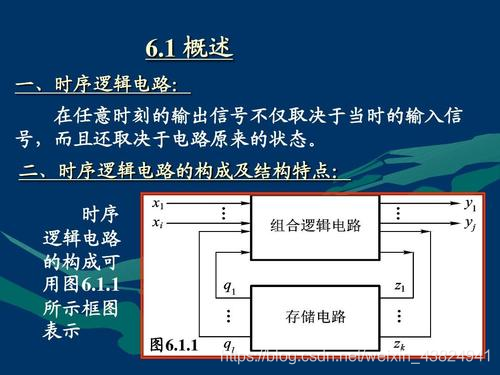

二、基本同步时序电路

时序电路的基础是触发器的知识,还有用于数字电路的布尔代数。

触发器这里要注意空翻以及一次变换现象这两个地方,还有就是,不同触发器之间是可以互相转化以应对实际工程要求的,这个和之前提到的组合逻辑函数表达式相互转化是一样的。

这里还要提一下,我们国内很多大学的教学中弱化了触发器的动态特征,而我在看UCSD的教程时发现他们非常注重动态特性,包括建立时间、保持时间、传输延迟等等都会严格地计算并且表达在时序图中,我觉得这是非常值得我们借鉴的。

时序电路相比于组合逻辑电路来说,就在于多了存储功能,由基本触发器构成的组合逻辑电路实际上能储存一个bit的信息,并且初态严格决定了次态。

同步和异步是重要概念,同步是指所有触发器状态随同一时钟进行翻转。异步则意味着多个时钟或者根本不随时钟变化(比如一些芯片中异步置0功能可以在任意时刻进行clear操作)

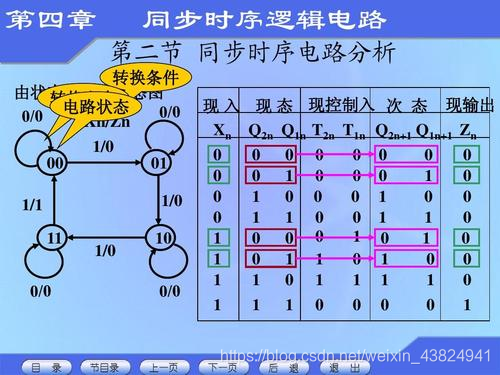

同步时序电路的分析步骤是:

1.根据电路图写出时钟方程、驱动方程和电路的输出方程

2.驱动方程带入触发器特征方程,得出每个触发器状态方程

3.根据时钟从初态开始带入,一步步移动

4.画出状态转换图

5.根据状态转换图画时序图

6.分析功能,检查自启动

异步时序电路的分析主要注意不同时钟就行了

同步时序电路的设计步骤如下:

1.根据实际问题抽象出输入变量和输出变量,确定状态数(这个非常重要)

2.确定触发器的类型和个数,假设触发器个数为n,要保证2^n>电路状态数

3.根据次态和初态画出次态卡诺图,有必要的话要分解,然后得出状态方程

4.状态方程和触发器特征方程对比,确定电路结构

5.检查自启动和无效状态

本期就到此结束,谢谢观看!