基于VHDL语言,设计一个模为129的8421BCD码加法计数器(0~128)

VHDL代码如下:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY cou129 IS

PORT(

en,clk:IN STD_LOGIC;

qa:buffer STD_LOGIC_VECTOR(3 DOWNTO 0);

qb:buffer STD_LOGIC_VECTOR(3 DOWNTO 0);

qc:buffer STD_LOGIC_VECTOR(3 DOWNTO 0);

rco:OUT STD_LOGIc);

END cou129;

ARCHITECTURE a OF cou129 IS

BEGIN

PROCESS(clk)

begin

if clk'event and clk='1' then

if en='1' then

if (qc="0001" and qb="0010" and qa="1000") or qa="1001" then

qa<="0000";

if (qc="0001"and tmb="0010") or qb="1001" then

tmb<="0000";

if qc="0001" then

qc<="0000";rco<='1';

else qc<=qc+1;rco<='0';

end if;

else qb<=qb+1;rco<='0';

end if;

else qa<=qa+1;rco<='0';

end if;

else qc<="0000";qb<="0000";qa<="0000";

end if;

end if;

end process;

end a;

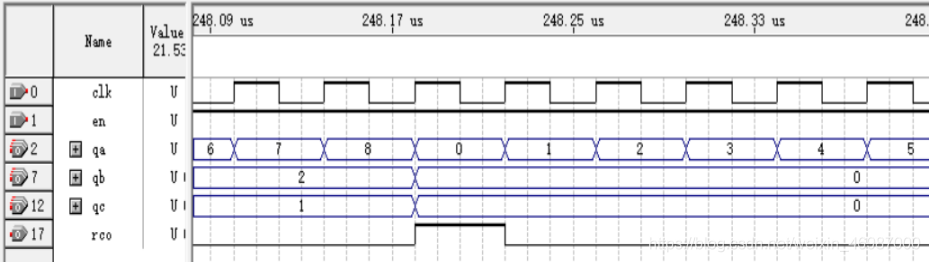

仿真显示:

129进制的加法器