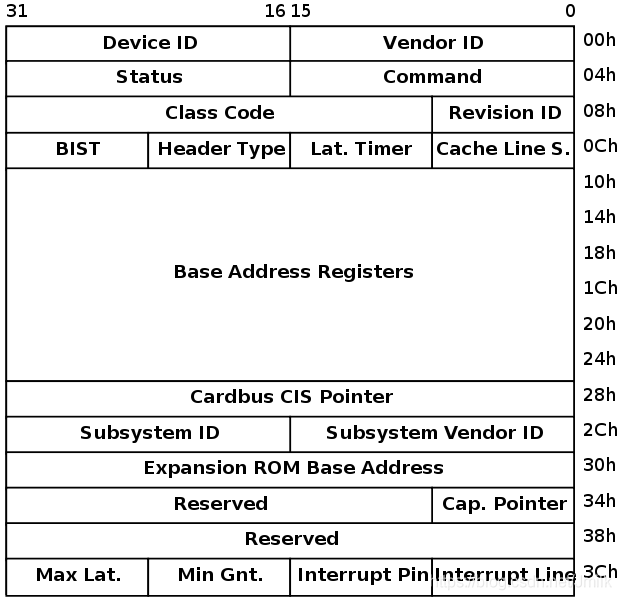

PCI/PCIE配置空间按照寄存器的范围如下图:

PCI 配置空间 0~255 地址空间,总共 256 bytes、 4字节宽的寄存器、总共 64 寄存器 (4*64 = 256 bytes), 内容定义如图所示。

<1>、 PCI ConfigurationSpace Header:

PCI ConfigurationSpace Header的范围是头64字节[0,63]。

PCI ConfigurationSpace Header分为type 0和type 1,type 1是专门给桥设备用的,type 0是给其它设备用的。两种类型首部的寄存器定义有相同的部分,规范中称之为Common Header,也有各自相区别的部分,详细内容请参考规范。不论是那种类型,只要确定了,那么它的格式就是确定的,是严格按照规范定义了的。

<2>、 PCI Capability List:

PCI CapabilityList位于[64-255]区间范围。

它可以被看做是一个由PCI CapabilityItem组成的一个链表。链表的头指针就存在了PCI ConfigurationSpace Header的0x34的一字节的寄存器里。有了这个指针,就可以知道链表的第一个Capability Item存在于[64-255]区间的哪个位置。每个Capability Iteam的大小长度范围不都是一样的,但所有Capability Iteam都定义了一个标准化的Cap Header。例如,PCI规范中对Capability Iteam的类型做了严格定义,都给出了Capability的ID号,这个Cap ID就存放在这个Header里。Header里另一个重要的内容就是下一个Capability Iteam的偏移量,以便形成链表。在PCI CapabilityList的所有存放指针的寄存器都是8位的,因为8位足够在256字节范围内定位了。

具体的Capability类型的定义可能存在于不同的规范中,PCI的基本规范并没有全部覆盖。如果设备自定义Capability只能属于Vendor Specific的类型。标准化了的Capability Item的格式长度是可知的,可以参考相关规范。但对于Vendor Specific类型,由于格式是自定义的,所以规范中给出了求得长度的方法,就是利用存放下一个Capalibity Iteam的寄存器来存放长度。

<3>、 PCIEExtended Configuration Space

在后续的PCIX和PCIE规范中,引入了ExtenedConfiguration Space[256-4095],使得配置空间的范围最大达到4K字节。

在PCIE规范中,扩展的配置空间用于存放PCIE EnhancedCapability List。这个List是一个和PCI Capability List逻辑上类似的一个链表结构,不同的是,链表的第一个Iteam就位于0x100,即从256字节起始。

EnhancedCapability List Iteam也有一个标准化了的Cap Header, 格式也略有变化,除了Cap ID之外,还有几个bit存放版本号。另外,在Cap header里,存放下一个Cap Iteam的位置的寄存器是12位的,以便能在4K范围内定位。因为PCIE EnhancedCapability List和PCI Capability List在空间上是保证隔离的,因此他们的Cap ID定义不需要考虑编码冲突,不同的Cap Item即可能使用相同的Cap ID的值。

同样的,EnhancedCapability List Iteam也有Vendor Specifc的Iteam用于设备存放自定义的寄存器,其长度值被要求存在指定的寄存器中。