JK触发器设计

任务描述

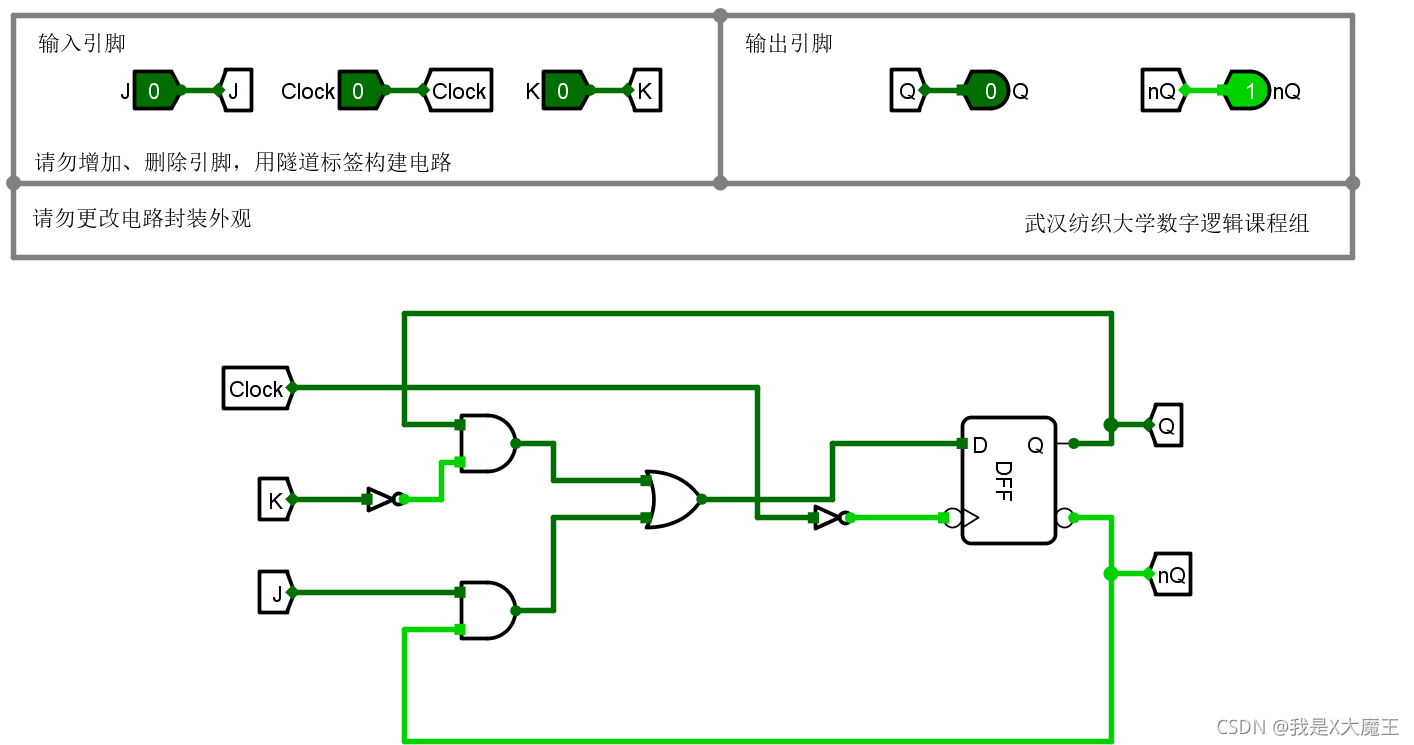

本关任务:在Logisim中,在D触发器的基础上构建JK触发器。

相关知识

在电平敏感型锁存器中,在时钟信号有效(如Clk=1)期间,锁存器的状态Q跟随输入的变化而变化,这种现象称为“空翻”。为了避免出现空翻,可以把状态变化时机限定在时钟信号的上升沿或者下降沿,这种类型的器件称为触发器(Trigger/Flipflop)。

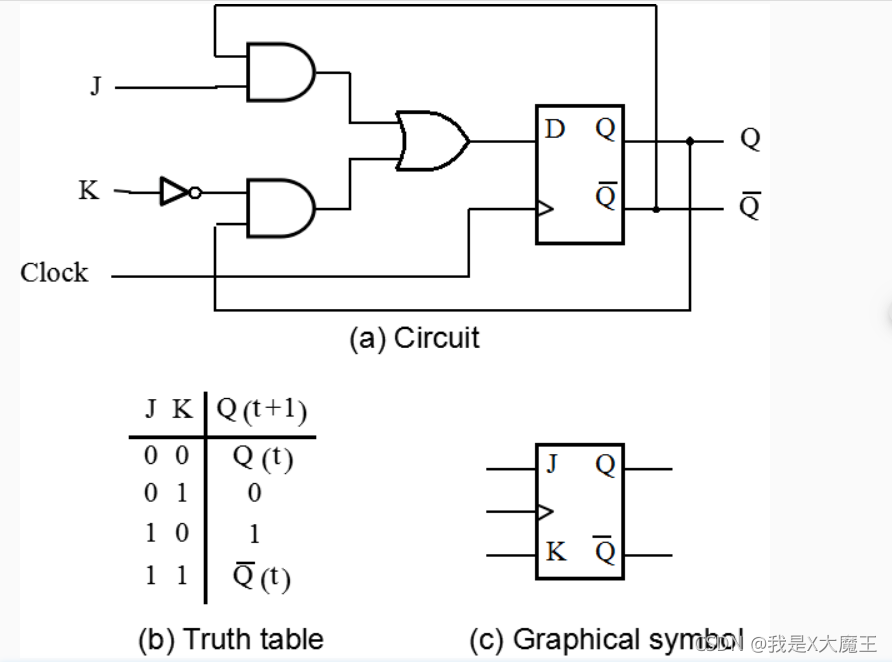

JK触发器(上升沿触发)原理图如下:

其特征方程如下:

Q(t+1) = J ∙ ~Q(t) + ~K ∙ Q(t)

Clk上升沿有效

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“JK触发器”子电路中绘制电路并进行测试。

注意不要改变已有的封装结构,否则无法完成测试!

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Latch_Flipflop.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

常见问题

如果出现震荡,可以用系统中的D触发器来设计。

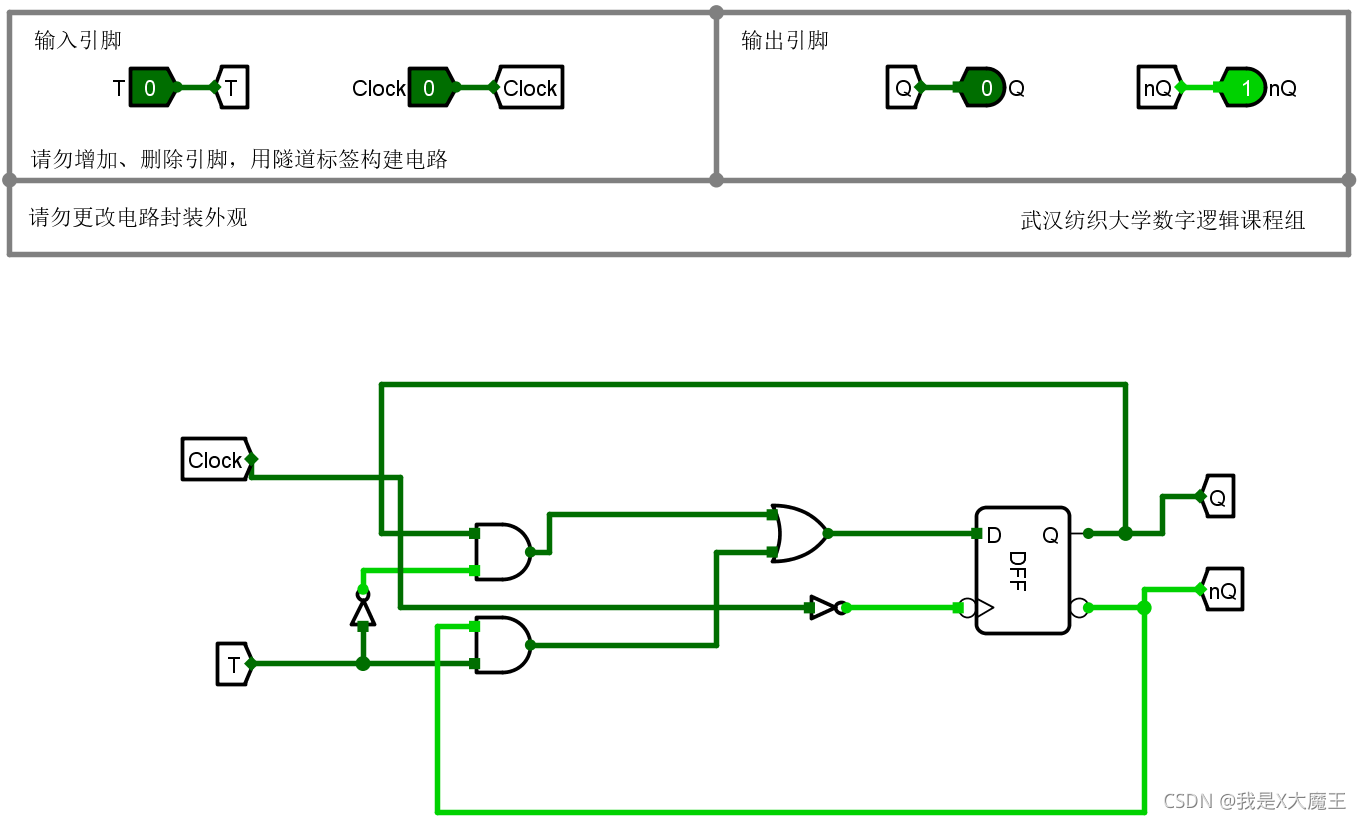

T触发器设计

相关知识

在电平敏感型锁存器中,在时钟信号有效(如Clk=1)期间,锁存器的状态Q跟随输入的变化而变化,这种现象称为“空翻”。为了避免出现空翻,可以把状态变化时机限定在时钟信号的上升沿或者下降沿,这种类型的器件称为触发器(Trigger/Flipflop)。

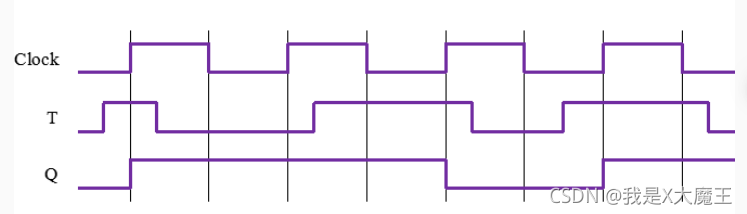

其特征方程如下:

Q(t+1) = T ^ Q(t)

Clk 上升沿有效

欢迎订阅频道,下次再见啦