备战秋招,如何看懂一个陌生的timing report

一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人可能会提到对于特定算法和协议的理解,有些人或许会提到对于软硬件的结合划分,作者想说,这些说法,其实对也不对,硬件描述语言,翻来覆去无非是always和assign这几个语句的反复使用,而一些基础的协议算法,深究起来其实也并不复杂,于作者而言,在常规的技能以外,有两项额外的技能颇为重要,其中之一便为sdc/STA的分析能力,它的重要之处在于作为桥梁建立了前端和后端的连接,虽然对于DE工程师而言,初版交付的sdc往往不甚准确,也没有办法通过这份sdc生成一份无误的timing report,但sdc的内容体现却是完完整整的将时序约束从行为级的描述映射到了gate level这样一个真实的电路层次上面。

写此专栏,一为学习记录,二为交流分享,以犒粉丝读者。

1.1 快速导航链接·

静态时序分析简明教程(一)绪论

静态时序分析简明教程(二)基础知识:建立保持时间,违例修复,时序分析路径

静态时序分析简明教程(三)备战秋招,如何看懂一个陌生的timing report

静态时序分析简明教程(四)时钟常规约束

静态时序分析简明教程(五)时钟其他特性

静态时序分析简明教程(六)端口延迟

静态时序分析简明教程(七)完整端口约束

静态时序分析简明教程(八)虚假路径

静态时序分析简明教程(九)多周期路径

静态时序分析简明教程(十)组合电路路径

静态时序分析简明教程(十一)模式分析与约束管理

静态时序分析简明教程(十二)浅议tcl语言

二、Timing Report

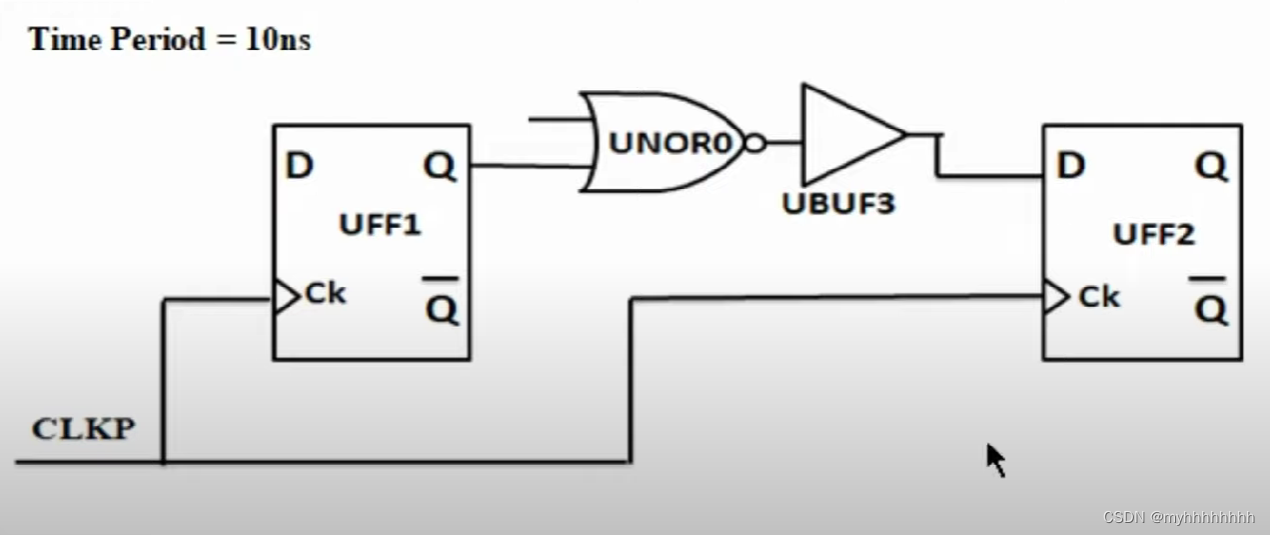

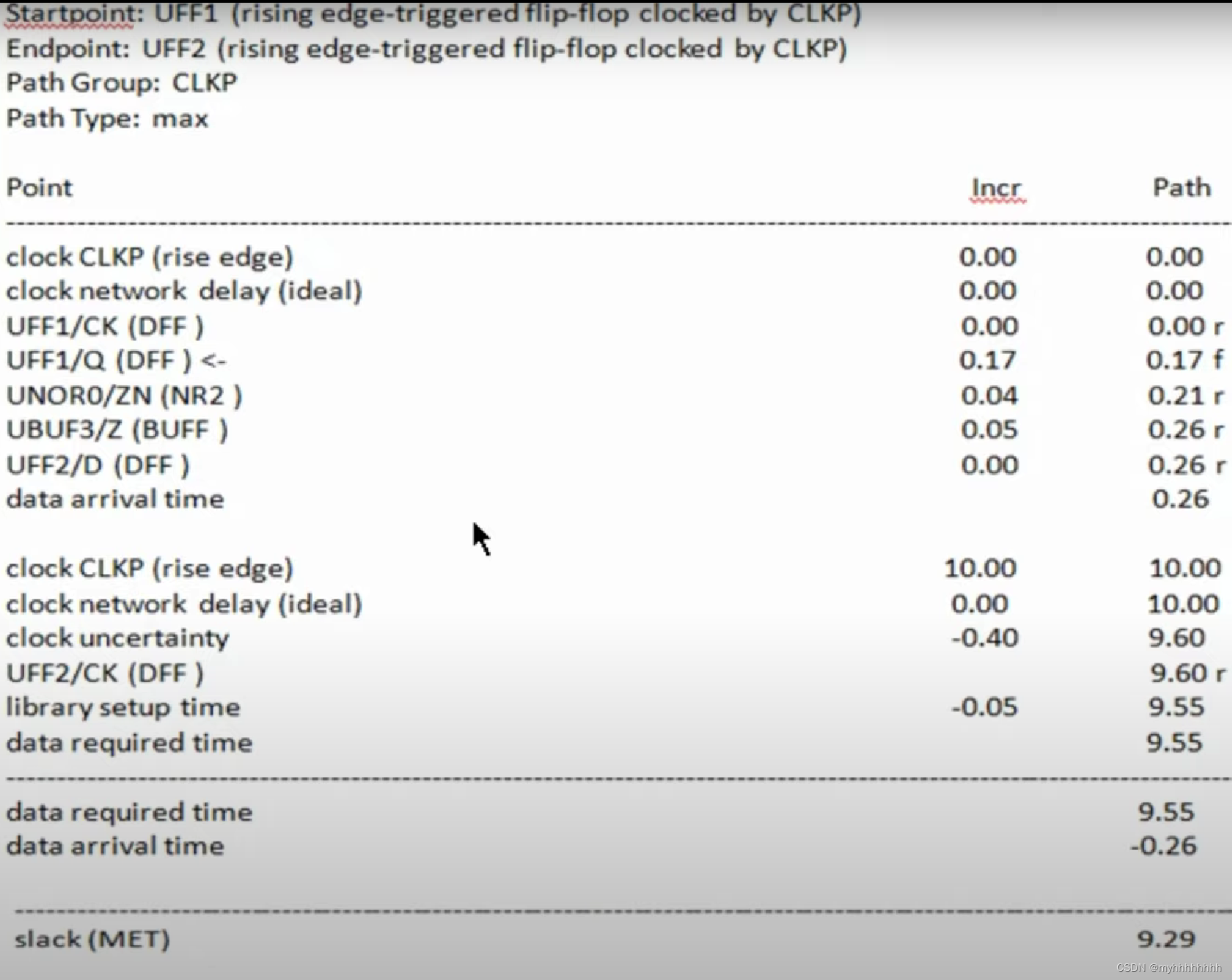

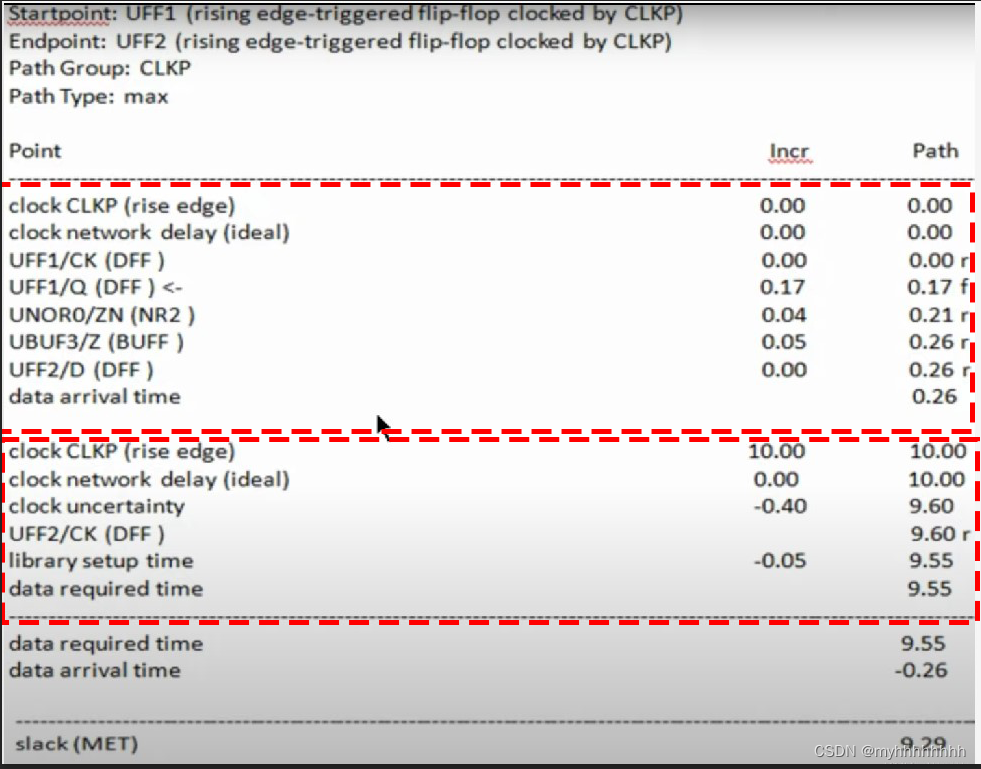

上面的电路图为一个典型的同步电路,包含组合逻辑和时序逻辑,是一个经典的时序分析案例,我们可以在其中找到静态时序分析简明教程(二)基础知识:建立保持时间,违例修复,时序分析路径所包含的全部的四条时序路径。对该电路进行分析,我们可以得到如下的时序报告,接下来就让我们看看这个报告中包括什么内容。

2.1 起始点与终止点

拿到timing report,我们第一个可以得到的信息就是时序分析路径的起点与终点。

在这份timing report中,Start Point为:UFF1的clk端;而Endpoint为:UFF2的clk端

2.2 路径时钟域的归属

除了起始点与中止店外,我们还能得到路径时钟域的归属,为CLKP,需要注意的是:起点的时钟和终点的时钟有可能不相同,但无论哪种情况,路径组合(Path Group)总是被归属于终点寄存器的时钟

2.2 建立时间检查与保持时间检查

建立时间的检查可以确保移动最慢的数据也能及时到达并满足建立的标准,因此,它又被称为最大分析(max analysis)。由于建立检查考虑了最晚到达的数据,所以也被称为晚期分析(late analysis)

保持时间的检查可以确保即使是移动最快的数据也不应该干扰其他数据,同时期望数据保持稳定。因此,数据路径计算最小延迟,被称为最小分析(min analysis)由于保持检查考虑了最早到达的数据,所以也称其为早期分析(early analysis)

本Timing Report中,Path Type为max,说明了这个是一个建立时间检查相关的时序报告,假如Path Type为min的话,就是一个保持时间检查相关的寄存器。

2.3 解读表头

表头有三项内容,分别是Point,Incr和Path。

Point代表着时序分析的点是哪一个,比如其中的”UFF1/CK(DFF)“就是第一个寄存器的clock端。

Incr为incremental delay,代表着一个分立的delay值,比如说经过组合逻辑的门电路,和寄存器的D到Q,都会产生各自的incr值。

Path为Path delay,是Incr delay的累加和。

2.4上升沿检查与下降沿检查

在Path端,我们可以发现一列数字,0.00、0.17f、0.26r,其中的f就是下降沿检查,r是上升沿检查

2.5 数据所需时间与时序违例

整个表格笼统上可以分为上下两部分,上半部分为data到达的时间,下半部分为data需要的时间,是否发生违例(建立时间违例与保持时间违例),用下面的时间减去上面的时间可以得到slack值,假如slack是正值,时序违例没有发生,假如slack是负值,说明发生了时序违例,需要按照第二节的方法去修改建立时间或者保持时间

三、总结

本文中,我们梳理了有关timing report的内容,介绍内容中,判断违例发生的条件,判断是建立时间检查还是保持时间的检查,为重中之重,和第二节的建立时间与保持时间公式一起,作为笔试中经常出现的内容对求职者予以考察,而在下一篇文章中,我们将从时钟信号开始讲起,讨论STA的具体约束内容。