目录

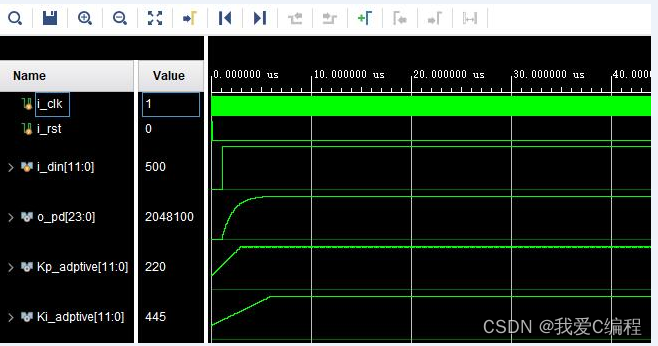

1.算法仿真效果

这个是PI控制器,非PID控制器。

vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

PID控制器(比例-积分-微分控制器),由比例单元 P、积分单元 I 和微分单元 D 组成。通过Kp, Ki和Kd三个参数的设定。PID控制器主要适用于基本线性和动态特性不随时间变化的系统。

PID 控制器的方块图PID 控制器是一个在工业控制应用中常见的反馈回路部件。这个控制器把收集到的数据和一个参考值进行比较,然后把这个差别用于计算新的输入值,这个新的输入值的目的是可以让系统的数据达到或者保持在参考值。和其他简单的控制运算不同,PID控制器可以根据历史数据和差别的出现率来调整输入值,这样可以使系统更加准确,更加稳定。可以通过数学的方法证明,在其他控制方法导致系统有稳定误差或过程反复的情况下,一个PID反馈回路却可以保持系统的稳定。

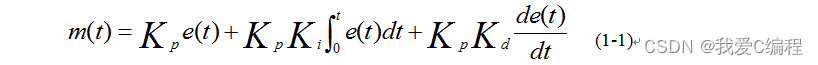

具有比例-积分-微分控制规律的控制器,称PID控制器。这种组合具有三种基本规律各自的特点,其运动方程为:

由此可见,当利用PID控制器进行串联校正时,除可使系统的型别提高一级外,还将提供两个负实零点。与PI控制器相比,PID控制器除了同样具有提高系统的稳态性能的优点外,还多提供一个负实零点,从而在提高系统动态性能方面,具有更大的优越性。因此,在工业过程控制系统中,广泛使用PID控制器。PID控制器各部分参数的选择,在系统现场调试中最后确定。通常,应使积分部分发生在系统频率特性的低频段,以提高系统的稳态性能;而使微分部分发生在系统频率特性的中频段,以改善系统的动态性能。

自适应PID控制,是指自适应控制思想与常规PID控制器相结合形成的自适应PID控制或自校正PID控制技术,人们统称为自适应PID控制。

最常用的自适应控制算法有:最小方差自适应PID控制、极点配置自适应PID控制和零极点对消的自适应PID控制。

最小方差自适应PID控制的基本思想是:在每个采样周期,以系统偏差的最小方差极小化为性能指标进行系统品质评价,通过引入在线辨识的最小二乘算法估计未知过程参数,依此来计算各采样时刻的自适应PID控制量u(t)。

极点配置自适应PID控制的基本思想是:按照某种优化策略选择期望闭环极点分布,在每个采样周期,通过加权递推最小二乘法显式地估计过程参数,并结合PID控制规律,求得含未知参数q0、q1和q2的系统闭环方程,然后利用系统特征多项式与期望特征多项式的恒等关系即可在线求得PID控制参数,进而求得各时刻控制器输出u(t)。

零极点对消自适应PID控制的基本思想是:当被控过程参数未知时,在每个采样周期,利用加权递推最小二乘算法显式地辨识过程模型,在以PID控制器传递函数中的零极点对消被控过程传递函数中的部分极零点,由此计算出各时刻的PID控制量,以使得闭环系统运行于良好的工作过程。

3.Verilog核心程序

.............................................................

input i_clk;

input i_rst;

input signed[11:0]i_din;

output signed[23:0]o_pd;

output signed[11:0]Kp_adptive;

output signed[11:0]Ki_adptive;

reg signed[11:0]o_error;

.............................................................

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_error <= 12'd0;

end

else begin

o_error <= i_din-o_pd[23:12];

end

end

//KP

reg signed[23:0]dat1;

reg signed[23:0]dat1d;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

dat1 <= 24'd0;

dat1d<= 24'd0;

end

else begin

dat1 <= o_error*Kp;

dat1d<= dat1;

end

end

//KI

//KI

reg signed[23:0]dat3;

reg signed[23:0]dat3d;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

dat3 <= 24'd0;

dat3d <= 24'd0;

end

else begin

dat3d <= o_error*Ki + dat3;

if(dat3d[23:22] == 2'b01 | dat3d[23:22] == 2'b11)

dat3d <= dat3d;

dat3 <= dat3d;

end

end

assign o_pd = dat1d + dat3d;

endmodule

A9814.完整算法代码文件

V