目录

1、前言

FPGA实现CameraLink视频编解码目前有两种方案:

一是使用专用编解码芯片,比如典型的DS90CR287;另一种方案是使用FPGA实现编解码,利用FPGA的serdes资源实现解串,优点是合理利用了FPGA资源,serdes资源不用白不用,缺点是操作难度大一些,对FPGA水平要求较高。

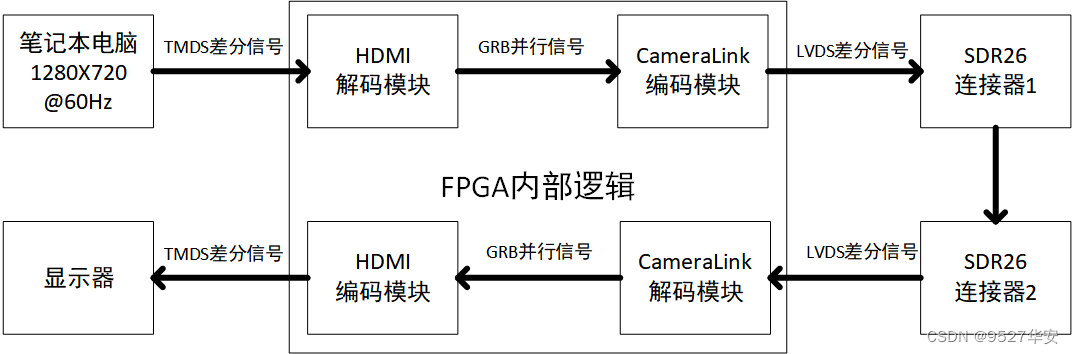

本文详细描述了FPGA纯verilog实现CameraLink视频接收和发送的实现设计方案,目的在于验证CameraLink解码模块和编码模块的正确性,思路是这样的,由于项目之处没有CameraLink相机,但又必须验证关键的CameraLink解码模块和编码模块,所以做了这样一个巧妙的设计:

先采集HDMI输入视频,经HDMI解码模块解为RGB数据后送入CameraLink编码模块,出来的就是CameraLink的LVDS差分视频信号了,再把这个信号通过CameraLink视频输出接口回环到CameraLink视频输入接口,这样FPGA又接受到了CameraLink的LVDS差分视频信号了,再把这个信号送入CameraLink解码模块,解为RGB视频,最后经过HDMI编码模块输出显示器显示;如此一来,输入和输出都是HDMI视频,却同时验证了CameraLink解码模块和编码模块,却输出效果可通过显示器直观查看,可谓相当精巧的方案,呵呵。。。

工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2、CameraLink协议基础

关于这部分,网上有很多博主解释过,我找了几篇推荐兄弟们去学习理论知识:

第一篇链接:点击直接前往

第二篇链接,这是我之前写的:点击直接前往

3、目前我已有的CameraLink收发工程

我的CameraLink视频专栏有很多FPGA的CaeraLink视频编解码方案,既有CaeraLink接收,也有CaeraLink发送,既有CaeraLink普通输出显示,也有CaeraLink视频拼接输出等等,专栏链接如下:欢迎前往查看:点击直接前往

4、设计方案

详细设计方案如下:

这个方案不需要有CameraLink相机,但你的板子需要有CameraLink相机接口或者有单独的具有CameraLink相机接口的转接板,具体流程如下:

视频输入:

用笔记本电脑模拟视频输入,将笔记本电脑分辨率设置为1280x720@60Hz;

HDMI解码模块:

输入为TMDS的差分视频信号,也就是HDMI视频信号,输出并行的RGB数据,即标准的VGA视频时序;这个视频作为CameraLink编码模块的输入;

CameraLink编码模块:

输入为RGB视频数据,输出为CameraLink的LVDS差分视频信号,这个信号通过CameraLink视频接口输出;

CameraLink视频接口:标准的SDR26连接器,一共两个,一个作为输出,另一个作为输出入;

CameraLink编码模块:

输入为CameraLink的LVDS差分视频信号,输出为并行的RGB数据,即标准的VGA视频时序;这个视频作为HDMI编码模块的输入;

HDMI编码模块:

输入为RGB视频,输出为TMDS差分视频,输出HDMI显示器显示;

5、CameraLink解码模块详解

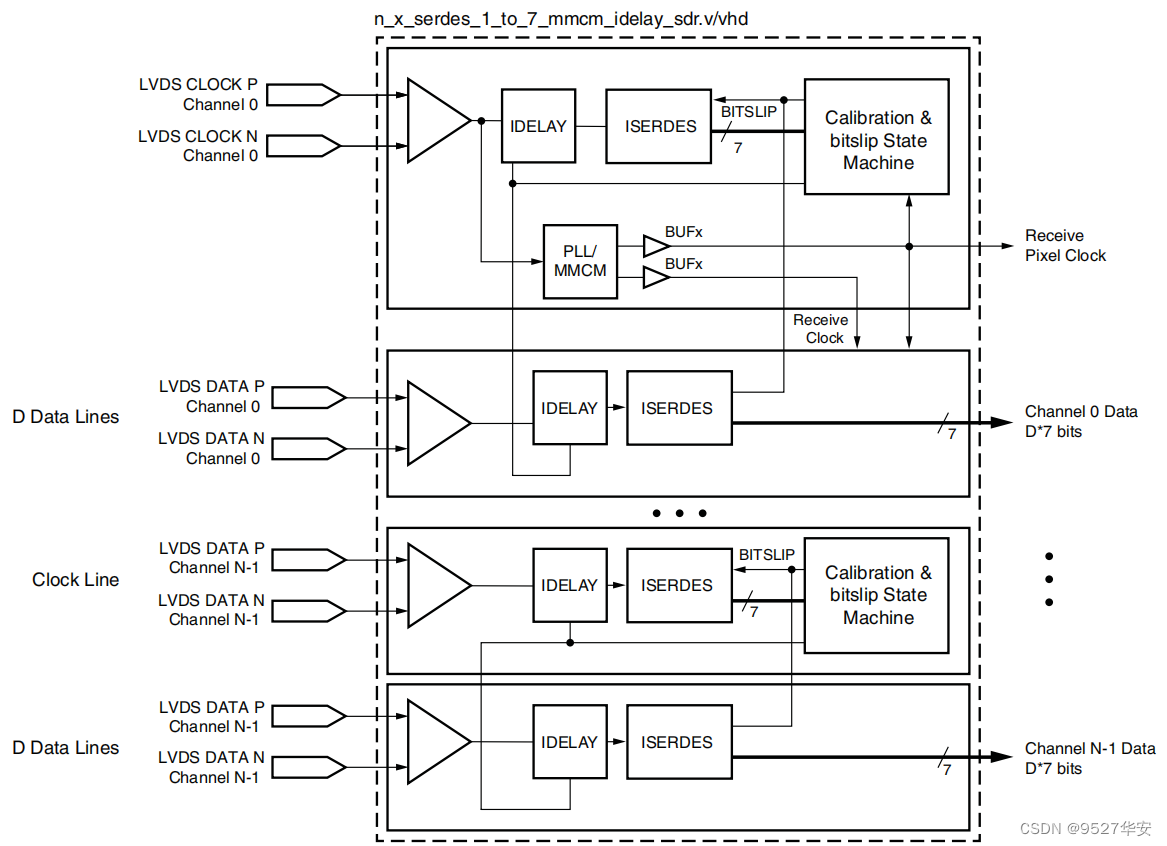

CameraLink解码模块设计框图如下:

CameraLink解码模块输入信号如下:

1路差分时钟,4路差分数据;利用Xilinx官方的IDELAY和ISERDES源语实现串并转换;

IDELAY源语的作用是延时,以便于FPGA采样时的CameraLink视频数据是稳定的;

ISERDES源语的作用是实现CameraLink视频数据的串并转换;

整个CameraLink解码模块严格按照设计框图实现,主要是调用源语,所以没啥可讲的,具体看代码,代码量很少;

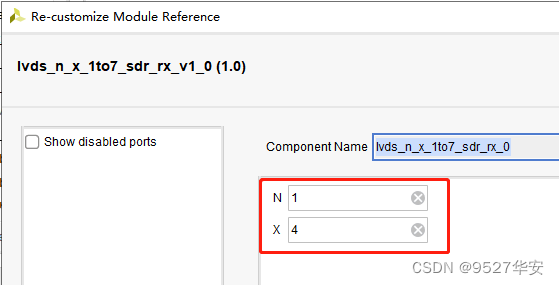

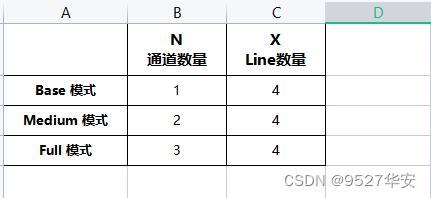

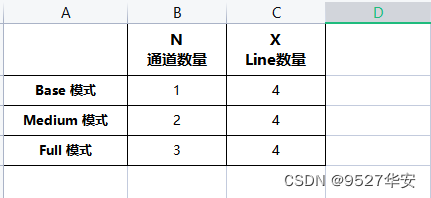

CameraLink解码模块参数配置如下:

这两个参数可自由配置,以适应CameraLink相机的不同模式;具体配置如下:

当前配置的模式适用于Base模式;

6、CameraLink编码模块详解

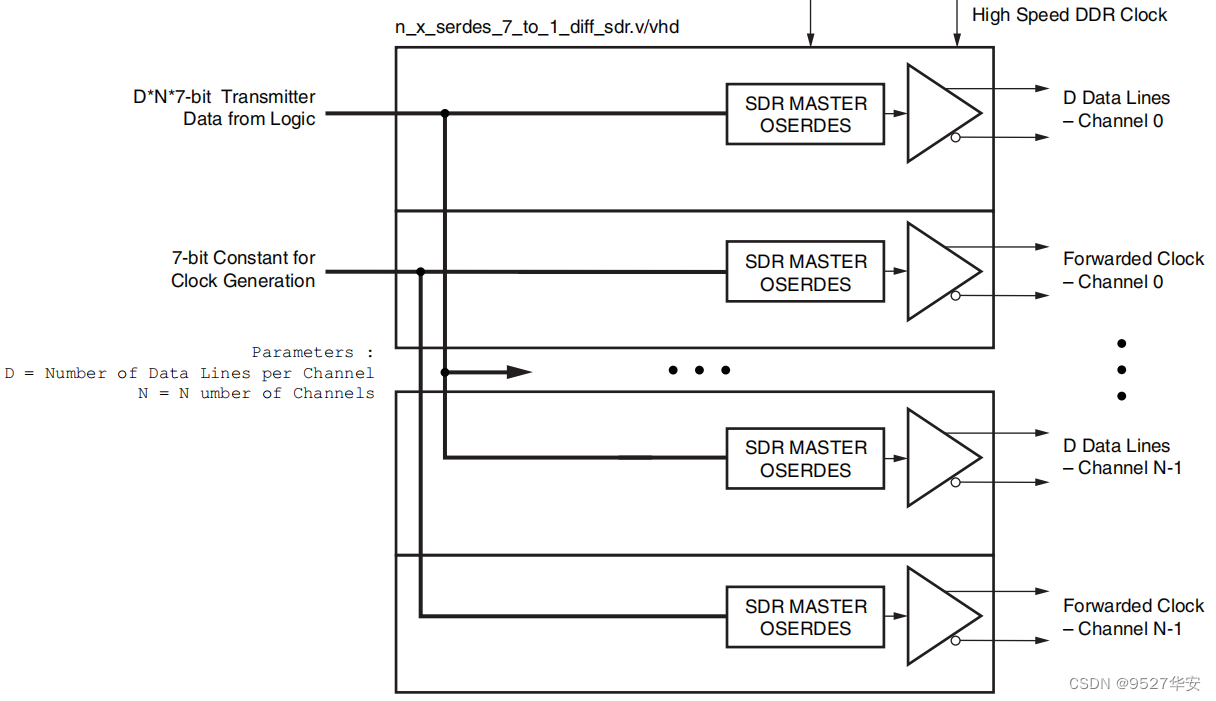

CameraLink编码模块设计框图如下:

CameraLink编码模块是解码的逆过程,输入信号如下:

1路单端时钟,并行的像素数据;利用Xilinx官方的OSERDES源语实现并串转换;

作为编码,不需要IDELAY源语的延时;

OSERDES源语的作用是实现CameraLink视频数据的并串转换;

整个CameraLink编码模块严格按照设计框图实现,主要是调用源语,所以没啥可讲的,具体看代码,代码量很少;

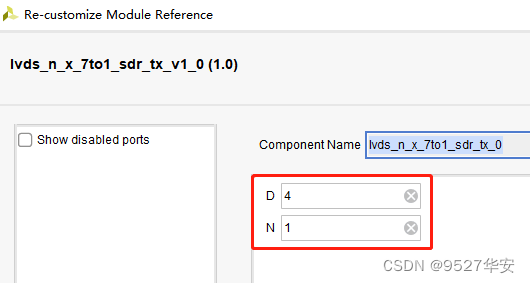

CameraLink编码模块参数配置如下:

这两个参数可自由配置,以适应CameraLink相机的不同模式;具体配置如下:

当前配置的模式适用于Base模式;

7、vivado工程详解

开发板FPGA型号:xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:HDMI,作为CameraLink编码模块的输入;

输出:HDMI,实质上是CameraLink解码模块的输出;

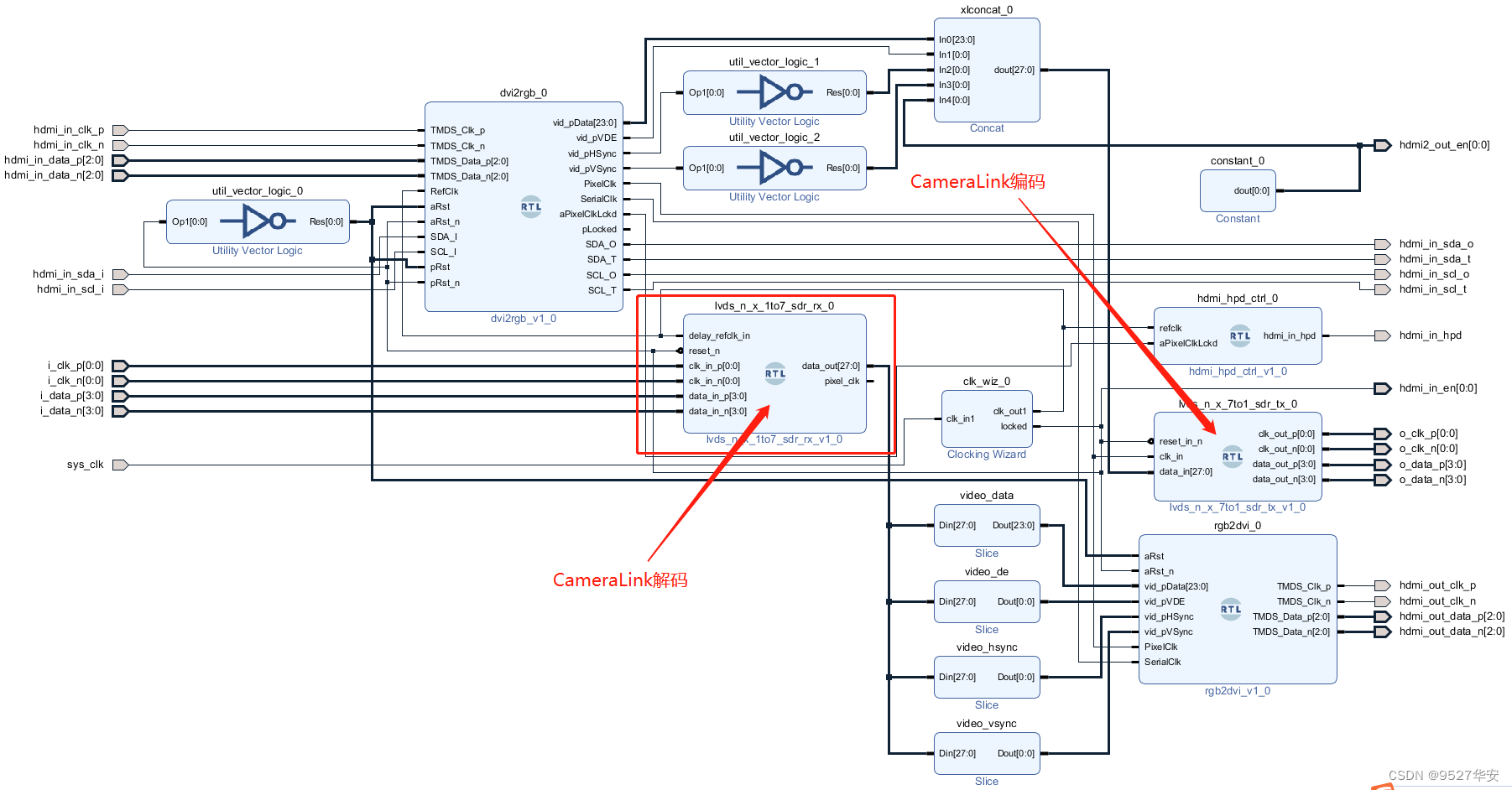

Bolck Design设计如下:

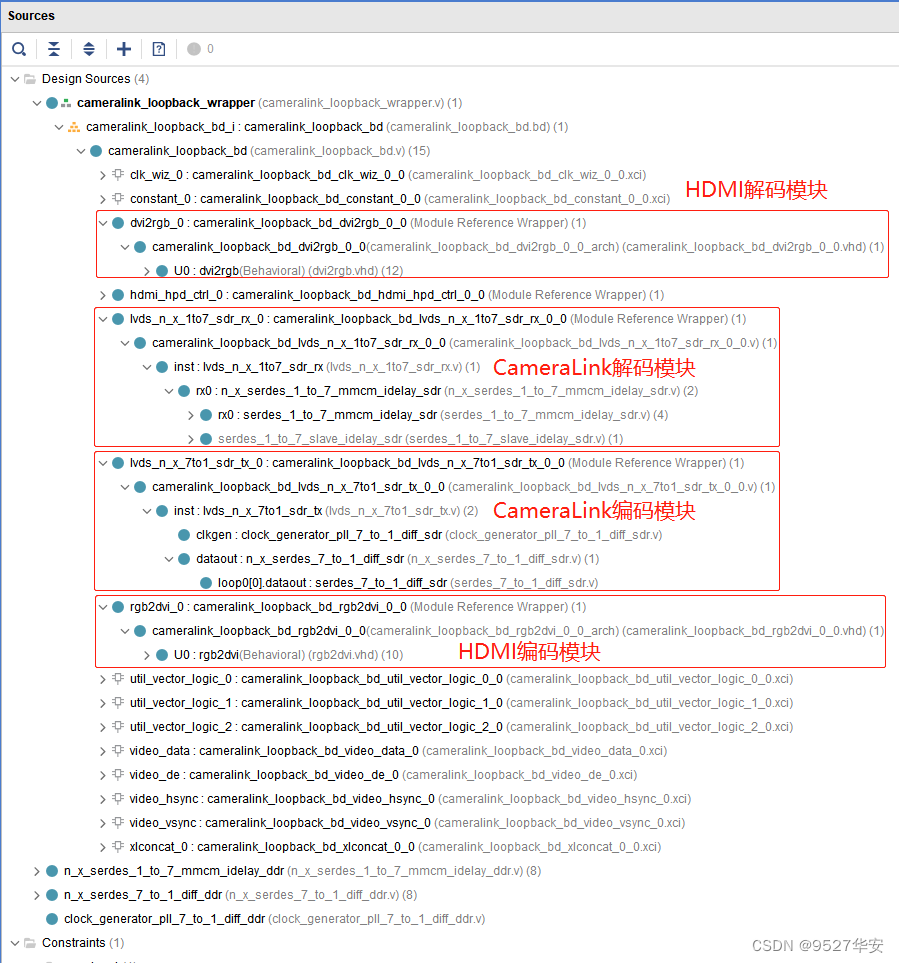

综合后的工程代码架构如下:

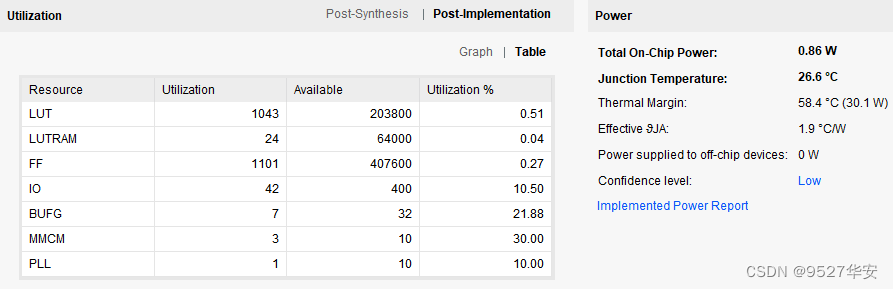

综合编译完成后的FPGA资源消耗和功耗预估如下:

8、上板调试验证

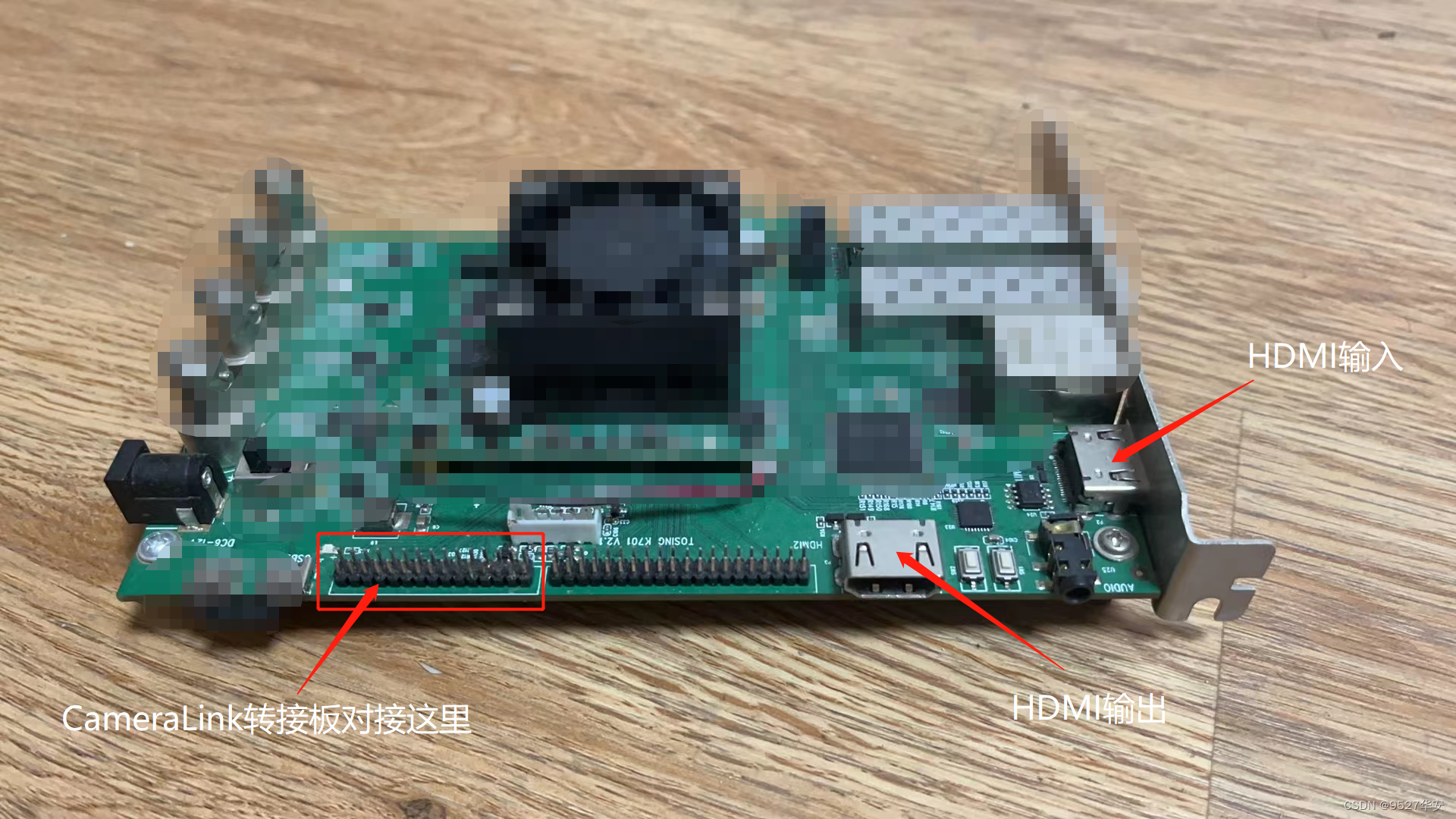

由于CamerLink转接板不方便出境,仅展示FPGA板子及对应的CamerLink转接板接口,如下:

输出效果如下:

9、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式1:私,或者文章末尾的V名片。

网盘资料如下: