文章简介

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第十六章:SPI

SPI简介

上一节讲解了SPI接口的协议以及时序内容,本节在上节的基础上,以Flash型号为M25p64为例,通过SPI总线控制Flash讲解擦除功能的实现。

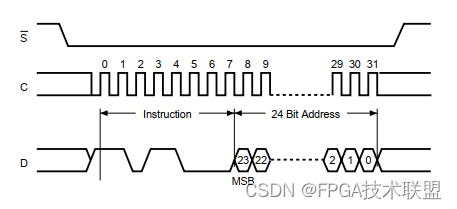

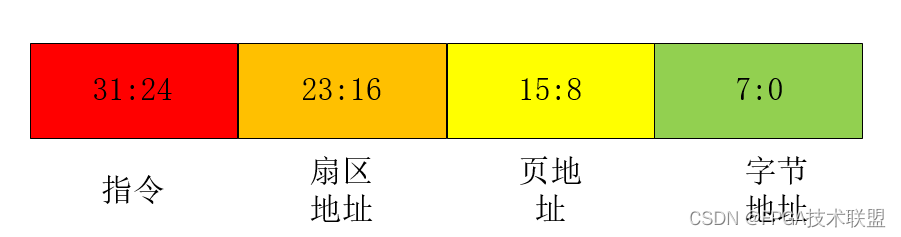

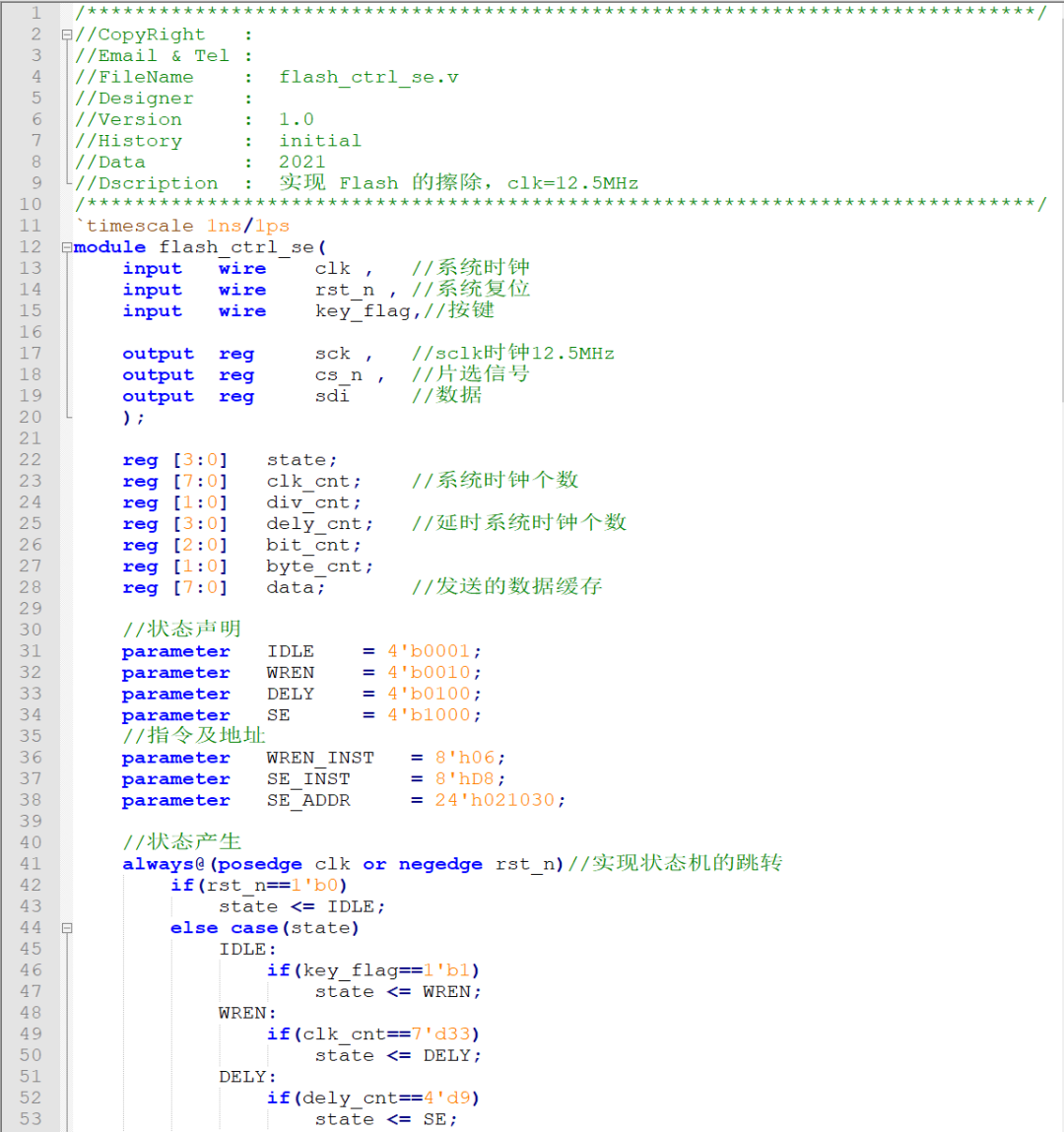

M25p64

M25p64 是意法半导体公司的 flash, 其最大的时钟频率为 50Mhz, 在此我们进行擦除时采用 12.5Mhz 的时钟,即 sck 的时钟频率为 12.5Mhz。 该款 Flash 芯片的存储空间为 64Mbit, 每个地址内存储 1byte(8bit) 的数据, 共 8M 的存储深度, 其地址分为 128 扇区(sector)、每个扇区包含 256 页(page)、每一页包含256 字节(byte), 因此该 Flash 芯片需要用到 23 位地址线, 加上扩展的 1bit 地址线,一共用到 24bit 地址线,具体如下图 所示。

在对 Flash 进行写入数据时,首先需要将 Flash内部现有的数据进行擦除, Flash 的擦除分为扇区擦除(sector erase) 和全擦除(bulk erase), 下面将以扇区擦除为例进行讲解。

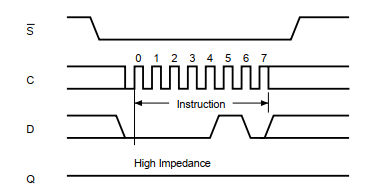

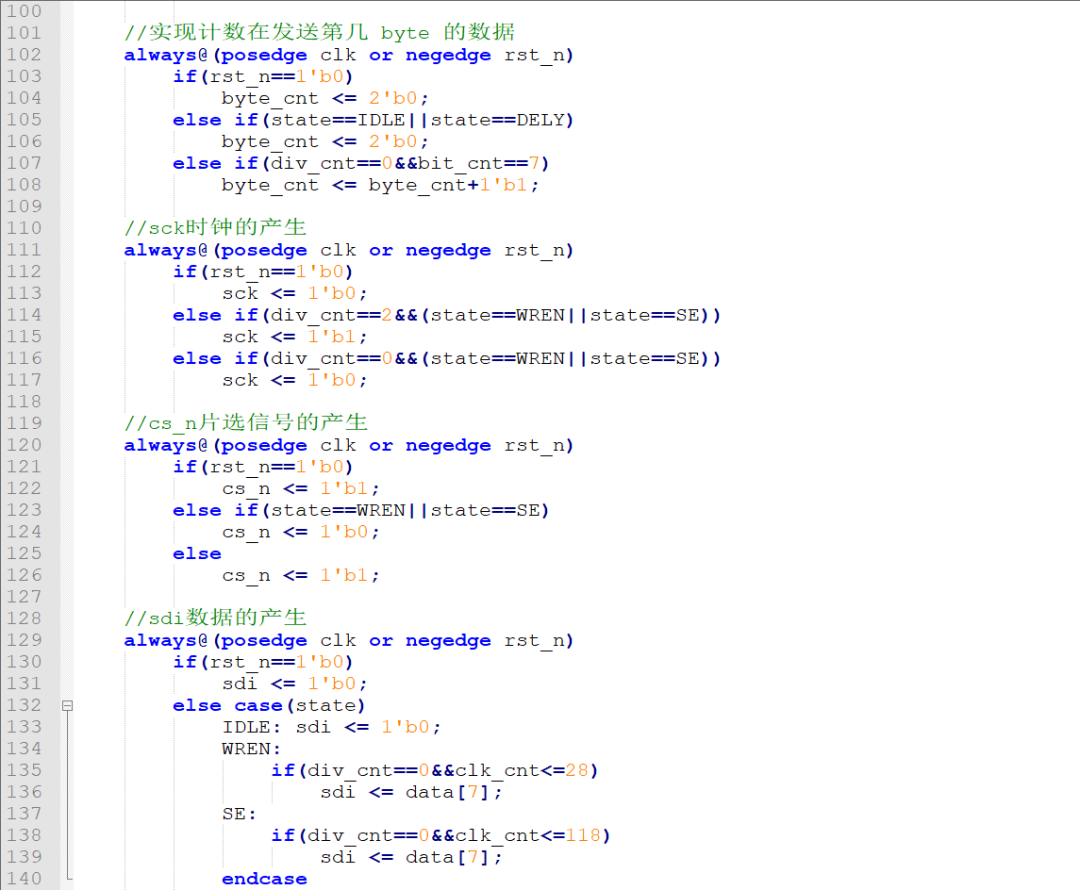

扇区擦除又称为 SE(Sector Erase), 在进行 SE 之前需要给出一个写使能指令(WREN), 然后进行扇区擦除。 写使能指令(WREN) 波形图如图 3 所示, 首先需要将 cs_n 置为低, 然后产生 12.5Mhz 的时钟 sck, Flash 会根据 sck 的上升沿锁存 sdi 的数据,因此我们给出的 sdi 的每一位最好都能被 sck 的上升沿采集到稳定的时刻, 即sck的上升沿对着sdi每一位数据的中心位置, WREN的指令为8’h06。由于在 WREN 状态下我们只需要发送 8bit 数据,因为只需要产生 8 个可以锁存sdi 数据的 sck 上升沿即可,在确定 sdi 数据被锁存结束后,我们就可将 cs_n 拉高。

WREN 波形图

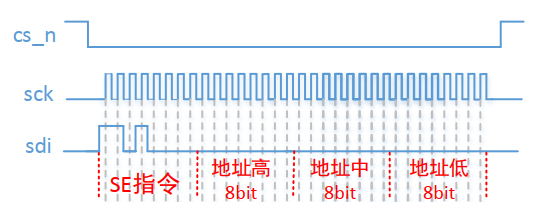

在 WREN 结束后, cs_n 需要被拉高, 为了确保 WREN 被 Flash 存储,因此 cs_n拉高的时间至少需要 100ns, 之后再次拉低 cs_n 为发送 SE 指令做准备, SE 的指令波形图如图 4 所示。 首先拉低 cs_n 选中 Flash, 然后发送 SE 指令(D8h) 以及3 个 byte 的地址位,根据所发生的 bit 个数给出对应数量的 sck 上升沿,并且确保每个 sck 的上升沿都能采集到 sdi 稳定的时刻。 由于是扇区擦除,因此给出的地址位只有高 8bit 有效,低 16bit 无论是何值都对该扇区的擦除没有影响。 在给出最后 1byte 地址位后, 确保被选中的扇区可以被擦除, cs_n 需要保持至少 3 秒高电平的状态。

时序波形图

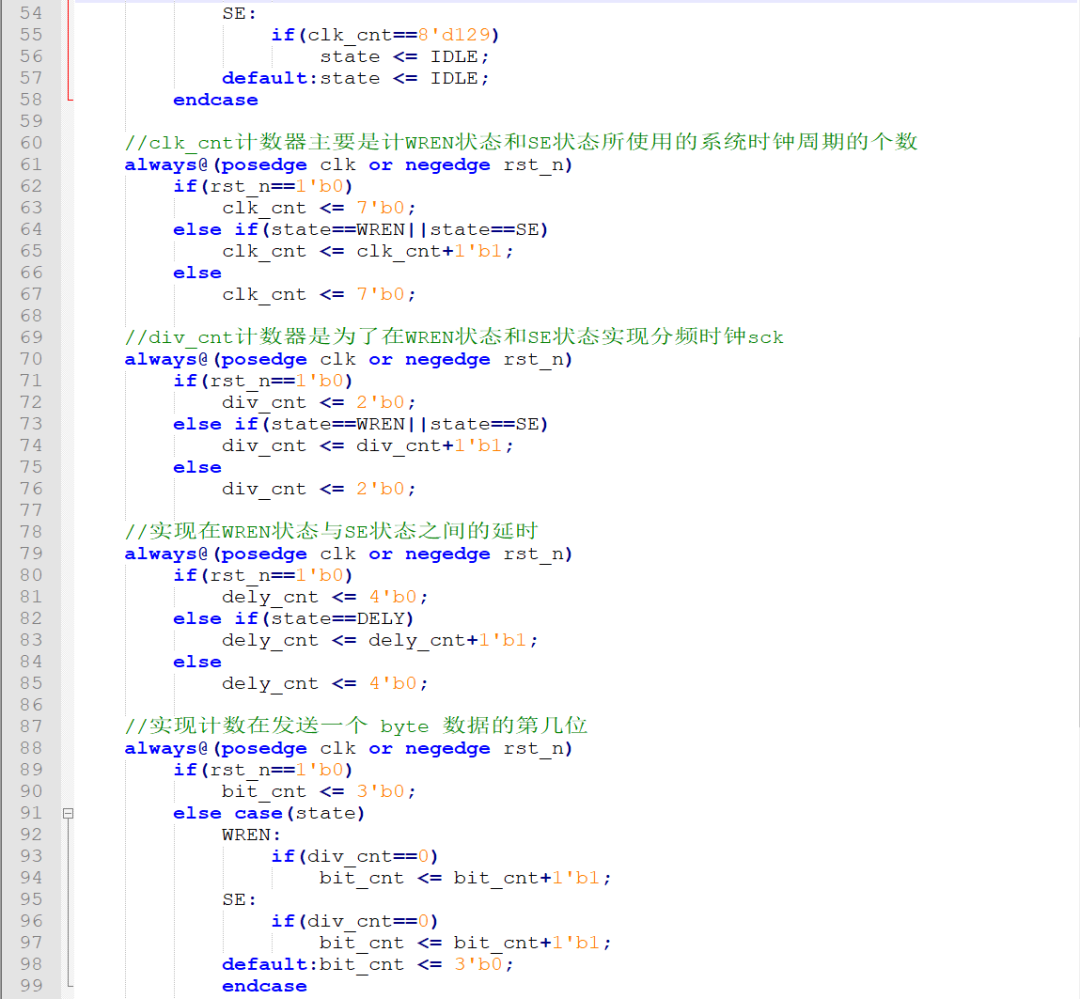

代码示例

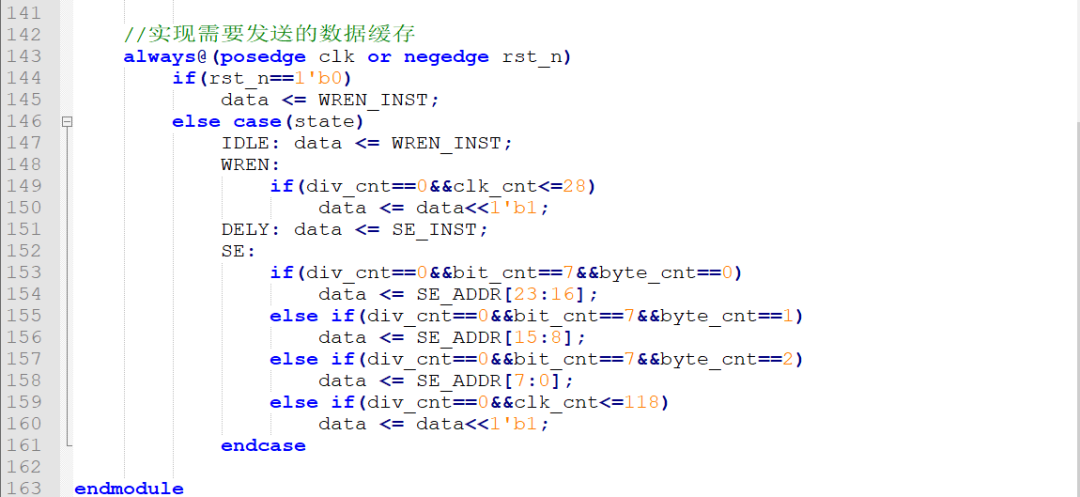

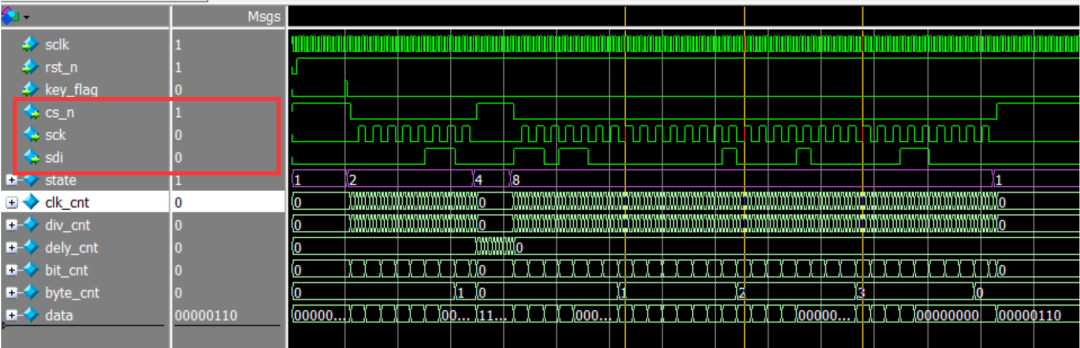

编写测试程序,测试程序比较简单,给出clk,rst_n,按键即可,仿真波形如图所示。

仿真波形示意图