问题:

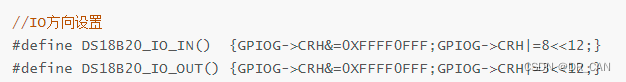

当32单片机进行引脚分配时,需要了解该程序的功能。

基础知识:

STM32 的每个 IO 端口都有 7 个寄存器来控制。他们分别是:

配置模式的 2 个 32 位的端口配置寄存器 CRL 和 CRH;

2 个 32 位的数据寄存器 IDR 和 ODR;

1 个 32 位的置位/复位寄存器BSRR;

一个 16 位的复位寄存器 BRR;

1 个 32 位的锁存寄存器 LCKR;

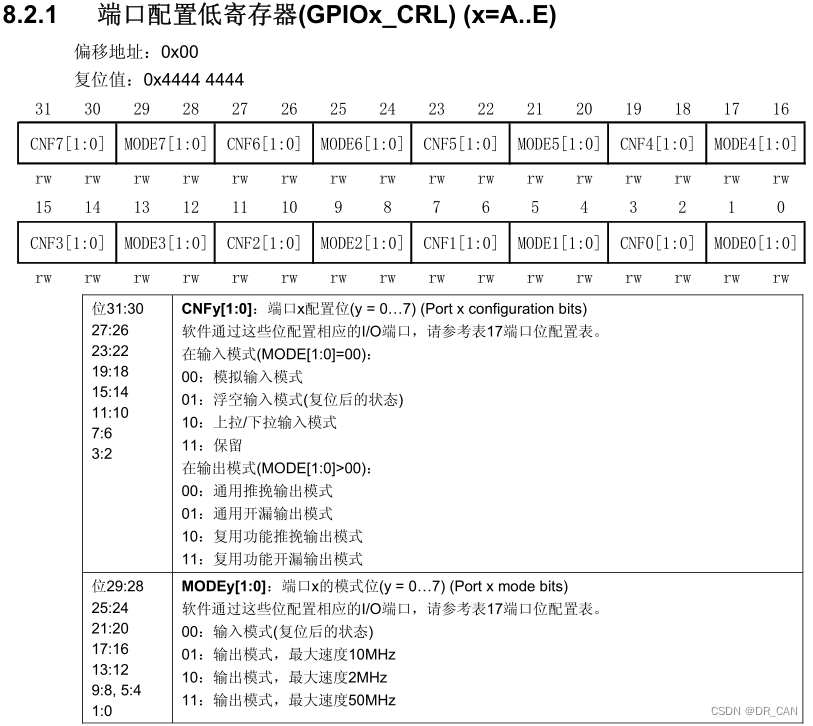

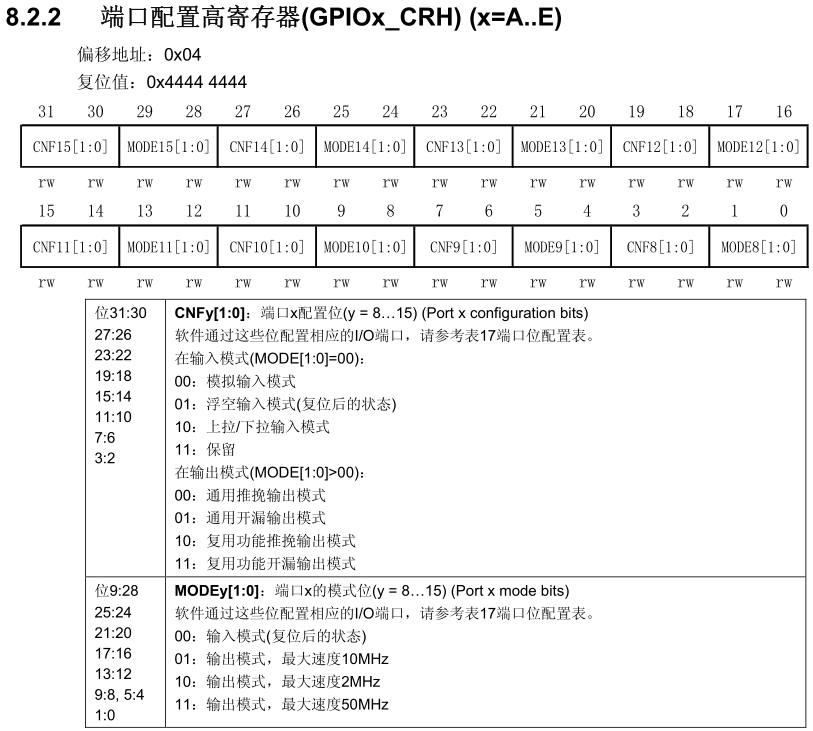

我们常用的 IO 端口寄存器只有 4 个:CRL、CRH、IDR、ODR。CRL 和 CRH 控制着每个 IO 口的模式及输出速率。

其中CRL配置规则

其中CRH配置规则

解释:

1、输入

GPIOA->CRL&=0XFFFFFFF0;GPIOA->CRL|=8<<0;

①前半段GPIOA->CRL&=0XFFFFFFF0;

利用“与”运算,把这个位清0,同时不影响其他的位的设置。

此时把PA0设置成模拟输入模式。

②后半段GPIOA->CRL|=8<<0;

意思就是将8(1000)左移0位(不移位),然后再与GPIOC->CRL进行或运算。

此时把PA0设置成上拉/下拉输入模式。

2、输出

GPIOA->CRL&=0XFFFFFFF0;GPIOA->CRL|=3<<0;

①前半段GPIOA->CRL&=0XFFFFFFF0;

利用“与”运算,把这个位清0,同时不影响其他的位的设置。

此时把PA0设置成模拟输入模式。

②后半段GPIOA->CRL|=3<<0;

意思就是将3(0011)左移0位(不移位),然后再与GPIOC->CRL进行或运算。

此时把PA0设置成通用推挽输出模式。

扩展

PA1为输入(上/下拉)

GPIOA->CRL&=0XFFFFFF0F;GPIOA->CRL|=8<<4;

PA2为输入(上/下拉)

GPIOA->CRL&=0XFFFFF0FF;GPIOA->CRL|=8<<8;

PA1为输出(通用推挽输出50MHZ)

GPIOA->CRL&=0XFFFFFF0F;GPIOA->CRL|=3<<4;

PA2为输出(通用推挽输出50MHZ)

GPIOA->CRL&=0XFFFFF0FF;GPIOA->CRL|=3<<8;

以此类推。