在之前的内容里,讲述了AXI和DDR3的基本知识,也做了一个用AXI IP核读写BRAM的测试实验。接下来,我们就将这些部分结合在一起,做一个用AXI IP核对DDR3进行读写测试的实验。因为DDR3的时序比较复杂,所以我们一般都会使用Xilinx官方提供的MIG IP核来控制DDR3,上一节简介了比较常用的Native接口的MIG IP核,而我么进这次实验是基于AXI IP核来对DDR3进行读写测试的,所以我们这次要使用的是AXI接口的MIG IP核,它的接口是满足AXI时序的,这里也不在赘述。

1 配置AXI IP核

在新建一个工程后,和第二节的方法一样,我们配置一个AXI4的IP核,操作与之前一样,可参考第二节。接下来,和之前一样,新建一个Block Design,然后将配置好的AXI IP 核添加进去。

2 配置MIG IP核

1.点击+号,添加IP核,然后搜索MIG IP核,然后双击选择这个IP核。

2.选择后在BD里会出现这样的MIG IP核。

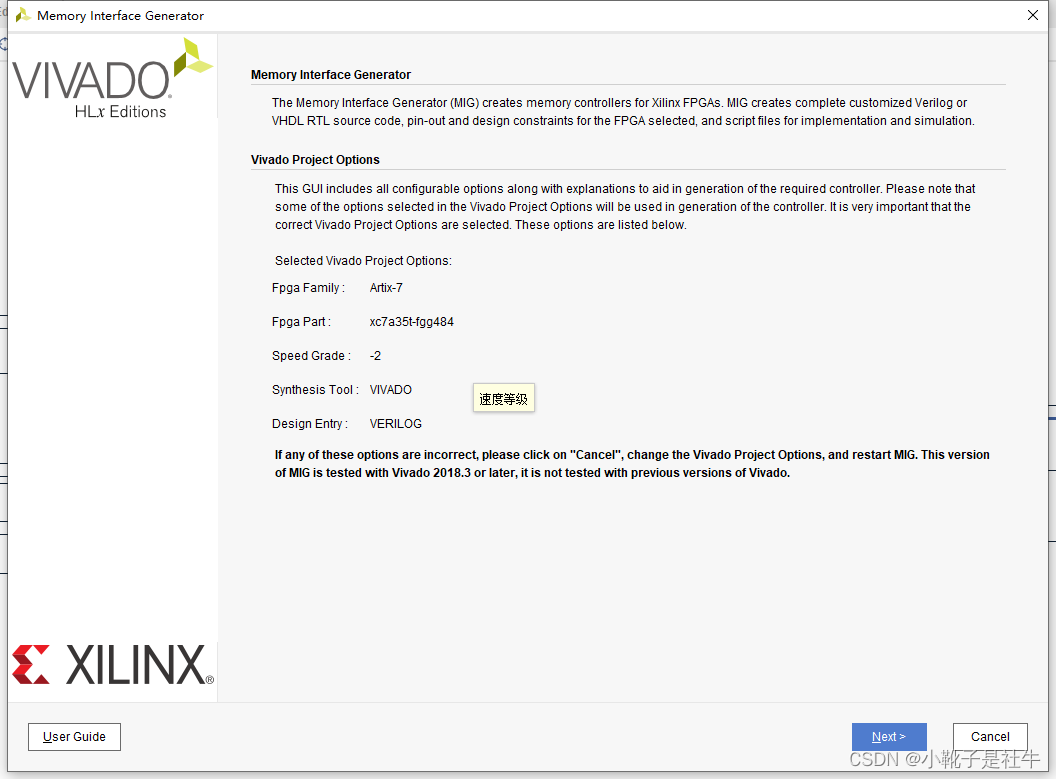

3.双击对其进行配置,会打开这个界面,点击NEXT。

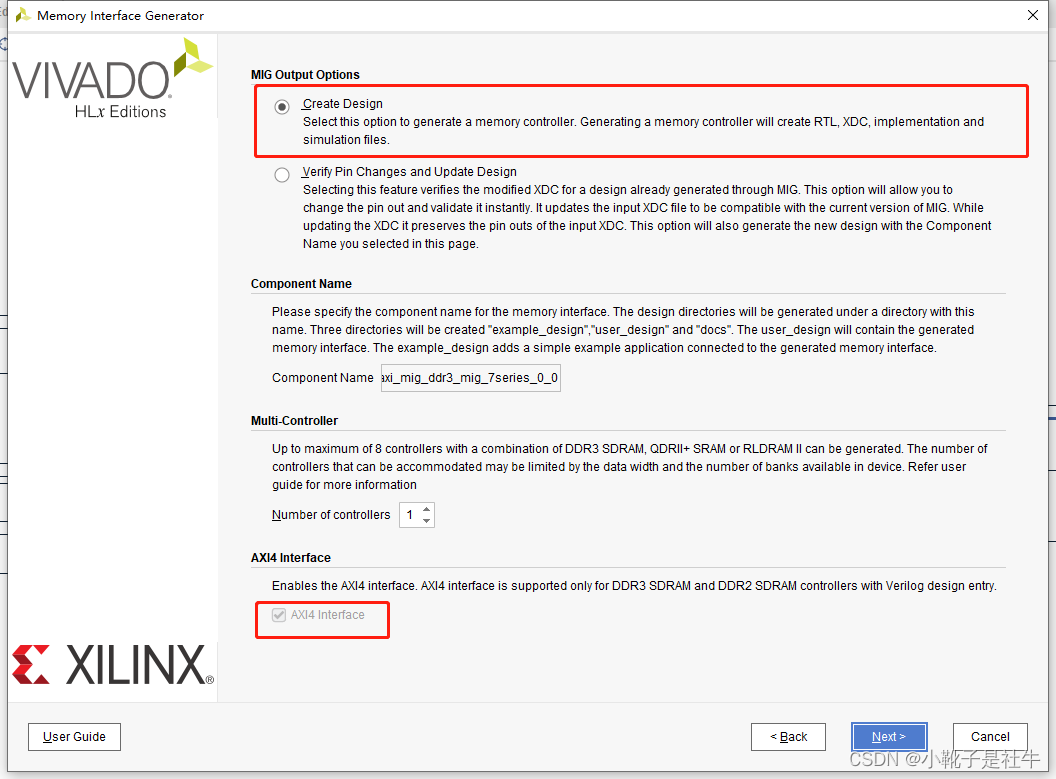

4.如图点击,创建一个MIG IP核,然后勾选AAXI4接口,控制器数目我们默认选1,然后点击NEXT。

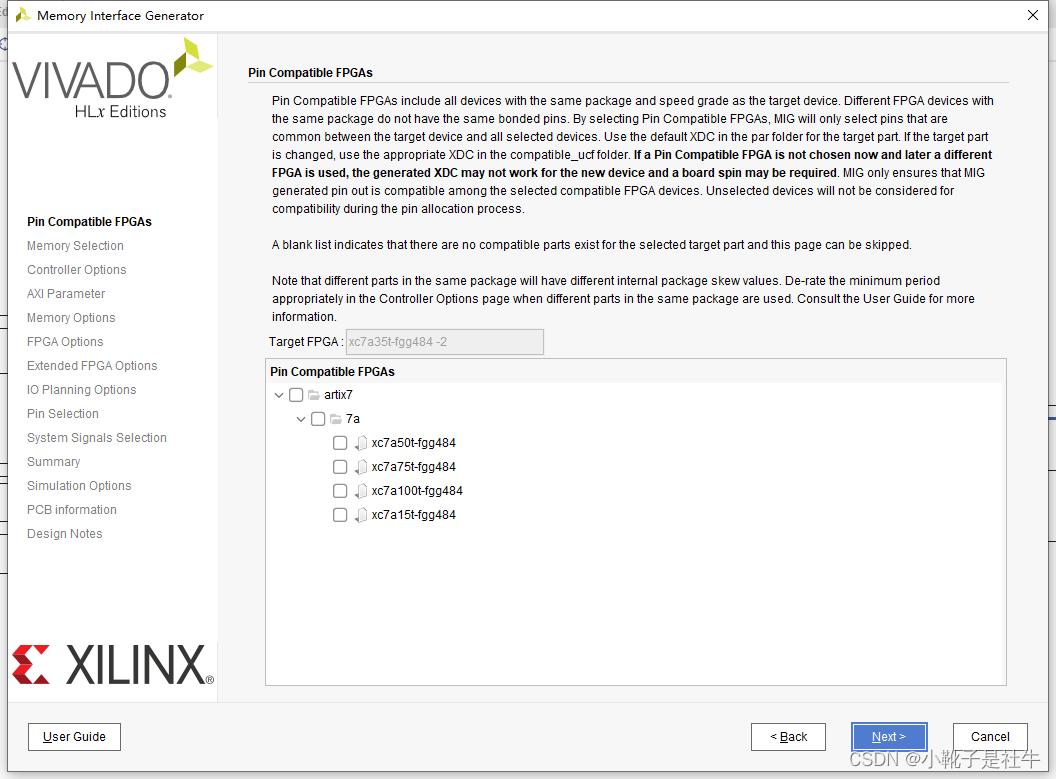

5.这个页面是选我们要兼容的芯片型号,这里不选择。

6.这里我们选择控制类型为DDR3,点击NEXT。

7.时钟周期我们选择2500ps,这个400M时钟是指DDR3的工作时钟,MIG会生成这个400M时钟给DDR3使用,同样会按照4:1的规则,生成一个100M的时钟给我们用户接口使用。第3步我们选择Components代表我们选择的内存类型是内存颗粒。因为我这边的板子是达芬奇PRO,所以第四部我是这样选择的,它具有2片256M*16的DDR3,所以它的总数据位宽就是32位,大家可以根据自己的板子型号选择。

8.因为我们的AXI IP核的数据位宽是32位,所以这里我们也配置为32位。

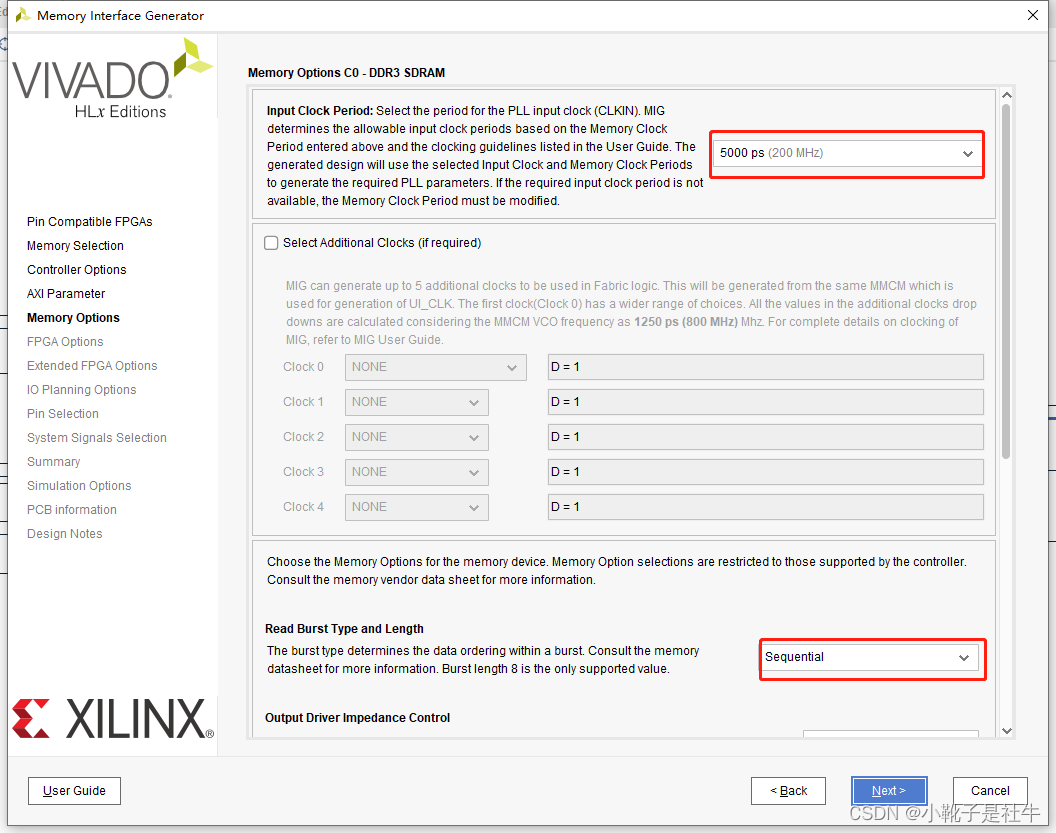

9.这里的输入时钟我们选择200MHZ,这个时钟是MIG IP核的工作时钟,突发类型选择顺序突发。

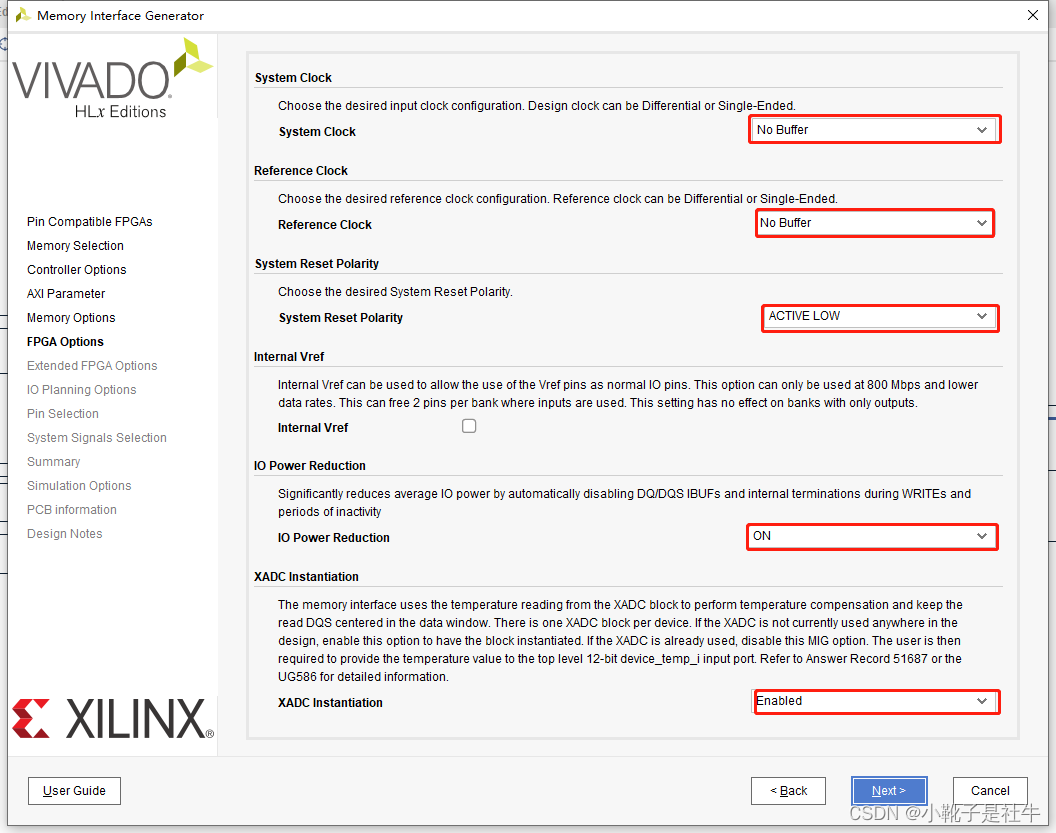

10.按照图示进行配置,因为我们使用的是FPGA的内部时钟,所以我们选择No Buffer,复位选择低有效,下边的两个选项是减小功耗和一些优化,我们都给打开。

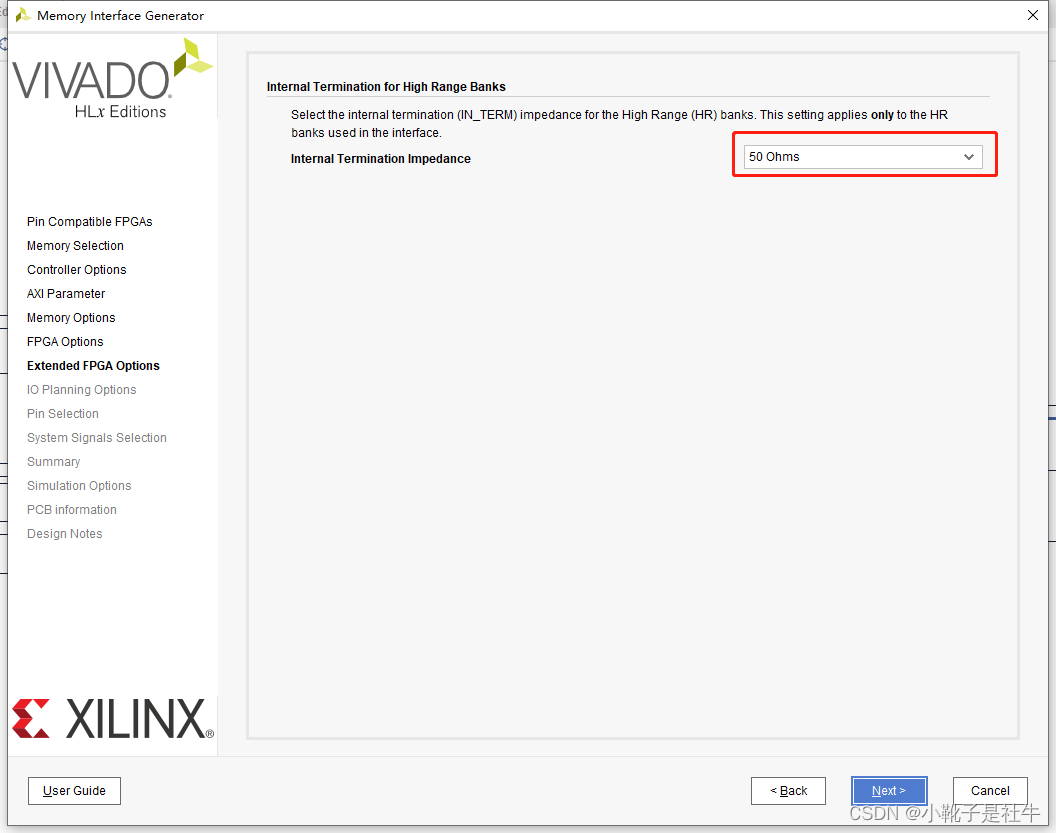

11. 这里的电阻默认不变。

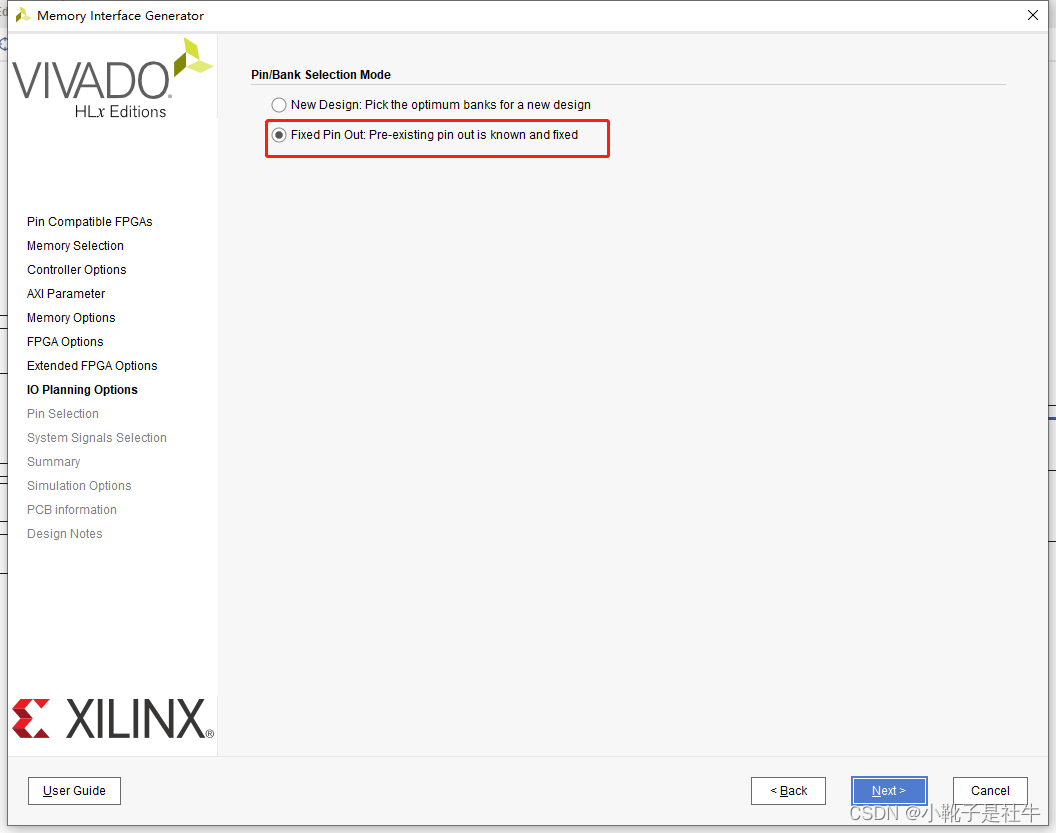

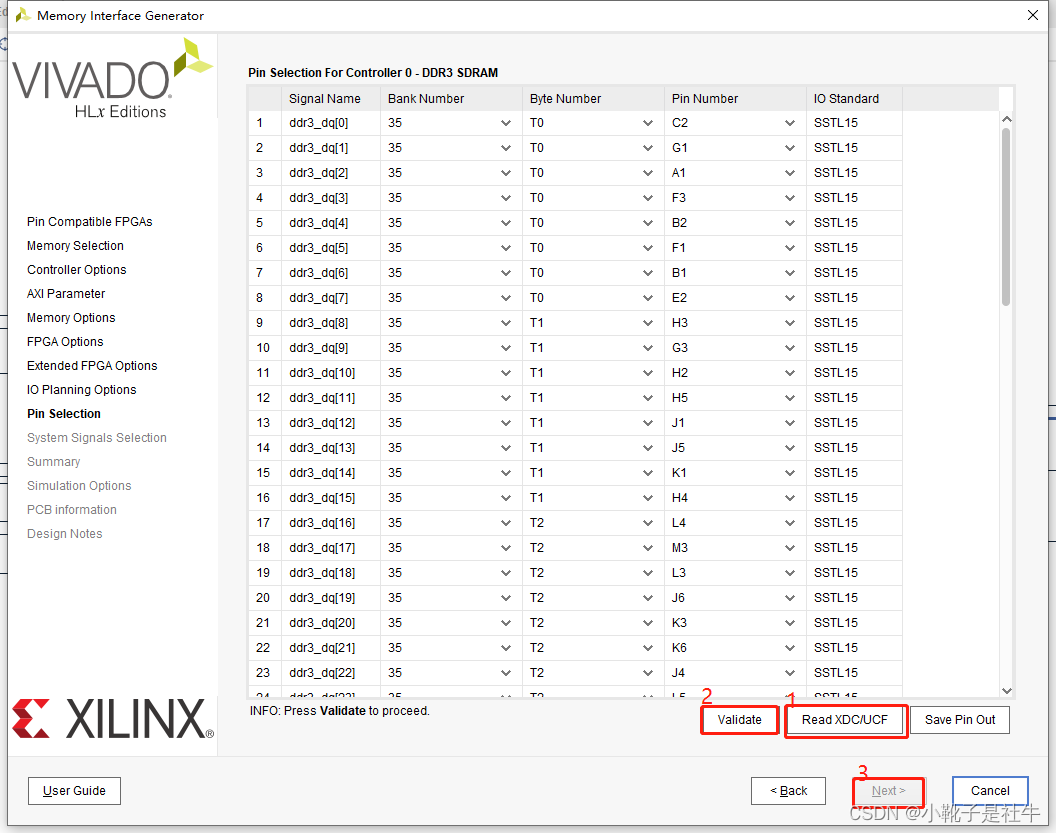

12.这里选择读入已有的管脚配置,重新绑定太麻烦。

13.将XDC文件读入后,点击验证,验证成功后点击NEXT。

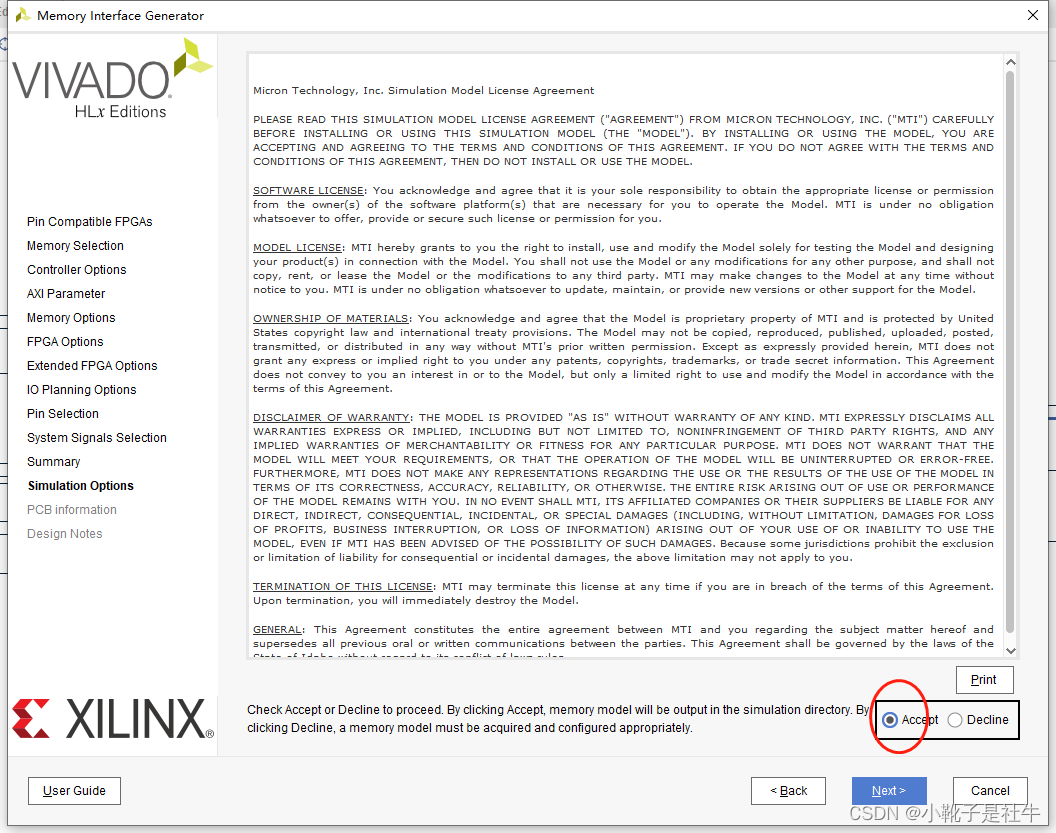

14.接下来就是一直点击NEXT,一直到这一步,选择接受协议,继续往下走。

15.然后都是一些信息,核对后生成IP核。

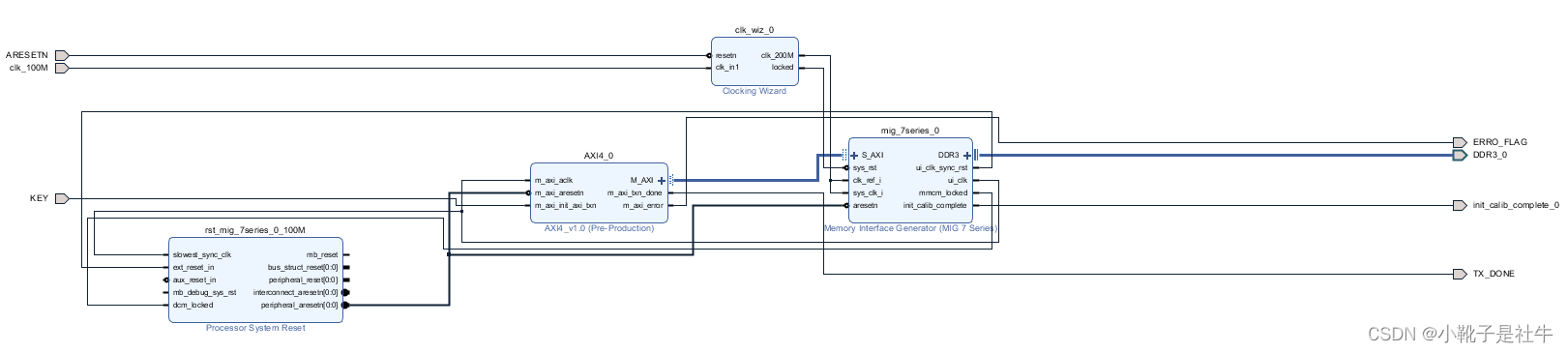

3 使用BD进行模块连接

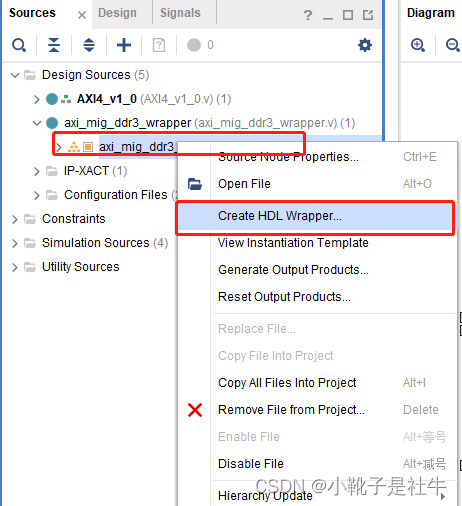

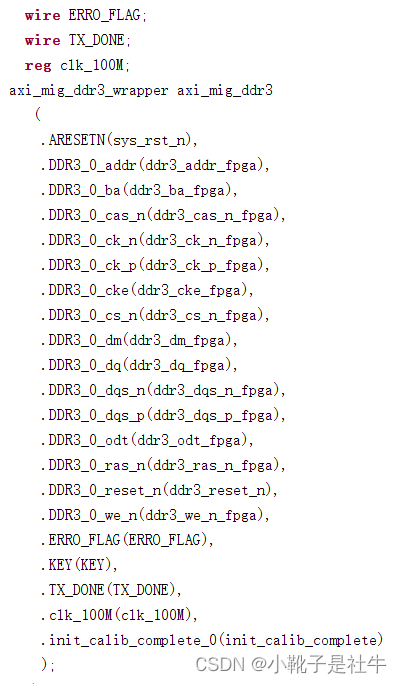

如图所示,将所有模块之间的信号都连接起来,其中的clock wizard用来生成MIG输入的200M时钟。然后F6进行检查,在检查无误之后,将这个设计打包生成我们的 .V文件。具体操作是选种我们的BD文件,右键选择Creat HDL Wrapper,就生成了我们的 .V文件。

这样,我们的设计就已将有了,接下来就是要对我们的设计进行仿真,我们使用XILINX官方给的仿真例子来修改为我们的仿真环境。

4 仿真环境

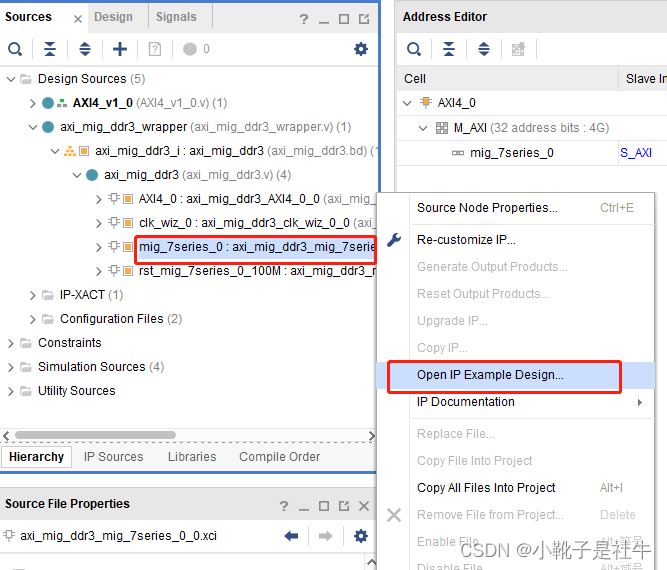

1. 我们右键选中我们的MIG IP核,然后选择Open IP Example Design。

2.这时系统会给我们生成MIG IP核的测试文件,还会给我们生成一对小模块。

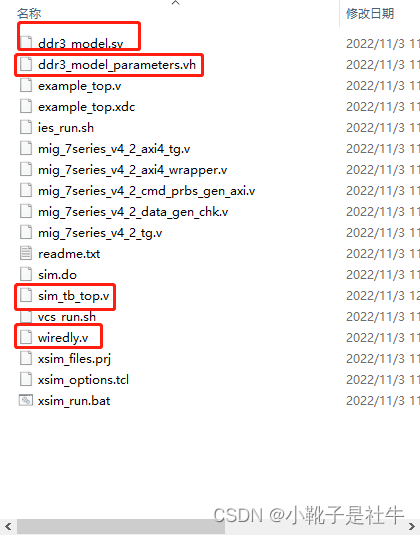

3.我们在工程根目录下新建一个import文件夹,然后将文件复制过来,如图所示。

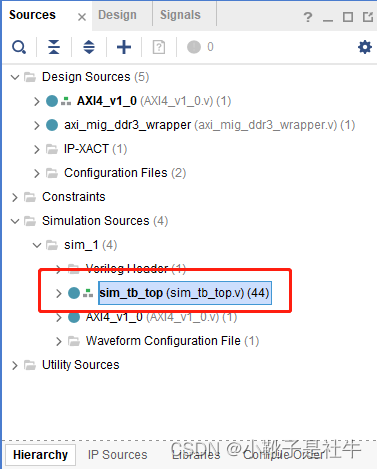

然后我们将这几个文件添加进工程里面。

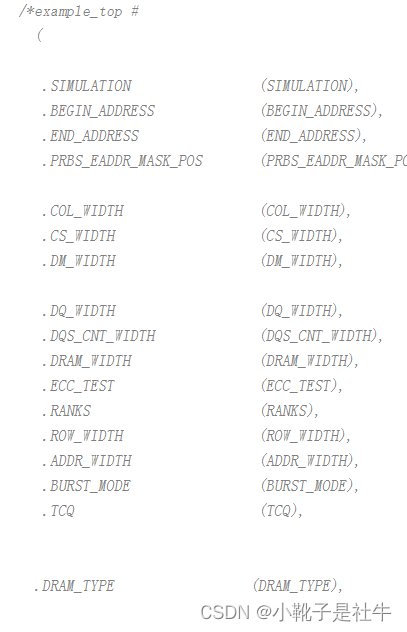

4.然后将sim_tb_top.v中的example改为我们的顶层,这样就可以使用了,我们只需要自己再生成一个100M的输入时钟给锁相环输入就可以了。在MIG初始化信号init_calib_complete拉高之后开始我们的读写测试。

这样,我们的仿真激励就修改成功了,可以通过仿真波形图对结果进行验证。

5 仿真波形图

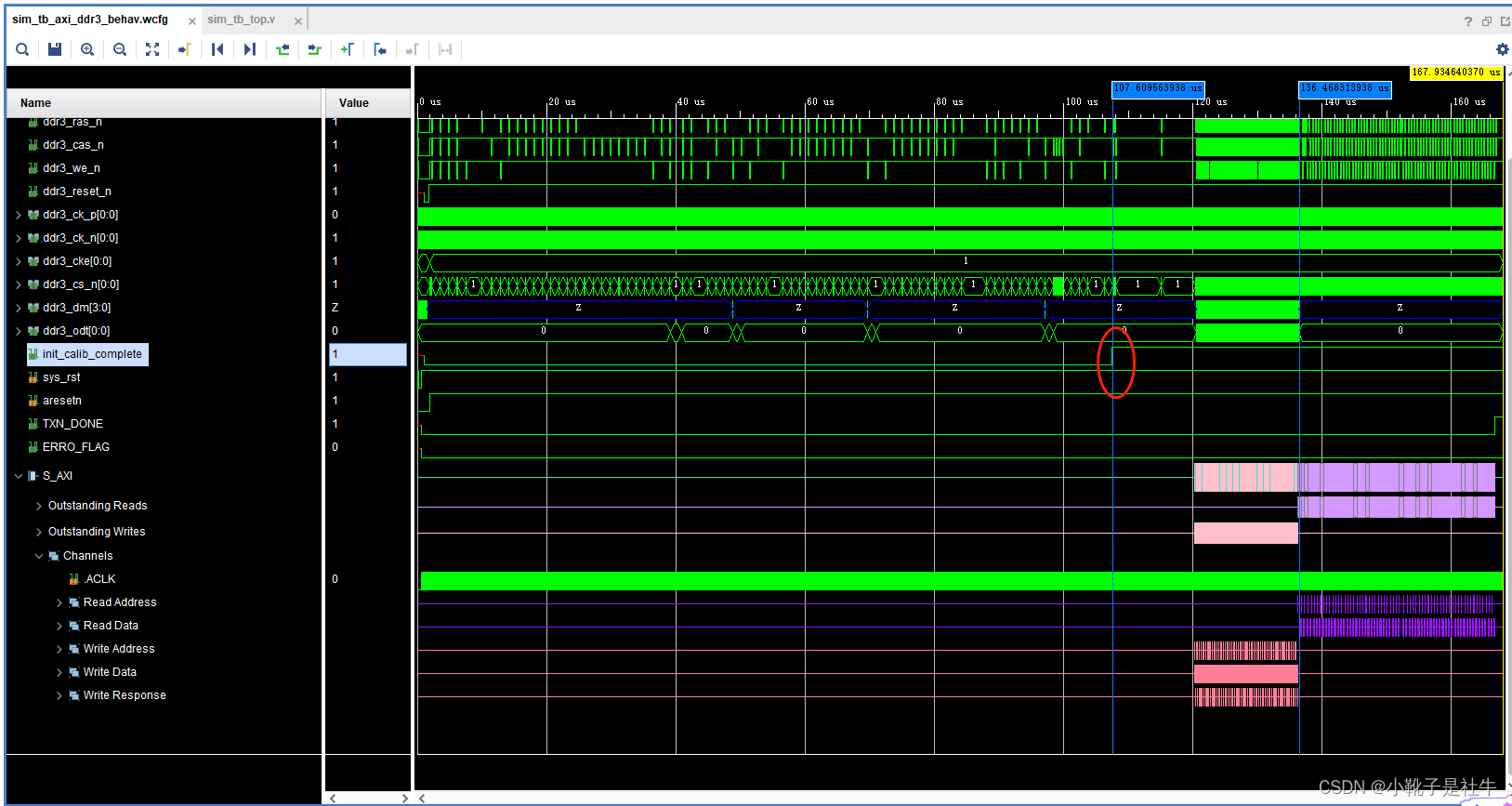

可以看到,在107us左右,初始化信号已经拉高了,之后120us时刻,我们开始进行读写测试。

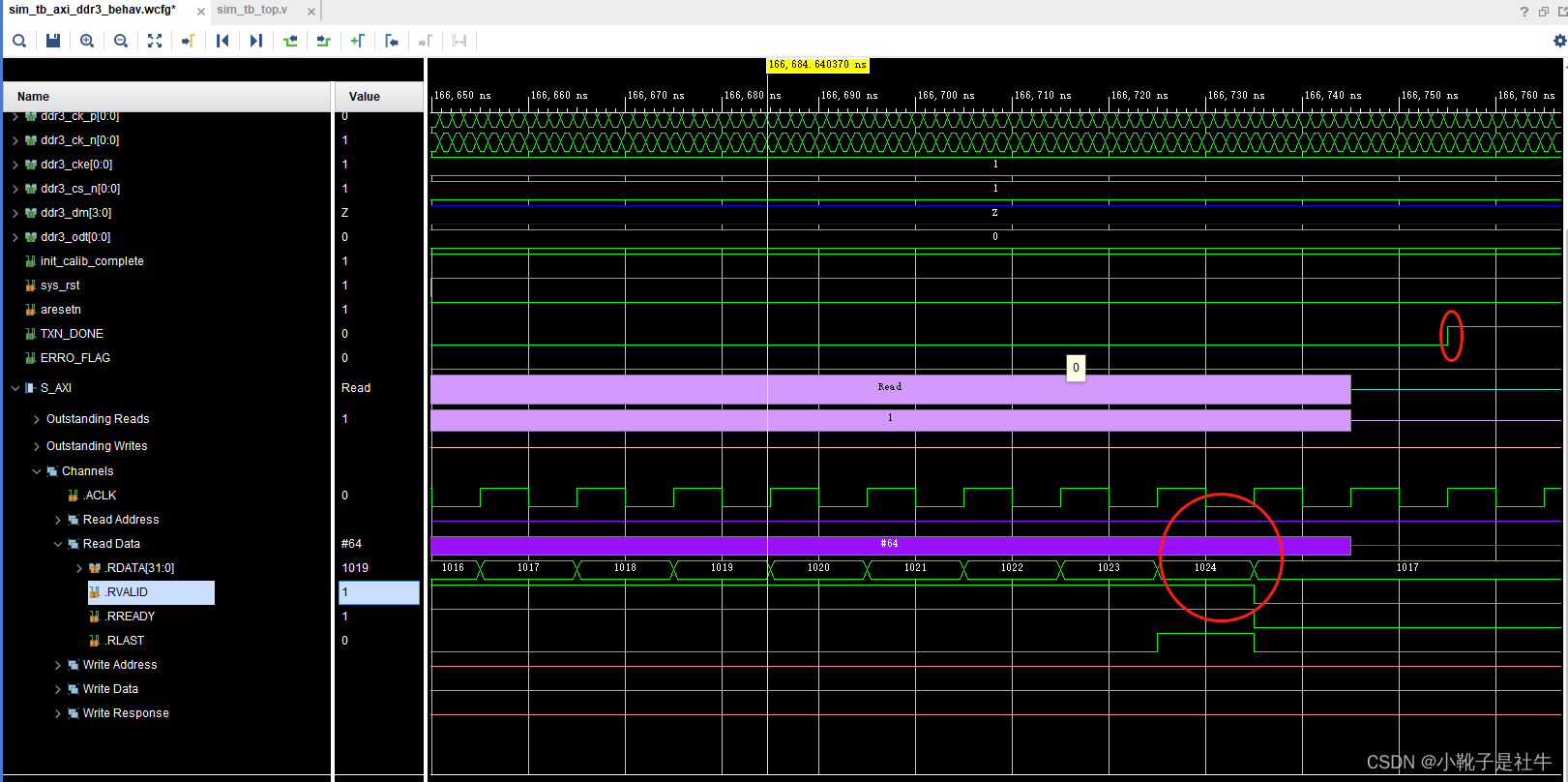

从下图可以看到,AXI的读数据通道已经读出了最后一个数据,并且测试完成信号TX_DONE也已经拉高。而ERRO_FLAG信号并没有拉高,说明功能正常。

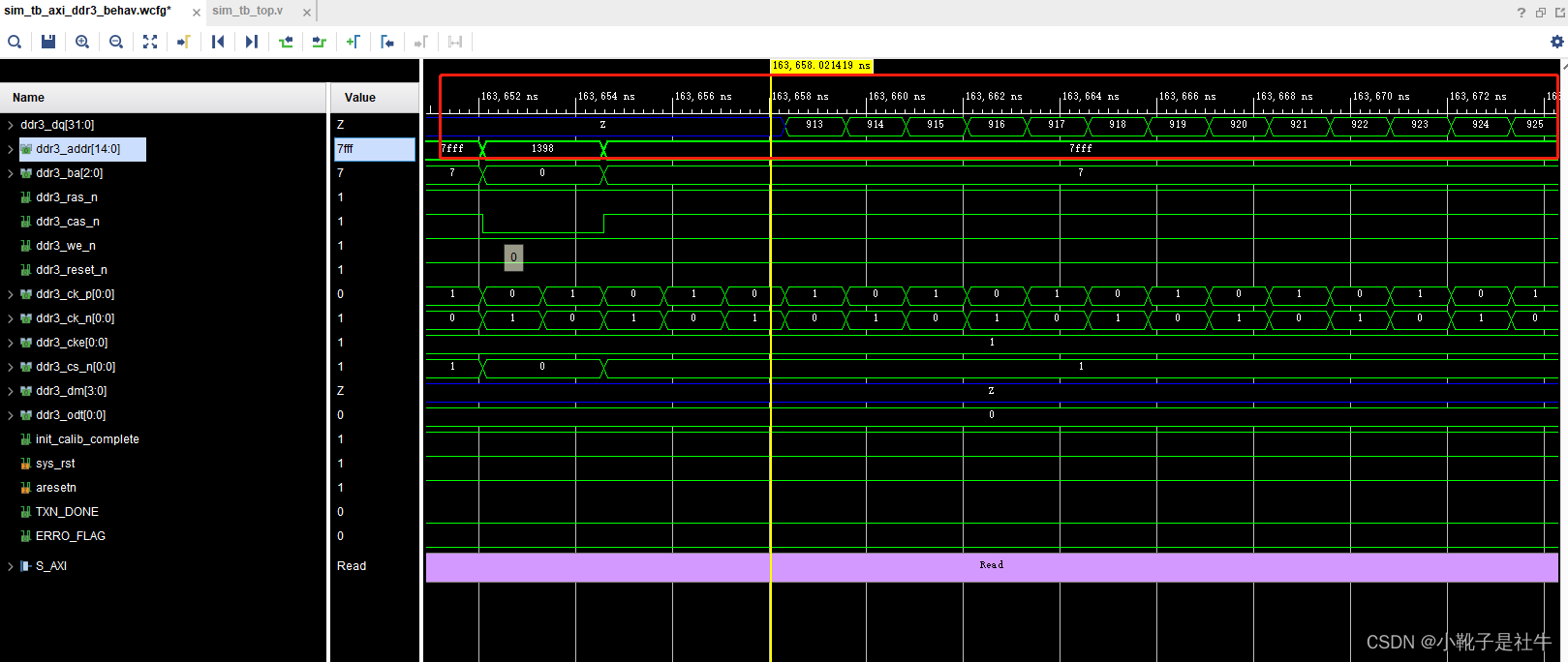

从MIG物理接口的信号也能看出功能是正确的。

本次实验就介绍到这里,主要就是探讨了利用AXI总线与内存交互的过程。