此系列博客,仅对Xilinx平台PS端(ARM部分)开发做介绍,不对PL(FPGA)做过多介绍。

目录

一. FSBL

FSBL包含以下几个部分:

1.Initalization:初始化系统,处理器,DDR等。

2.Boot Device Initalization: 启动设备的初始化,第二段启动设备的初始化等。

3.Partition Loading: 固件加载,分区头文件验证,固件拷贝等。

4.Handoff: 启动,PM初始化等

注:FSBL和PMU交互通过 PMU 的全局寄存器 PMU_GLOBAL_BASEADDR

二. 初始启动

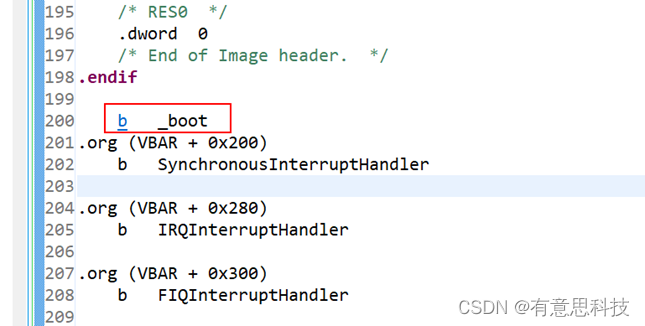

2.1 asm_vector.S

1.在此文件为PS的RPU/APU执行的初始位置, .org 0程序从地址0开始执行

2.跳转到 _boot

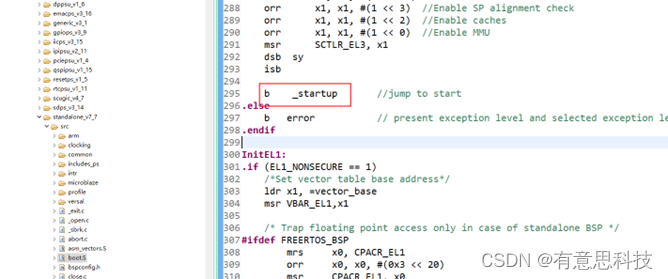

2.2 boot.S

1.执行CPU初始化相关准备工作

2.跳转到 _startup

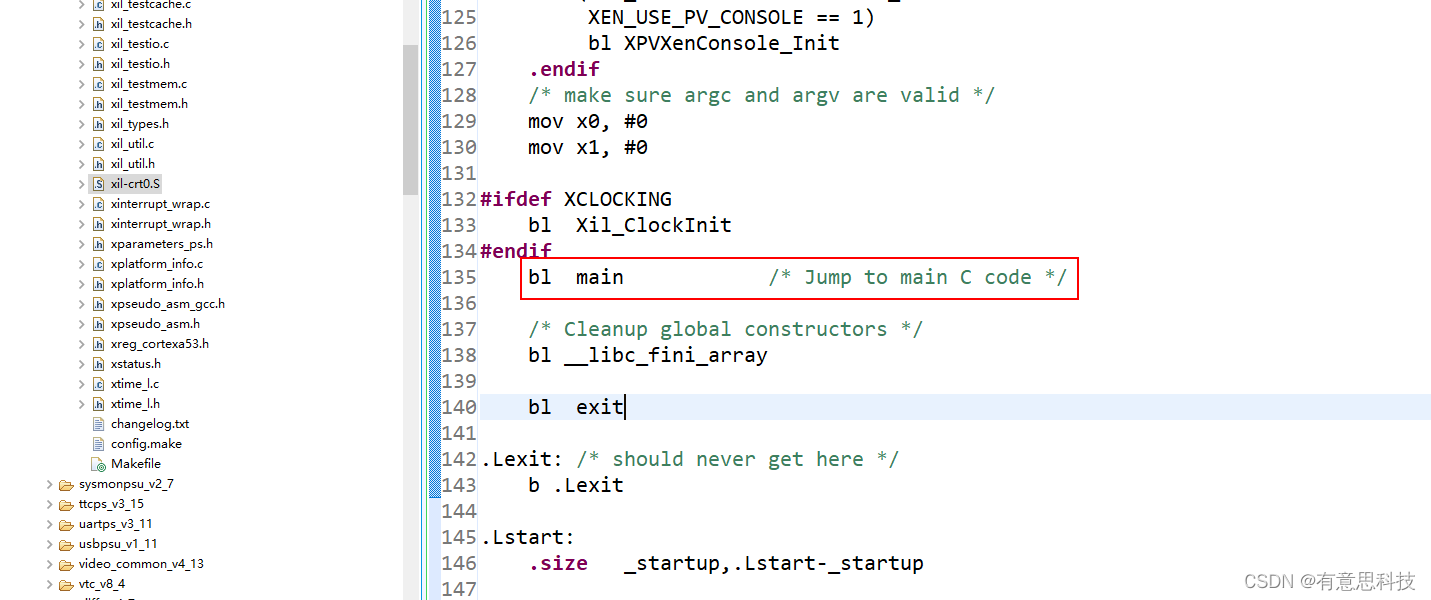

2.3 xil-crt0.S

跳转到C代码main主函数

三. Initalization

此部分主要做一下工作:

- 获取复位的原因

- 系统初始化

- 处理器初始化

- DDR初始化

- 板级外设初始化

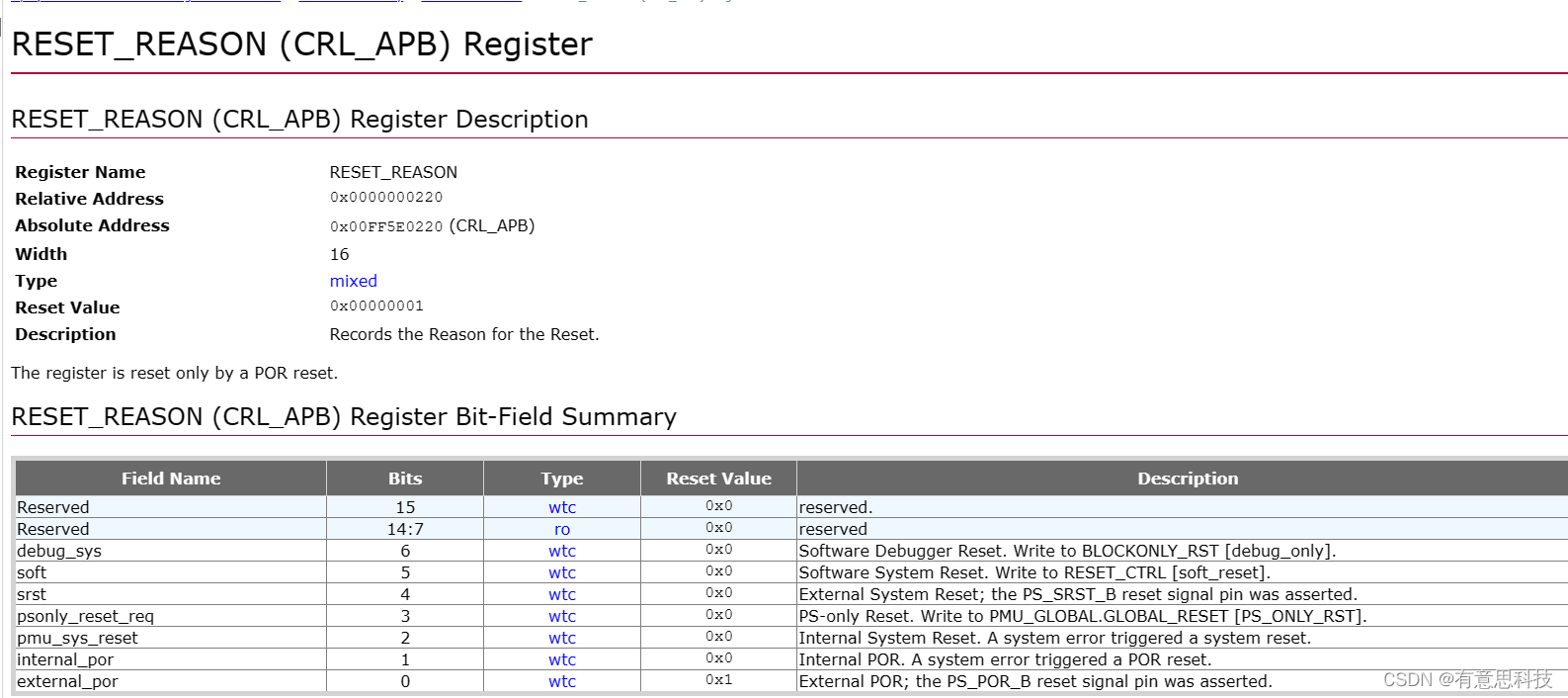

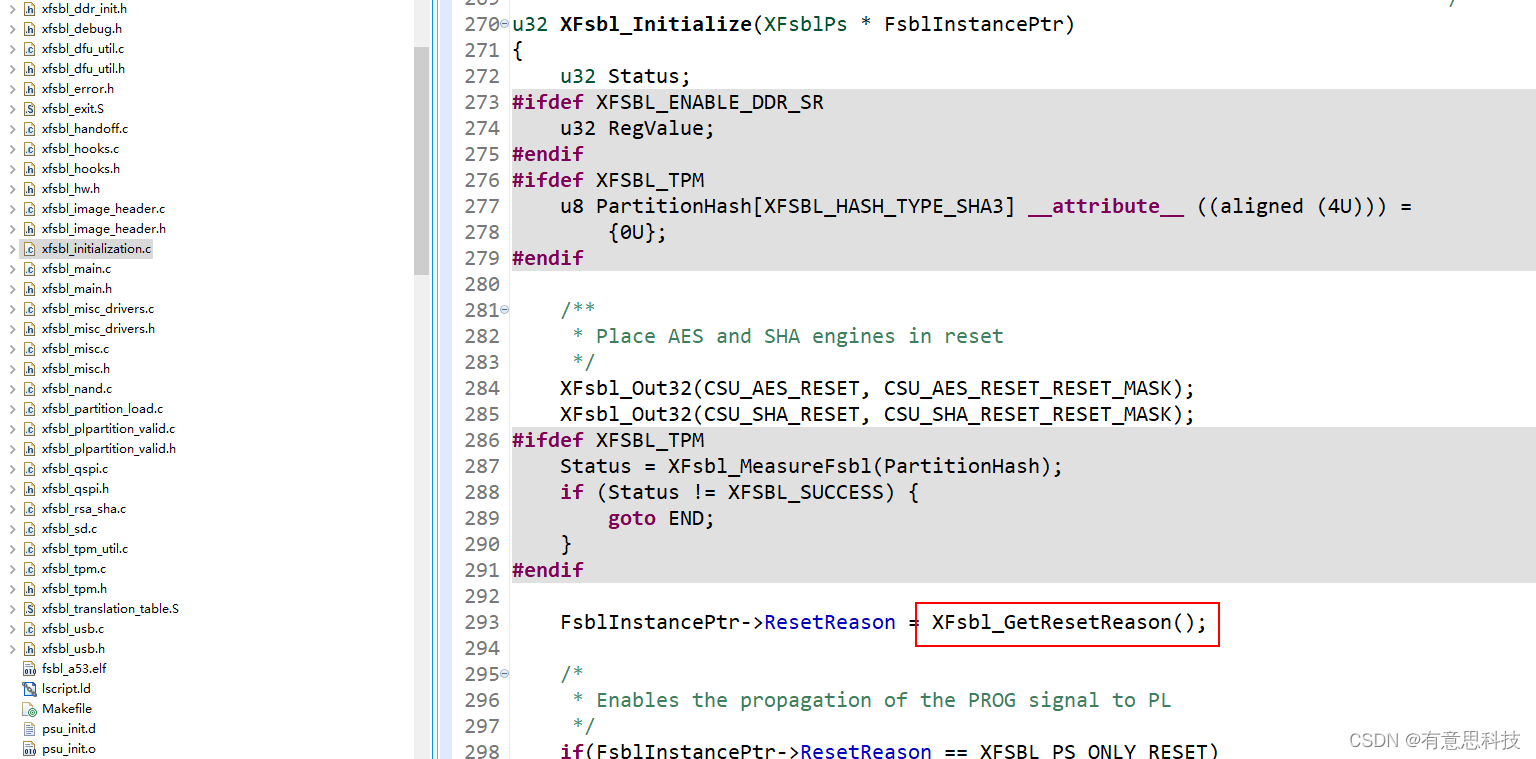

3.1 获取复位原因

1.通过读取RESET_CTRL(CRL_APB)寄存器值获取复位原因

2.不同的复位原因做不同的工作

3.2 系统初始化

- MIO初始化:初始化相关IO口,设置其复用功能

- 外设预初始化:复位SYSMON CLOCK,复位QSPI

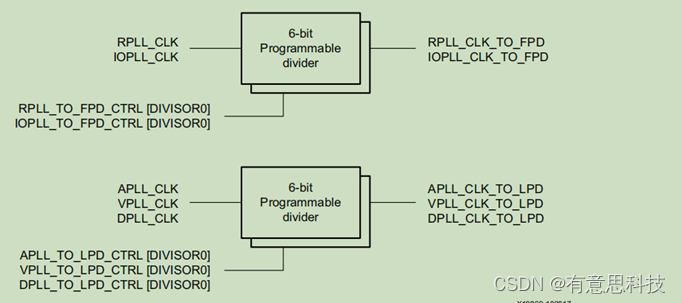

- 初始化PLL

(1)初始化RPLL,输出时钟到RPU_FPD

(2)初始化IOPLL,输出时钟到IO_FPD

(3)初始化APLL,输出时钟到APU_LPD

(4)初始化DDR_PLL,输出时钟到DDR_LPD

(5)初始化VPLL,输出时钟到VPLL_LPD

4.时钟初始化

配置GEM3(千兆以太网控制器),USB0,USB3,IIC,CAN,DP,DDR等时钟。

5.DDR数据初始化

配置相应寄存器,复位,使用何种类型DDR等等

6.DDR 控制器初始化

PYH初始化,DRAM初始化,数据传输

7.外设初始化

配置,复位,GPIO使能,输入输出,SDIO,USB0,USB3,IIC,CAN,DP,GEM等

8.SerDes()初始化

使用SerDes通信技术的接口进行初始化,USB,GEM,PCIE,DP等

注:SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号

9.初始化SMMU,以至于可以获取SMMU消息

10.配置AFI(AXI FIFO Interface)

11.配置DDR QOS

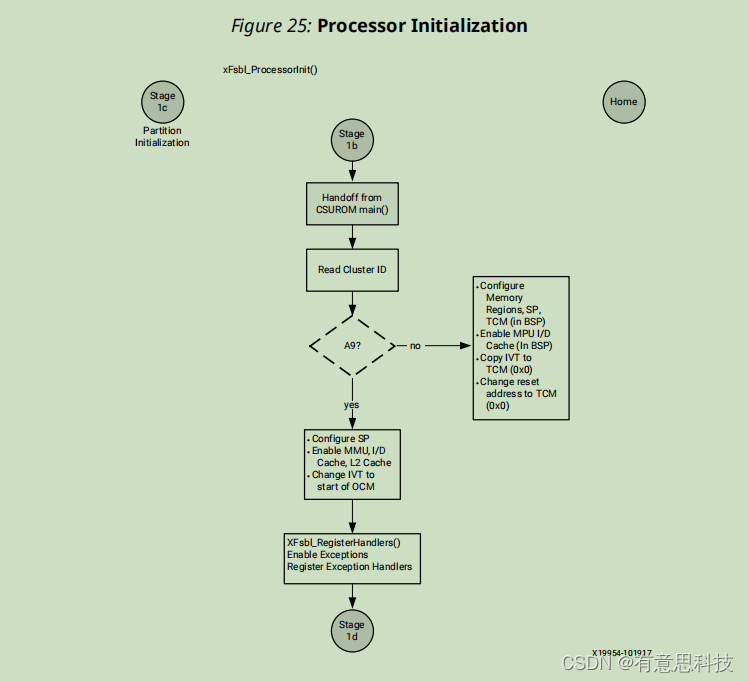

3.3 处理器初始化

- 读取CPU ClusterID,运行于那个CPU,从协处理器CP15中读取,并存储

- 读取设备名等

- 更新PMU GLOBAL_GEN_STORAGE5 (PMU_GLOBAL)寄存器值,存储的是处理器的值

- 注册异常中断

3.4 其他初始化

- 如果DDR支持ECC,进行ECC初始化

- 底板自定义的相关初始化,可根据不同板子进行相应初始化工作XFsbl_BoardInit