AHB 与 APB、ASB同属于 AMBA 总线架构规范,该总线规范由 ARM 公司提出。

目录

一、AHB 总线

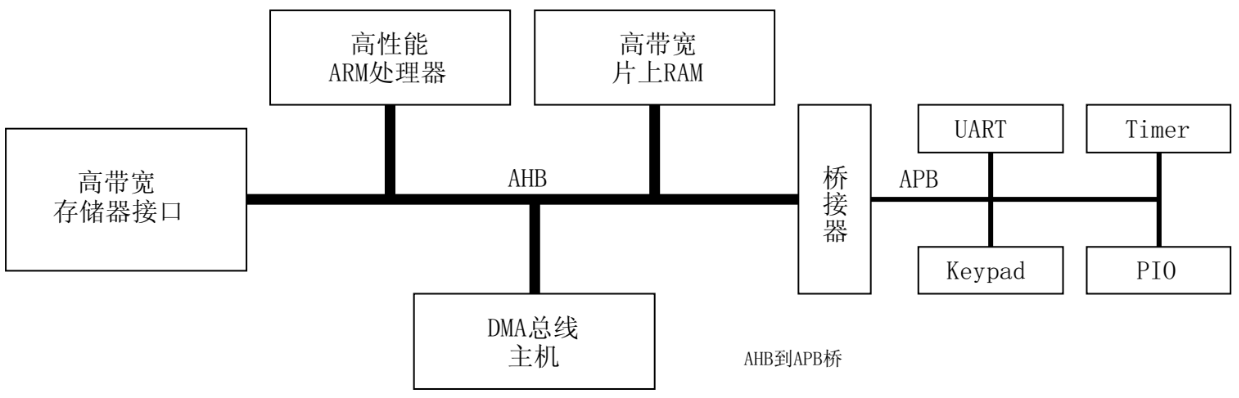

AHB(Advanced High Performance Bus),意为高级高性能总线,能将微控制器(CPU)、高带宽的外部存储器接口、高带宽的片上RAM、DMA总线等各种拥有AHB接口的控制器连接起来,构成一个完整的 SOC 系统。可以通过 AHB-APB 桥来连接 APB。

APB(Advanced Peripheral Bus),意为高级外设总线,STM32 中还可细分为 APB1 和 APB2

- APB1负责DA、USB、SPI、I2C、CAN、TIM、串口2345,主要支持低速状态下的工作

- APB2负责AD、I/O、高级TIM、串口1,主要APB2支持高速状态下的工作

二、AHB 总线组成

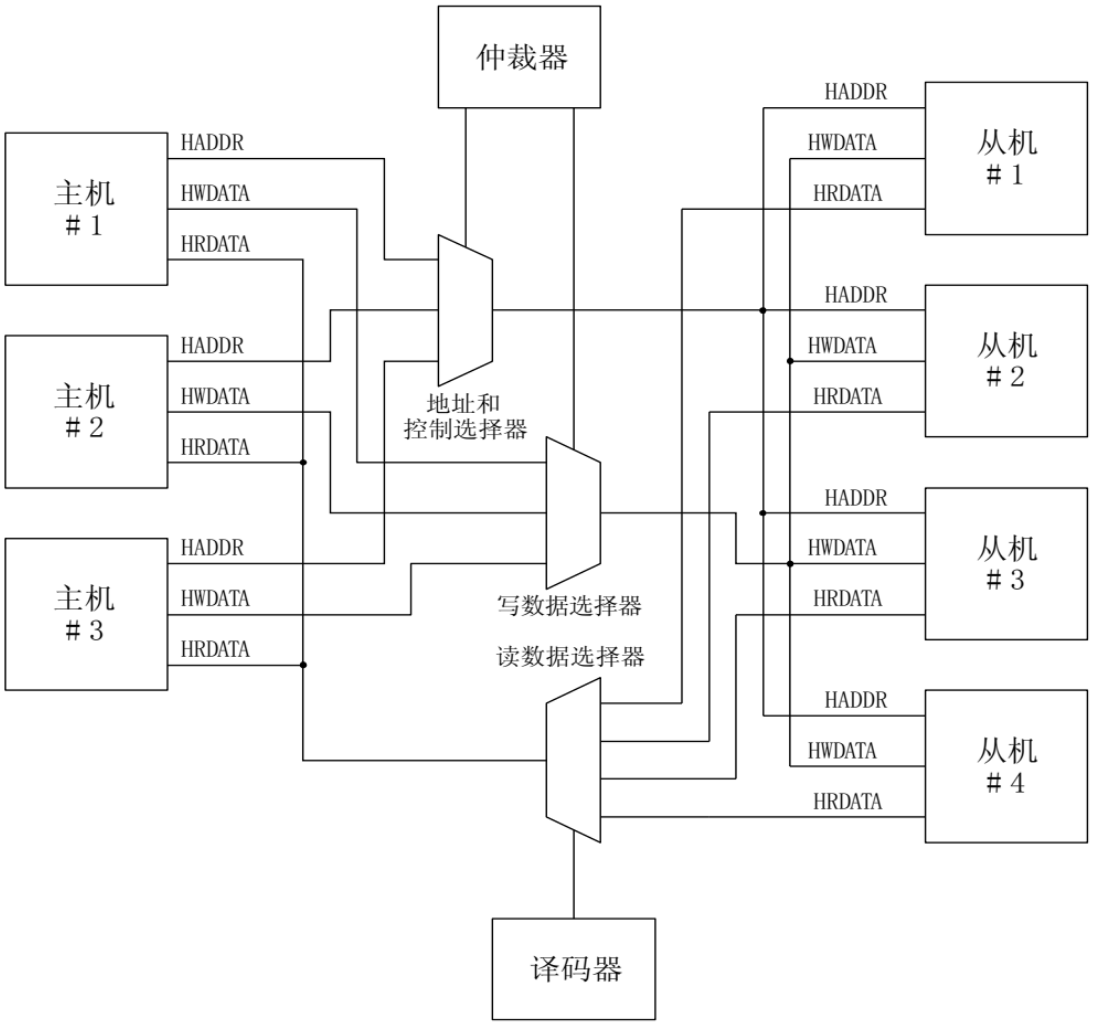

AHB 总线可以将 DMA、高速RAM、高速存储器等具备 AHB 接口的控制器连接起来,这些控制器/硬件设备大体可以分为四类。

- AHB 主设备:总线主机可以通过地址和控制信息发起一次读 / 写操作。某个时刻仅有一个主机占用总线

- AHB 从设备:总线从机响应主机发起的读写操作。总线从机 会将读写成功或者失败的信号反馈给主设备

- AHB 仲裁器:当存在多个设备申请占用总线时,会发起仲裁,确保每次只有一个设备占用总线

- AHB 译码器:用来对每次传输进行地址译码,并在传输中包含一个从设备的选择信号

为了方便主 / 从设备的地址和数据传输,每个主 / 从设备都会连接三根总线

- HADDR:地址控制总线

- HWDATA:写数据总线(用于从 Master 到 Slave 的数据传输)

- HRDATA:读数据总线(用于从 Slave 到 Master 的数据传输)

三、AHB 主从通信过程

选择主设备

需要占用总线的 Master 向仲裁器发出请求,冲裁器授权给指定的 Master。任一时刻只能有一台 Master占用总线,占用总线的 Master 可以对其指定的 Slave 进行读写操作。

选择从设备

Master 发出地址和控制信号,提供地址信息、传输方向、带宽和brust类型。译码器根据地址和控制信号确定那个Slave与Master进行数据通信。

- 地址周期:传输地址。占用一个周期

- 控制周期:传输读写方向。占用一个周期

- 数据周期:传输数据。占用一个或多个周期(通过 HREADY 信号控制周期数目)

数据传输

一般情况下只有当 Master 完成一次完整的数据传输,冲裁器才会授权给其他 Master 接入总线。有的时候为避免过大的判决延迟,冲裁器也可能打断 burst 传输。这种情况下 Master 必须再次接入总线以进行剩余部分的传输。

参考文章:

FPGA奈克斯特——AMBA(AHB)总线初识及接口定义 - 知乎 (zhihu.com)