资料来自:《世界前沿技术发展报告2023》和网络

1. 概述

电子信息技术是现代信息技术的底层支持技术,在长期的发展过程中对计算、通信等技术的发展提供了重要支持。元器件和架构的不断创新推动各类实用设备的研发,以此开发的计算机、人工智能、机器人等技术正在彻底变革医疗保健、运输和制造等行业,并有助于提升流程效率;高速互联网和移动设备的可用性使人们能够随时随地访问丰富的信息,提升沟通与协作的效率,促进社会和文化交流。

2. 微电子技术

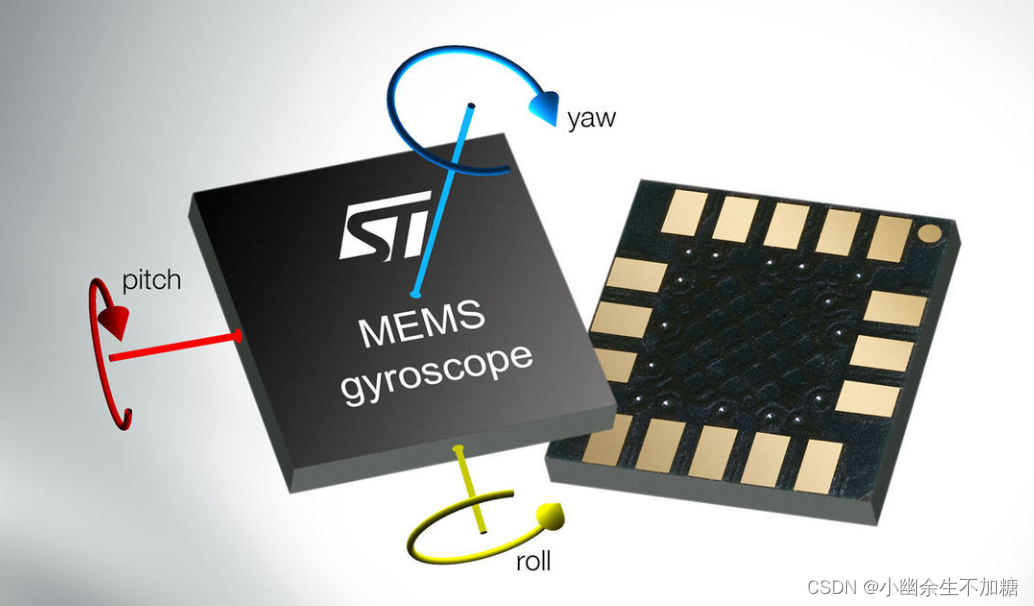

微电子技术在许多现代技术的发展和进步中起着至关重要的作用。这种技术旨在将电子元件和电路集成到小芯片或微处理器上,可用于各种设备和系统。将多个组件和电路集成到单个芯片上的能力大大提高了电子系统的性能和可靠性,同时还减小了系统的尺寸、重量和成本,且提高了性能和效率。这使复杂和精密系统的发展成为可能,不断拓展与丰富各类军事和民用信息系统的应用场景。

2.1 精细制程芯片

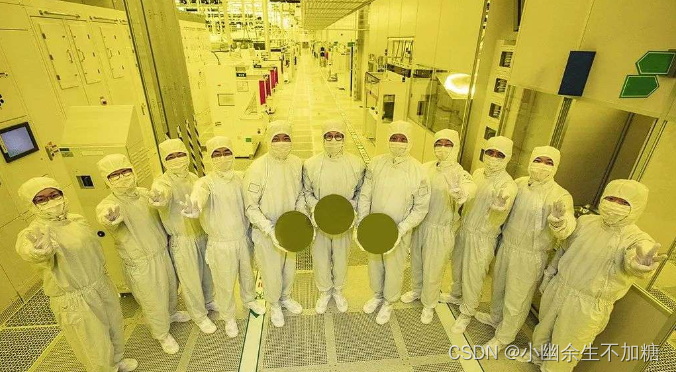

2022年,韩国三星电子和中国台积电实现了3纳米制程工艺芯片量产,2纳米制程工艺芯片也在加紧开发中。芯片制程的不断微缩使设备的运算性能和效率不断提升,且体积更小,有望在数据中心、消费电子、人工智能等行业场景中发挥更大作用。

2.1.1 中国台积电发布2纳米制程工艺细节

台积电在北美技术论坛上公布其未来先进制程路线图,拟于2025年量产2纳米制程芯片。为此,台积电将于2024年引入荷兰阿斯麦公司(ASML)最先进、最新的高数值孔径极紫外光刻机,用于量产2纳米制程芯片。台积电的2纳米制程工艺将采用全环绕栅极场效应晶体管(Gate-All-Around Field Effect Transistors, GAAFET)架构。在相同功耗下,2纳米芯片性能速度较3纳米提高10%~15%;在相同速度下,功耗降低25%~30%。台积电表示,2纳米制程工艺平台将涵盖高效能版本及完备的小芯片整合解决方案。预计商用2纳米芯片将在2025年年底或2026年上市。

2.1.2 美国英特尔公司称2030年芯片晶体管密度将达到目前的10倍

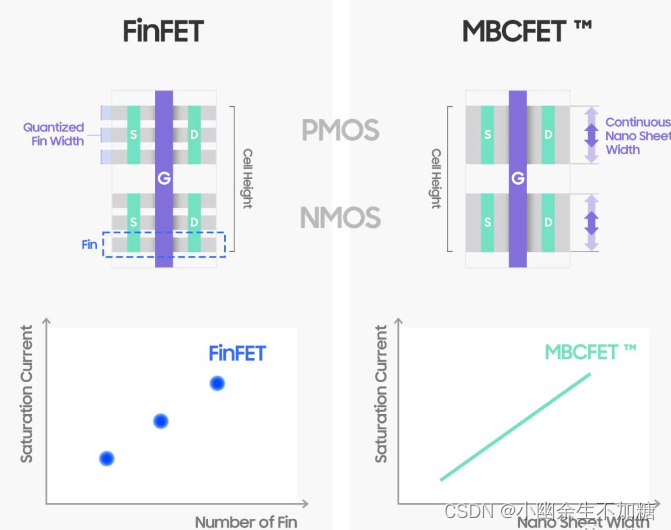

2022年8月,美国英特尔公司首席执行官帕特·基辛格(Pat Gelsinger)出席Hotchips 2022会议,就未来芯片技术进行展望。基辛格指出,先进封装技术将推动摩尔定律发展,将发展出先进的基于小芯片(Chiplet-Based)的系统封装模式(System on Package, SoP),其内涵是芯片制造厂不再仅提供单一的晶圆生产,而是提供完整的系统级服务,包括晶圆生产、先进封装及整合在一起的软件技术等。基辛格指出,目前的芯片最多有约1000亿晶体管,而随着SoP技术的发展,到2030年,芯片的密度将提升到1万亿晶体管,是目前的10倍。为实现这一目标,英特尔将会在2024年量产的20A工艺上放弃鳍式场效应晶体管(FinFET)技术,转向带状晶体管(RibbonFET)及PowerVia等下一代技术。PowerVia是英特尔独有的、业界首个背面电能传输网络,通过消除晶圆正面供电布线需求来优化信号传输。

2.1.3 韩国三星电子率先实现3纳米制程芯片量产

2022年5月,韩国三星电子宣布正式开始量产基于全环绕栅极晶体管(GAAFET)架构的3纳米芯片,成为全球首家量产3纳米芯片的公司。韩国三星电子表示,与5纳米芯片相比,3纳米芯片的性能提高了23%、功耗降低了45%、芯片面积减少了16%。该公司将于2023年推出第二代3纳米芯片,其功耗将降低50%、性能将提升30%、芯片面积将减少35%。

2.1.4 日本丰田、索尼等8家公司合资成立高端芯片公司,生产2纳米及以下制程芯片

2022年8月,日本丰田汽车、索尼、日本电信电话、日本电气、电装(Denso)、软银(Softbank)、铠侠和三菱日联银行(Bank of Tokyo-Mitsubishi UFJ, MUFG Bank)8家公司合资成立Rapidus高端芯片公司,将在日本国内生产用于超级计算机和人工智能的下一代半导体芯片。该公司将依靠日本与美国的合作关系,借助IBM公司的技术,力争到2025年试产2纳米芯片,2027年实现2纳米及以下制程的芯片大规模量产。日本新能源和工业技术开发机构(New Energy and Industrial Technology Development Organization, NEDO)已委托Rapidus参与5G通信先进半导体制造项目。

2.1.5 中国台积电正式量产3纳米制程工艺

2022年12月,台积电在其晶圆18厂启动3纳米制程芯片的正式商业化量产。台积电晶圆18厂一期于2018年开工建设,此前主要生产5纳米制程芯片。随着3纳米芯片的商业化量产,未来台积电晶圆18厂将成为其先进制程工艺的主要生产基地。在3纳米制程工艺上,中国台积电和韩国三星电子采用不同的路线,韩国三星电子采用全环绕栅极晶体管(GAAFEET)架构,而中国台积电则是采用鳍式场效应晶体管(FinFET)架构。

2.2 特殊工艺

数据中心和人工智能对算力的需求激增,对计算设备效率及能耗提出更高要求。为此,全球主要公司与研究机构不断探索新的技术与工艺,在材料、电路设计、制造工艺等方面寻求新的突破,追求更优化的系统集成、更高的效率和更低的能耗。

2.2.1 三星发布全球首款基于磁阻随机存取内存的计算机

2022年1月,韩国三星电子发布世界首款基于磁阻随机存取内存(Magnetoresistive Random Access Memory, MRAM)的计算机,有望用于人工智能运算。目前的计算机大多采用独立的内存芯片及独立的硬盘存储。为了提高运算效率,业界一直在开发包括MRAM在内的各种非易失内存(Non-Volatile Memory, NVM),兼顾硬盘和内存的功能,支持内存计算(Computing in Memory, CIM)新范式,同时有助于大幅降低功耗。为了实现这一目标,研究人员开发了阻抗随机存取内存(Resistive Random Access Memory, RRAM)、相变随机存取内存(Phase-Change Random Access Memory, PRAM)等非易失内存,而三星独辟蹊径开发出MRAM内存计算芯片原型。三星的MRAM具有高速、耐用、容易量产等优点。

2.2.2 俄罗斯研发X射线光刻机

2022年4月,俄罗斯莫斯科电子技术学院(National Research University of Electronic Technology, MIET)承接俄罗斯联邦工业和贸易部(Ministry of Industry and Trade of the Russian Federation)派发的X射线光刻机研制项目。俄罗斯政府将向该项目投入6.7亿卢布资金(约合916万美元)的首期资金,该项目研发的光刻机将达到极紫外光刻级别,但技术原理完全不同。X射线光刻机是基于同步加速器或等离子体源的无掩模X射线光刻机,所使用的X射线波长介于0.01纳米到10纳米之间,比极紫外光还要短,因此其光刻分辨率要高于EUV光刻机。此外,X射线光刻机相比EUV光刻机,不需要光掩模板就可直接进行光刻作业,成本更低。全球范围内,中国、美国和欧洲都有X射线光刻的相关研究,但尚没有能达到规模量产的X射线光刻机。俄罗斯在X射线及等离子之类的技术上有着深厚的基础,因此具备一定研发实力。

2.2.3 日本东京大学开发出三维垂直场效应晶体管,将催生更小、更环保的数据存储器

2022年6月,日本东京大学工业科学研究所(Institute of Industrial Science, the University of Tokyo)的研究人员开发了一种基于铁电和反铁电场效应晶体管的概念验证3D堆叠存储单元。这种晶体管可以非易失方式存储1和0数据,这意味着其不需要一直供电;垂直设备结构则增加了信息密度并降低了运算能源需求。此外,通过使用反铁电体代替铁电体,该存储单元只需要很小的净电荷就能擦除数据,提高了写入的效率。研究证实,该器件在至少1000个使用周期内都可保持稳定。研究人员称,新技术或将大幅改善非易失存储器,同时有助于开发

2.2.4 中美研究人员实现亚0.5纳米电介质与二维半导体集成

2022年10月,中国北京大学和美国得克萨斯大学奥斯汀分校(University of Texas at Austin, UT Austin)联合研究团队实现了亚0.5纳米电介质与二维半导体集成。研究人员使用一种名为紫外线辅助插层氧化的工艺来合成硒-铋氧化物二维材料,使其拥有高介电常数、超平坦的晶格匹配界面和出色的绝缘性。经测试,这种材料的等效氧化物厚度低至0.41纳米时,其在1伏特栅极电压下的漏电流仍处于超低水平,满足下一代晶体管电介质的工业要求。该新型材料有望用于开发二维晶体管中的超薄高介电常数栅极电介质,帮助实现晶体管的小型化。

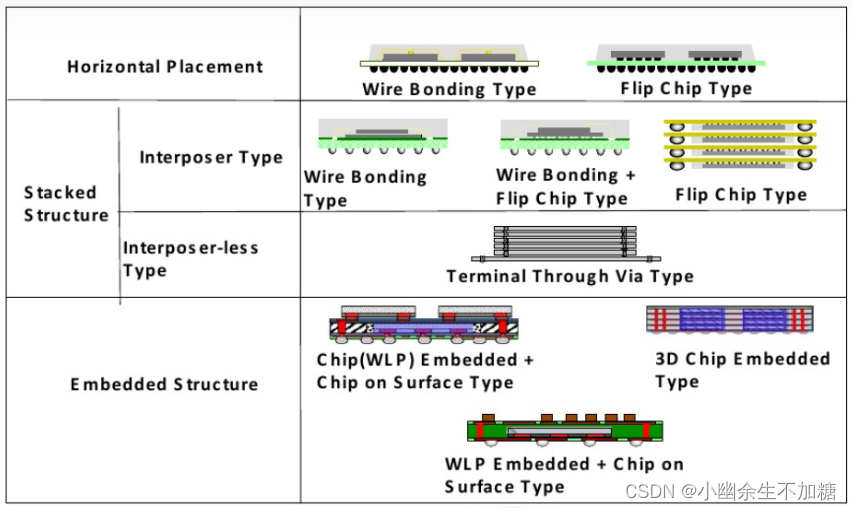

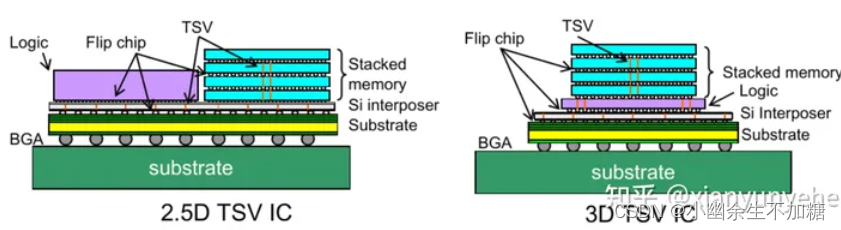

2.3 先进封装

随着半导体前端制造节点变得越来越精细,设计成本快速增加,先进封装及其2.5D和3D解决方案应运而生,在降低前端制造成本方面变得至关重要且有效。同时,先进封装解决方案在数据传输方面有新的高性能协议,有助于提高系统性能并提供更低的延迟、更高的带宽和电源效率。

2.3.1 英特尔、微软和台积电等IT巨头成立小芯片互连联盟

2022年3月,英特尔、AMD、高通、三星、台积电、Meta和微软等行业巨头成立小芯片互连(UCIe)标准联盟。UCIe标准推出的初衷是通过开源设计实现芯片互连标准化,从而降低成本,促进形成更广泛的验证芯片的生态系统。这种新的互连标准将实现小芯片之间的标准化连接。UCIe标准的目标是像USB等其他连接标准一样普遍和通用,同时为小芯片连接提供卓越的功率和性能指标,将覆盖X86和ARM生态。

2.3.2 英特尔3D封装技术取得新进展

2022年6月,英特尔公司在封装设计中开发了一种嵌入式电感的全集成稳压器(Fully Integrated Voltage Regulators,FIVR),用于控制芯片在3D硅通孔(3D Through Silicon Via,3D-TSV)堆叠系统中的功率。电压控制器对于3D封装至关重要,有助于基于工作负载的最优流程节点实现小芯片封装。FIVR在基于22纳米工艺的裸片上实现,采用三种硅通孔(Through Silicon Via, TSV)友好型电感结构,具有多重关于面积与效率的折中选项。

2.3.3 韩国三星电子成立半导体封装事业部,以加强与大型代工客户的合作

2022年7月,韩国三星电子成立半导体封装事业部,旨在加强与封装领域的大型代工客户的合作。该部门由三星设备解决方案事业部的测试封装工程师、半导体研发中心成员,以及内存和代工部门的人员组成,将开发先进的封装解决方案,以加强与广大代工客户合作的决心。随着前端工艺的电路小型化工作达到极限,各大芯片制造商将在各种先进封装工艺上展开更激烈的竞争。目前,英特尔和台积电等半导体巨头都在该领域大举投资,尤其是3D封装和小芯片技术。

2.3.4 英特尔公司发表论文展示UCIe标准技术细节

2022年10月,英特尔公司发布《小芯片互联:封装级小芯片创新的开放行业标准》(UCIe: An Open Industry Standard for Innovations with Chiplets at Package Level),对小芯片互联标准的技术细节进行了介绍。UCIe是一种开放的行业标准互连,为异构芯片提供了芯片封装内连接,以满足整个计算系统的需求,使设计者能对不同种类、不同厂商的芯片进行封装,以实现高性能、灵活性和互操作性的目标。该论文从小芯片分层设计、物理层架构、标准封装通道设计、先进封装通道设计等方面介绍了技术细节,并对UCIe封装通道性能测试结果进行了分析,表明该标准具有高带宽、低延迟、高电源效率和高性价比的特性。

2.3.5 日本东京工业大学研究团队研发出一种新型芯片封装技术,可有效降低集成复杂度

2022年10月,日本东京工业大学研究团队研发出一种新型芯片封装技术,该技术满足宽带芯片间通信和可扩展的芯片集成的要求,并有效降低了集成的复杂度。该研究团队设计了小芯片硅桥互连结构,通过精细的“微柱”实现芯片之间的宽带通信,并采用后上芯(Chip-Last)工艺进行集成。该新型芯片封装结构可以提高芯片外部布线的高频特性和散热性能,而且在放大集成时没有良品率问题。未来,该技术有望加速半导体集成技术的演进,进一步推动芯片小型化发展。

2.3.6 韩国三星公司拟使用背面供电网络技术研发2纳米芯片,可在晶圆背面进行开发

2022年10月,韩国三星公司拟使用背面供电网络(BSPDN)技术研发2纳米芯片。BSPDN技术将芯片上的电源线转移到晶圆空置的背面,通过减薄的背面直接向高级微处理器核心芯片供电,从而增加芯片的晶体管集成度。开发晶圆背面成为继制程缩进、3D封装后第三个提高芯片晶体管密度的思路。

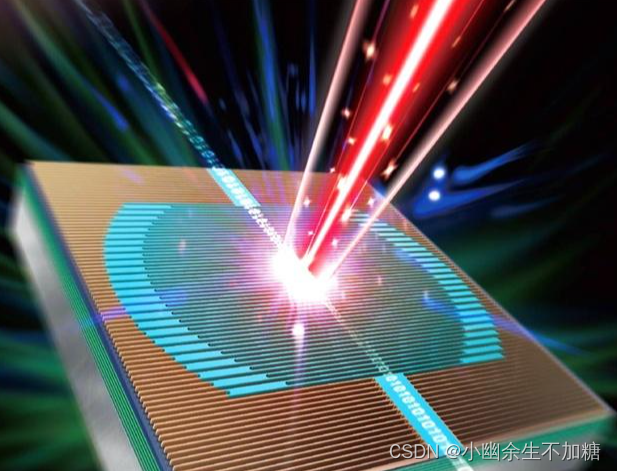

3. 光电子技术

光电子技术涉及光的产生、控制和操纵,从而实现运算、通信和传感。光通信与光计算具有高速、低损耗的特性,允许更快速、更高效的数据传输与运算,且能耗更低。当下,光学器件推陈出新、光电平台集成度日渐提升,不断拓展在高速通信、光计算和医疗诊断等领域的应用。

3.1 美国OpenLight公司推出全球首个开放式硅光子平台

2022年6月,美国新思科技(Synopsys)子公司OpenLight推出全球首个带集成激光器的开放式硅光子平台,以满足日益增长的硅光子市场对性能、功率和可靠性的要求。新思科技工程副总裁艾维克·萨卡(Aveek Sarkar)表示,OpenLight正在通过实现激光器在可插拔和共封装光学元件中的可扩展集成,为新一代硅光子学铺平道路。新思科技的电子和光子设计解决方案与OpenLight创新型硅光子平台相结合,将显著加速光子集成电路的开发。

3.2 美国佐治亚理工学院开发出新的电调光子超表面平台

2022年5月,美国佐治亚理工学院(Georgia Institute of Technology, Gatech)研究人员开发出一种新的电调光子超表面平台(Electrically Tunable Photonic Metasurface Platform)。超表面具有特殊的光学特性,可使光学系统变得轻薄。传统的超表面都是无源的,性能在制造后无法改变或调整。美国佐治亚理工学院基于一种名为特殊相变材料的纳米光子材料,开发出新型电调光子超表面平台。研究人员通过局部加热的方式改变特殊相变材料的光学特性,使其能形成可重构的超表面平台。经测试,该平台反射特性变化范围达到11倍,且具有大范围的光谱调谐操作性能及更快的调谐速度。该技术将促进透镜技术的进步,预计会对激光雷达系统、成像、光谱学和传感等技术产生直接影响。

3.3 美国英特尔研究院光电集成技术取得重大进展

2022年7月,美国英特尔研究院在硅晶圆上成功集成光学与电子设备。英特尔在300毫米晶圆上成功制造了具有8个微环调制器和光波导的8波长分布式反馈激光器阵列,其中每个微环调制器都被调节到特定的波长。利用多波长,每个微环都可单独调制光波,以实现独立通信。该光电共封装解决方案使用了密集波分复用技术,输出功率均匀性达到±0.25分贝,波长间隔均匀性达到±6.5%,均优于行业水平,展现了在增加带宽的同时显著缩小光子芯片尺寸的前景。随着电气互连性能逐渐接近实际极限,将硅电路和光学器件并排集成在同一封装上,有望在未来提高输入/输出(Imput/Output, I/O)接口的能效,延长传输距离。

3.4 美国加利福尼亚理工大学研发出一种新型超快全光开关

2022年8月,美国加利福尼亚理工大学(California Institute of Technology, Caltech)研究人员研发出一种新型全光开关,处理信息的速度可达9太比特每秒,且能耗更低,打破了集成光学平台综合性能的纪录。研究人员利用薄膜铌酸锂平台较强的等效二阶非线性光学效应,通过对铌酸锂纳米波导进行巧妙设计,使不同波长的光脉冲能以相近的群速度传播,且不出现脉冲展宽,进而可精确地控制铌酸锂纳米波导的准相位匹配和色散。该成果未来有望应用于实现集成的非线性光学系统。

3.5 .国际研究团队开发出一种新型磁光调制器,可用于超导计算机

2022年9月,美国加利福尼亚大学圣巴巴拉分校(University of California, Santa Barbara, UCSB)、BBN科技公司(BBN Technologies)、微软研究院(Microsoft Research, MSR)、意大利卡利亚里大学(University of Cagliari)和日本东京工业大学研究人员开发出一种磁光调制器,有助于实现基于超导体的大型电子设备和计算机。超导体仅在低温下正常工作,需要通过光纤来传输数据,避免受到温度的干扰。国际团队研究人员开发了一种通过磁场控制光束特性的装置,通过一种名为磁光效应的物理机制,将电磁体中的电流携带的信息转换为光。光可以通过光纤传播并将信息带出寒冷的环境,而不会对低温设备产生影响。这种磁光调制器能够实现每秒2吉比特的调制速率,传输信息的能耗低于每比特4皮焦耳。该设备是提高超导电路传输速率的关键组件。低温磁光材料领域是一个未开发的领域,相关研究未来有更广阔的空间。

3.6 丹麦技术大学开发出基于芯片的光束转向装置,可用于激光雷达

2022年8月,丹麦技术大学(Technical University of Denmark,DTU)研究人员开发出一种基于芯片的光束转向技术,可用于制造尺寸更小、成本更低的激光雷达。光束转向是激光雷达系统的一项关键技术,但传统的机械光束转向系统体积庞大、价格昂贵、对振动敏感且速度有限。丹麦技术大学研究人员开发出一种基于芯片的光学相控阵装置,可以消除光学混叠,在大视野内实现光束转向,同时使光束保持高品质。该研究有望为小型、经济、高效和高性能的激光雷达铺平道路,在自动驾驶、自由空间光通信、3D全息、生物医学传感和虚拟现实等领域得到广泛应用。

3.7 英国苏塞克斯大学研发出新型光子器件微梳,可用于下一代超精密原子钟

2022年8月,英国苏塞克斯大学(University of Sussex)研究人员研发出新型光子器件微梳。该微梳可长期保持稳定性质,能够在被称为微谐振器的微小腔体上产生多种光频率,形成不同颜色的光。这些颜色是均匀分布的,因此微型梳子的行为就像“由光制成的尺子”,可用于以极高的精度测量或生成频率。苏塞克斯大学研究团队将微芯片嵌入标准激光器中,产生出新型的激光腔孤子,可保证微梳在所需的孤子状态下运行。该技术可用于下一代超精密原子钟、网络通信和激光雷达等。