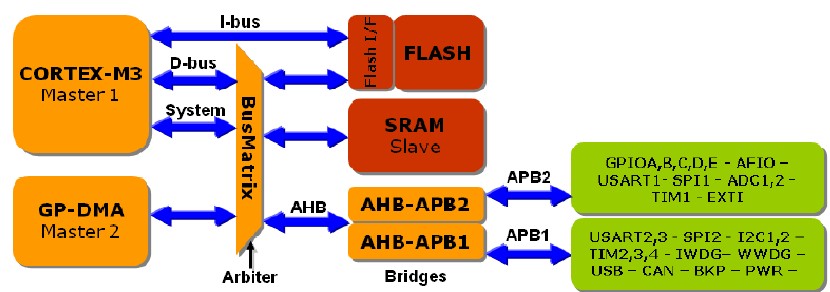

当我们看到STM32 的系统架构时,我们看到Cortex-M3 内核是通过一个专门的I-总线连接到内部FLASH的。此总线与CPU 运行在相同的频率,因此当PLL使能时核心将试图全速运行在72 MHz。由于本质上Cortex CPU是一个单周期的机器,它会试图以每次1.3ns 的速度访问内部FLASH。当STM32启动时,它是从频率为8 MHz 的内部振荡器运行的,因此内部FLASH 的访问时间不是一个问题。然而,一旦PLL启用并作为时钟源,对于运行在最高性能的Cortex CPU来说,FLASH的访问时间太长了(35ns)。为了允许Cortex CPU 运行在72 MHz具有零等待状态,FLASH 存储器具有由两个64 位缓存器组成的预取缓冲器。这些缓冲器可以从FLASH 存储器中进行64 位宽读取,然后传递独立的16 位或32 位指令给Cortex CPU执行。该技术在Thumb-2 指令集的条件执行和Cortex 流水线的分支预测中效果很好。由于FLASH 缓冲区的存在,在正常操作过程中程序员不需要采取任何特别的措施。但是你必须确保在主时钟源切换到PLL前启用它。FLASH缓冲区是由FLASH 访问控制寄存器控的。启用预取缓冲器,你必须调整FLASH 预取缓冲器所需的等待周期,来从FLASH 存储器中读取8个字节。延迟设置如下:

0< SYSCLK <24MHz 0 waitstate

24< SYSCLK <48MHz 1 waitstate

48<SYSCLK <72MHz 2 waitstate

这些等待状态是在预取缓冲器和FLASH存储器之间的,不会影响Cortex CPU。CPU正在执行缓冲器上半部分的指令的同时,下半部分正在加载,使得CPU可以在其最佳的速度无缝地继续执行代码。