0. 相关阅读

1. 使用场景

本教程所介绍的Makefile不太适用于企业级项目,适用于我们平时练习时编写小代码而快速编译的场景。具体来讲,是这样的场景:

我们平时看书或教程时,里面讲到的一些案例我们想实操一下,这类的案例一般比较短小,经常一个.c文件就足矣。如果针对每个小程序都编写一个Makefile那就显得有些麻烦,或者不编写Makefile,那就要手动敲一串gcc编译命令,会影响学习效率。于是我们就有这种需求:在一个文件夹下面有多个.c文件,分别对应一个小程序,而总共只有一个Makefile,只要一个make命令就可以把这些程序全部编译一遍。并且,再往里面增加小程序时,make一下也可以编译这个新增的程序。本篇教程就是为了实现这个需求而编写的Makefile。

2. 编写思路

1. 我们将文件夹下每个.c文件都视为一个程序,编译出来程序的名字(目标)与.c文件的文件名相同(去掉.c后缀),比如app1.c编译出来的程序为app1。实现这个目的的Makefile片断为:

SOURCE = $(wildcard *.c)

TARGETS = $(patsubst %.c, %, $(SOURCE))

2. 每个.c文件独立编译为一个目标,如果直接手写的话,对应的命令类似为:

gcc app1.c -o app1

gcc app2.c -o app2

gcc test.c -o test

这样的命令可以抽象为一个,即:

$(TARGETS):%:%.c

$(CC) $< $(CFLAGS) -o $@

TARGETS即为app1, app2, test,依赖为%:%c,这是一个模式变量,表示与目标相同的.c文件,即:

app1:app1.c

app2:app2.c

test:test.c

有了这两个思路后,Makefile就可以补充完整了。完整的代码可以从这里获取。

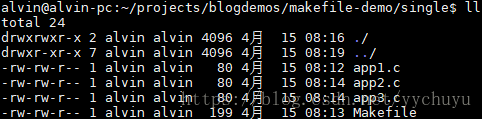

文件夹内容如下:

完整Makefile为:

SOURCE = $(wildcard *.c)

TARGETS = $(patsubst %.c, %, $(SOURCE))

CC = gcc

CFLAGS = -Wall -g

all:$(TARGETS)

$(TARGETS):%:%.c

$(CC) $< $(CFLAGS) -o $@

.PHONY:clean all

clean:

-rm -rf $(TARGETS)

编译完成后文件夹内容为:

3. 作者介绍

本人是一名Linux应用开发工程师,目前供职于一家世界500强公司,主要负责车联网产品的研发。喜交天下好友,欢迎关注本人公众号一起学习、交流!