STM32F103系列增强型微控制器

——时钟控制(RCC)

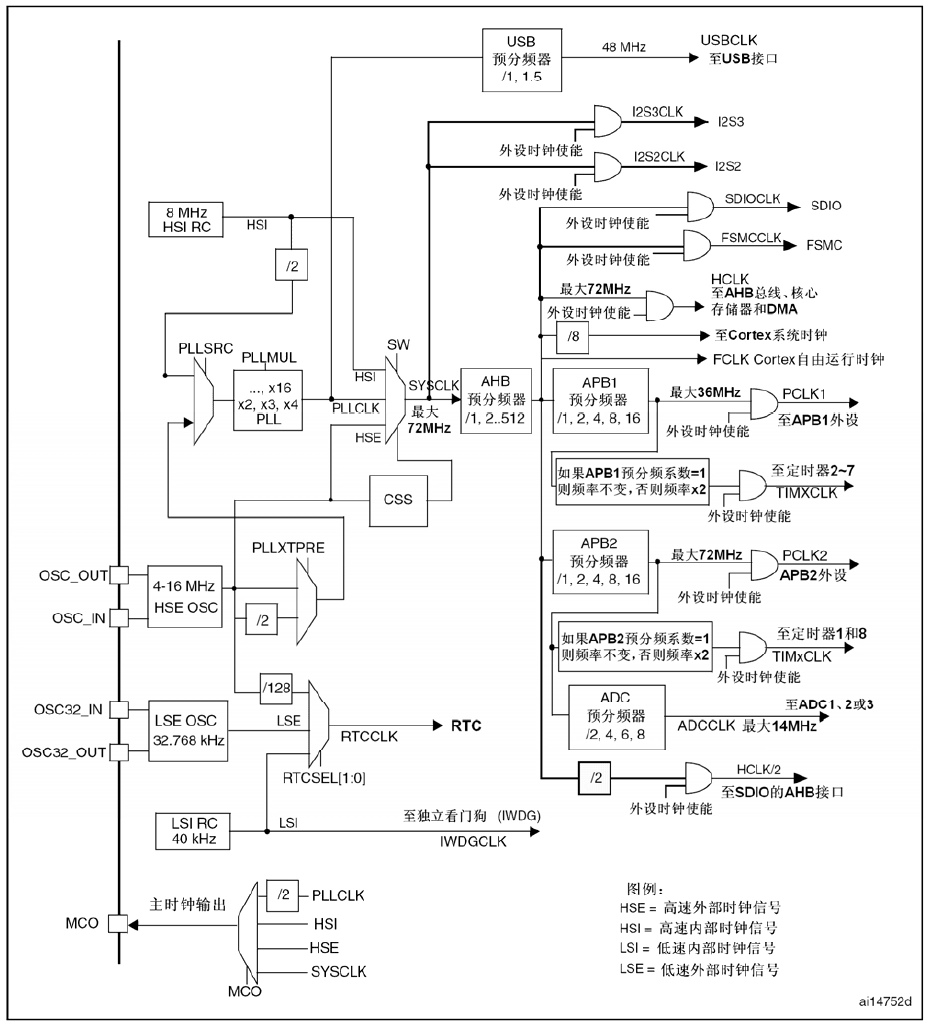

三种不同的时钟源可用作系统时钟(SYSCLOCK):

HIS振荡器时钟(由芯片内部RC振荡器提供)

HSE振荡器时钟(由芯片外部晶体振荡器提供)

PLL时钟(通过倍频HIS或HSE振荡器倍频得到)

另外还有两个时钟源:

LSI内部40kHz低速RC振荡器时钟,用于驱动独立看门狗或选择驱动RTC

LSE外部32.768kHz低速外部输入时钟,用于驱动RTC

时钟模块框图如下:

| 图1 时钟树框图 |

1.当HSI被用于作为PLL时钟的输入时,系统时钟能得到的最大频率是64MHz。

2.用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。AHB和APB2域的最大频率是72MHz。APB1域的最大允许频率是36MHz。SDIO接口的时钟频率固定为HCLK/2。

3. RCC通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟。ADC时钟由高速APB2时钟经2、4、6或8分频后获得。 定时器时钟频率分配由硬件按以下2种情况自动设置:

a. 如果相应的APB预分频系数是1,定时器的时钟频率与所在APB总线频率一致。

b. 否则,定时器的时钟频率被设为与其相连的APB总线频率的2倍。

4. FCLK是Cortex??-M3的自由运行时钟。详情见ARM的Cortex??-M3技术参考手册。

关于HSE、HIS、PLL、LSE、LSI时钟特性及校准直接参考STM32相关Datasheet。

系统时钟配置过程:

配置过程主要对RCC_CR、RCC_CFGR、RCC_CIR这三个寄存器,进行读写访问,配置系统时钟完成后进行对要使用的相应外设时钟进行使能和配置,不用的外设建议关闭相应的外设时钟(降低功耗)。

比较经典的系统时钟选择配置为:使用外部8MHz的HSE时钟源作为PLL时钟输入,PLL再进行9倍频得到72MHZ的时钟作为系统时钟输出,具体实现过程如下:

1、置RCC_CR的HSION[0]位,启动HIS时钟。

2、清RCC_CFGR的MCO[26:24],ADCPRE[15:14],PPRE2[13:11],PPRE1[10:8],HPRE[7:4],SWS[3:2],SW[1:0]位,选择默认的HIS时钟且设置相应的时钟不分频。

3、清RCC_CR的PLLON[24],CSSON[19],HSEON[16]位,关闭PLL和HSE时钟,且关闭时钟检测。

4、清RCC_CR的HSEBYP[18]位,说明HSE时钟为外部的陶瓷晶体振荡器,并非旁路模式。

5、清RCC_CFGR的USBPRE[22],PLLMUL[21:18],PLLXTPRE[17],PLLSRC[16]位,使HSE不分频作为PLL的时钟输入,PLL的1.5倍频作为USB的时钟。

6、清RCC_CIR所有位,关闭全部的时钟中断。

7、置RCC_CR的HSEON[16]位,开启HSE振荡器。

8、检测RCC_CR的HSERDY[17]位来检测HSE振荡器是否准备就绪,若该位为1则接着往下配置,否则一直等待检测直到该位被硬件置1或等待检测时间结束。

9、清RCC_CFGR的HPRE[7:4]位,设置AHB预分频值使SYSCLCK不分频。

10、清RCC_CFGR的HPRE2[13:11]位,设置APB2时钟(PCLK2)不分频。

11、置RCC_CFGR的HPRE1[10:8]位为110,设置APB1时钟(PCLK1)二分频。

12、置RCC_CFGR的PLLMUL[21:18]位为0111,设置PLL9倍频输出,得到SYSCLK为72MHz。

13、置RCC_CR的PLLON[24]位,使能PLL时钟。

14、检测RCC_CR的PLLRDY[25]位,若为1表示PLL时钟锁定成功,为0表示锁定未完成,继续检测等待直到该位被硬件置1.

15、置RCC_CFGR的SW[]1:0]位为10,选择PLL输出作为系统时钟。

16、检测RCC_CFGR的SWS[3:2]位,若为10表示PLL作为系统时钟使用成功,否则一直等待直到该位为10,。

17、至此系统时钟配置全部完成。

总结系统时钟配置大体过程:

1、上电初始,开启HSI振荡器,关闭PLL及HSE,清RCC_CR及RCC_CFGR形影位为缺省值

2、开启HSE振荡器,等待HSE振荡器启动并进入稳定。

3、选择HSE作为PLL时钟输入,配置好各个预分频器相应的预分频系数。

4、启动PLL时钟,等待PLL时钟准备就绪。5、选择PLL时钟输出作为系统时钟输入。