Q1:RDCLK和WRCLK差距较大时,是否会造成multi-bit的问题?是否会造成跳过了full而full+1的状态漏过满?

A1:总结一下几点:https://zhuanlan.zhihu.com/p/22681019

1.慢时钟采快时钟会出现漏采,虽然不会出现功能错误,但是将空满新号的判断变得更为保守,效率因此会i降低。

2.由于出现漏采,快时钟的读/写指针sync到慢时钟时,gray code就不是按照1次变化1个bit的方式进行了,而是有可能一次变化好几个bit,这样gray code的好处就体现不出来了。

异步fifo需要将读写的pointer作比较产生满和空信号,但是假如fifo的两个时钟域的clk相差特别大,pointer在做跨时钟域转换的时候就会出现问题。什么问题呢?慢时钟采快时钟会漏采数据。

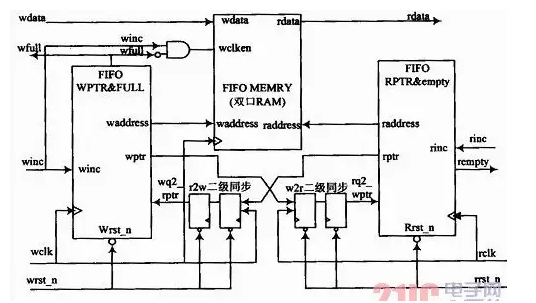

举个栗子:异步fifo,写时钟500M,读时钟100M,相差5倍。那么写时钟域的write_pointer就会以500M的频率增加,但是读时钟的read_pointer增加的频率是100M。现在要判断满和空,满是在写时钟域判断的,空是在读时钟域判断的。下图所示:

判断满的方法是拿write_pointer和做完CDC转换过来的read_pointer作比较。CDC转换的方法是采用格雷码过两级flip-flop的同步器。由于read_pointer属于100M的频率,write时钟域有500M,属于快采慢,CDC转换不会有什么问题。因此满的判断不会有问题。

判断空的方法是拿read_pointer和做完CDC转换过来的write_pointer做比较。CDC转换的方法也是采用格雷码过两级flip-flop的同步器。由于write_pointer的变化频率是500M,而read时钟域只有100M的clk,属于慢采快,CDC的转换就会出问题。

出什么问题?

因为read时钟的频率过低,所以write_pointer做完CDC之后得到的将是零星的离散的采样值,而非连续的值,比如说可能会采样到格雷码的5->10->15,而非连续的格雷码的5->6->7->8............

那么该怎么解决这个问题?

这个问题其实没法解决,也不需要解决。

为什么没法解决?

因为快时钟往慢时钟传数据,要想一个不漏,唯一的办法就是hold住(通常来讲,至少hold住目标时钟域2T,可以把HOLD理解成将信号延时)。把当前数据牢牢keep住,等到数据被取走了再传下一个。但是很明显write_pointer属于自增型的,只要fifo没有满,它都可以持续增加,并不会hold不变,所以必然会漏采。

为什么不需要解决?

因为只要fifo够大,即便读到的write_pointer是离散的,也不会影响到fifo判空。只要fifo判空不出错,异步fifo的行为就没有问题,只不过效率可能略微降低

举个栗子:

当read时钟域采样到write_pointer的值是5的时候,真正的write_pointer的值可能是多少?可能已经是5,6,7,8,9等等了。但绝对不可能比5小。

为什么不可能比5小?

因为对于write_pointer而言,它从4变到5,这个沿变在跨CDC的时候,只有没采着和采着两种可能,没采着的话,跨完时钟域得到4,采着了就得到5。绝对不可能得到比5大的值。

也就是说,只要是格雷码跨CDC,跨过去的值只可能比真实值相等或者小,不可能比真实值大!

所以如果在read时钟域已经看到write_pointer等于5了,那么真实的write_pointer必然不小于5。那么基于write_pointer等于5来判断空,将会得到一个很保守的空(也可以叫假空)!也就是说异步fifo明明还有数,读时钟域就判断出空,暂时停止读取数据。

但是这并不会导致出错,因为这种保守的空判断,只是降低了读的效率(因为提前会判断成读空,所以就停止了读,如果不提前停止,还能再读几个数据,所以效率降低了),并没有导致读出错误的数据或者不存在的数据。

所以,即便采样到的write_pointer是个离散值,但是由于异步fifo并不会有实际的行为出错,所以也不需要解决这个问题。

Q2: 亚稳态真的消除了吗?如果真的出现亚稳态,你的FIFO还能用吗?http://www.cnblogs.com/skyworks/p/5928398.html

A2: 通过使用格雷码,我们可以降低亚稳态出现的可能性,但是不能说是真的消除了。 如果出现亚稳态,FIFO还是能够继续使用,原因很简单:举个列子,写快读慢,我们来看看full信号的产生,只有当读地址变化的时候(触发器的输入变化的时候才会出现亚稳态,而且由于是慢到快,就算出现亚稳态,因为相邻位的格雷码每次只有一位变化,这个出错结果实际上也就是读指针没有跳变保持不变,),亚稳态才会产生,这个时侯意味着我又读了一个数据,所以即使传递过去后产生了full信号,也没有出现溢出的问题,因为传递的时候读是至少又读了一个数据的。(由快到慢就跟不会出现读空了,写地址同步过去的时候也会写好几次,)

在涉及到触发器的电路中,亚稳态无法彻底消除,只能想办法将其发生的概率将到最低。其中的一个方法就是使用格雷码。格雷码在相邻的两个码元之间只由一位变换(二进制码在很多情况下是很多码元在同时变化)。这就会避免计数器与时钟同步的时候发生亚稳态现象。但是格雷码有个缺点就是只能定义2^n的深度,而不能像二进制码那样随意的定义FIFO的深度,因为格雷码必须循环一个2^n,否则就不能保证两个相邻码元之间相差一位的条件,因此也就不是真正的格雷码了。第二就是使用冗余的触发器,假设一个触发器发生亚稳态的概率为P,那么两个级联的触发器发生亚稳态的概率就为P的平方。但这会导致延时的增加。亚稳态的发生会使得FIFO出现错误,读/写时钟采样的地址指针会与真实的值之间不同,这就导致写入或读出的地址错误。由于考虑延时的作用,空/满标志的产生并不一定出现在FIFO真的空/满时才出现。可能FIFO还未空/满时就出现了空/满标志。这并没有什么不好,只要保证FIFO不出现overflow or underflow 就OK了。

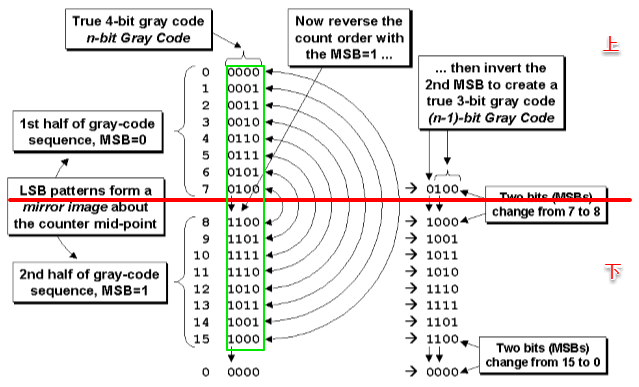

Q3:格雷码的轴对称问题

A3:

1.镜像对称的原因是为了每一个相邻的变化都是只有1bit,为了满足0000(0)和1000(15)也只有1bit发生变化。

2.格雷码地址直接比较去判断写满读空,

当最高位和次高位相同,其余位相同认为是读空

当最高位和次高位不同,其余位相同认为是写满

3.格雷码地址直接当作RAM的地址,由于格雷码递增时都是唯一的,虽然在RAM里时散乱的排布,但是依旧可以正确存储

因为格雷码是镜像对称的,若只根据最高位是否相同来区分是读空还是写满是有问题的,详情我会慢慢说,请看图 1

绿色框起来的是0--15的格雷码,用红线将格雷码分为上下两部分

通过观察格雷码相邻位每次只有1位发生变化,且上下两部分,除了最高位相反,其余位全都关于红线镜像对称,

7 --> 8 ,格雷码从 0100 --> 1100 ,只有最高位发生变化其余位相同

6 --> 9 , 格雷码从 0101 --> 1101 , 只有最高位发生变化其余位相同

以此类推,为什么要说镜像对称呢?

试想如果读指针指向 8,写指针指向 7 ,我们可以知道此时此刻并不是读空状态也不是写满状态

但是如果在此刻套用理论 1 来判断,看会出现什么情况,我们来套一下

7的格雷码与8的格雷码的最高位不同,其余位相同,所以判断出为写满。这就出现误判了,同样套用在 6 和 9,5 和 10等也会出现误判。

因此用格雷码判断是否为读空或写满时应使用理论 2,看最高位和次高位是否相等,具体如下:

当最高位和次高位相同,其余位相同认为是读空

当最高位和次高位不同,其余位相同认为是写满

补:理论2这个判断方法适用于用格雷码判断比较空满

在实际设计中如果不想用格雷码比较,就可以利用格雷码将读写地址同步到一个时钟域后再将格雷码再次转化成二进制数再用理论1进行比较就好了。。

图 1

附几个FIFO的问题:

例如:

-

异步FIFO,如何做到适配不同时钟域。简单例子,10m工作时钟写数20m时钟读,与10m时钟写数100m时钟读数的区别是什么。(可能深度上有变化)

-

读写地址使用格雷码,格雷码编码解码,如果不用格雷码可能出现的问题,以及原因。(相邻格雷码只变化一位,降低了亚稳态出现的可能性)

-

如果该异步FIFO是用来作为存储以包为单位的数据,是否可以添加一些逻辑,控制错包,或者是如何处理,将错包抛弃。(通过上位机对写使能的判断,来实现错包抛弃)

-

如果异步FIFO有数据位转换功能,32b的数据入16b数据出,该怎么处理。(下位机,完全可以两个时钟产生一个读使能给FIFO,这样就解决了)

异步FIFO一些要点:

-

格雷码的轴对称问题。

-

为何用格雷码而非二进制码做CDC。

-

异步FIFO的大致框图。

-

满空信号产生。尤其是满。

-

RDCLK和WRCLK差距较大时,是否会造成multi-bit的问题。

-

是否会造成跳过了full而full+1的状态漏过满。

异步fifo的时序约束也是非常麻烦的,不要认为整个格雷码跨时钟域就可搞定,而且是可靠的,那是理想情况,实际的情况每bit延时都是不一样的,会给时序造成很大困扰。