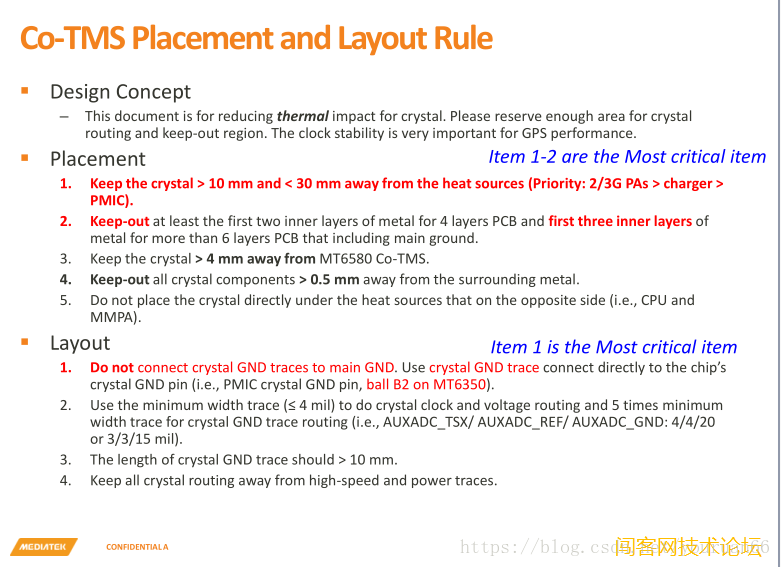

协同TMS布局与布局规则

设计理念

这个文件是为了减少晶体的热冲击。请保留足够的晶体面积

路由和保持区域。时钟稳定性对GPS性能有着重要的影响。

放置位置

1。保持晶体> 10毫米和30毫米远离热源(优先:2 /3G PAS >充电器>

PMIC)。

2。至少保留前两层金属层,用于4层PCB和前三层内层。

金属包括6层PCB,包括主接地。

三。保持晶体>4毫米远离MT65 80 CO TMS。

4。将所有晶体成分保持在离周围金属0.5毫米处。

5。不要将晶体直接放置在相反侧的热源之下(即CPU和

MMPA)。

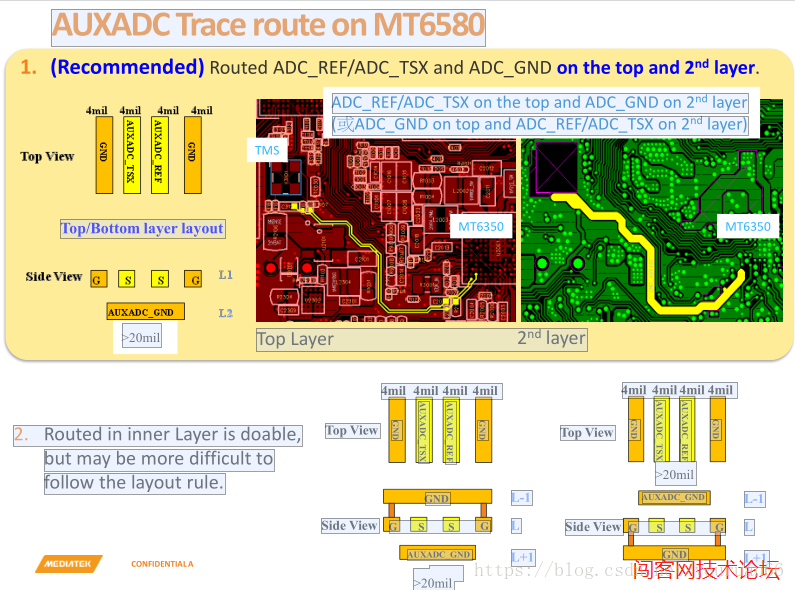

布局图

1。不要将晶体GND轨迹连接到主GND。使用水晶GND轨迹直接连接到芯片

晶体GND引脚(即,PMIC晶体GND引脚,球B2上MT6350)。

2。使用最小宽度跟踪(小于4密耳)进行晶体时钟和电压路由,最小5倍

晶体GND跟踪路由的宽度跟踪(即AuxADCKTSX/AUXADCYREF/AUXADCKGND:4/4/20)

或3/3/15密耳。

三。晶体GND轨迹长度应大于10 mm。

4。保持所有晶体路由远离高速和功率跟踪。

TCXO布局布局规则

重要的

这个文件是为了减少晶体的热冲击。请保留足够的晶体面积

路由和保持区域。时钟稳定性对GPS性能有着重要的影响。

放置位置

-保持晶体>10毫米远离热源(即2/3G PAs、充电器和PMIC)。

-至少保留前两层金属层,用于4层PCB和至少第一三层内部。

6层PCB的金属层,包括主接地。

-保持晶体从MT65 80离开4毫米。

-将所有晶体成分保持在离周围金属0.5毫米处。

-不要将晶体直接放置在相反侧的热源之下(即CPU和

MMPA)。

布局图

-使用最小宽度迹线(小于4密耳)进行所有晶体布线(即电压、时钟和GND迹线)。

-不要将晶体GND轨迹连接到主GND。使用水晶GND轨迹直接连接到芯片

晶体GND引脚(即,ConSys)。芯片,收发器或PMIC晶体GND引脚。

晶体GND的长度应大于10毫米。

-保持所有晶体路由远离高速和功率跟踪。