一、中断体系结构

1)ARM体系CPU的7种工作模式

①:7种工作模式:

A、用户模式(usr):ARM处理器正常的程序执行状态

B、快速中断模式(fiq):用于高速数据传输或通道处理

C、中断模式(irq):用于通用的中断处理

D、管理模式(svc):操作系统使用的保护模式

E、数据访问终止模式(abt):当数据或指令预取终止时进入改模式,可用于 虚拟存储及存储保护

F、系统模式(sys):运行具有特权的操作系统任务

G、未定义指令中断模式(und):当未定义的指令执行时进入该模式,可用于 支持硬件协处理器的软件仿真

②可通过软件来进行模式切换,或者发生各类中断、异常时CPU自动进入相应模式,除用户模式外,其他6种模式都属于特权模式,大多程序运行于用户模式,进入特权模式是为了处理中断、异常,或访问被保护的系统资源

③ARM体系的CPU有两种工作状态:

A、ARM状态:处理器执行32位字对齐ARM指令

B、Thumb状态:执行16位半字对齐的Thumb指令

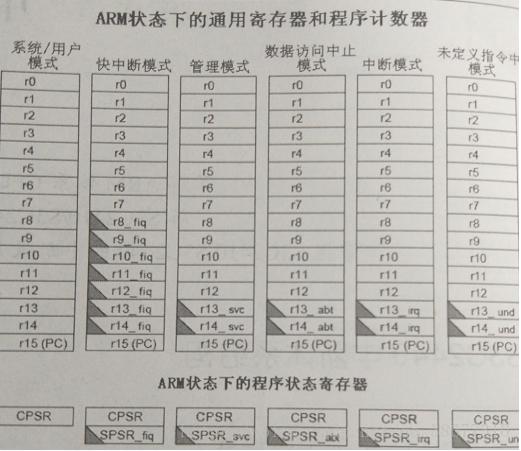

④ARM920T有31个通用的32位寄存器和6个程序状态寄存器

⑤

R0---R15可直接访问,除R15外都是通用寄存器,即可以保存数据也可以保存地址

R13---R15稍有特殊:

R13:栈指针寄存器,保存栈指针

R14:程序连接寄存器

R15:程序计数器 (pc)

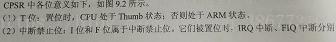

⑥CPSR(Current Program Status Regsiter)当前程序状态寄存器

其中一些位被用于标识各种状态、处于什么模式

各个位的意义:

⑦SPSR(Saved Process Status Registers)程序状态保留寄存器

当切换工作模式时,SPSR中保存前一个工作模式的CPSR值,当返回前一个工作模式时,可以将SPSR的值恢复到CPSR 中。

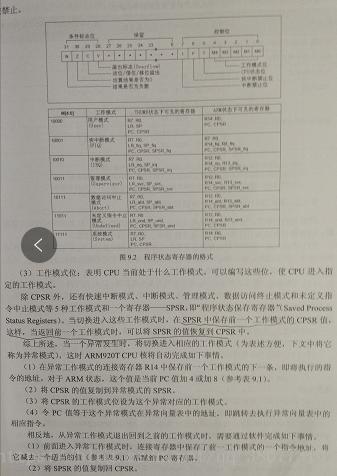

⑧切换进入异常模式时,CPU自动完成如下事情:

A、在异常模式下的连接寄存器R14中保存前一个工作模式的下一条即将执行的指令的地址,对于ARM状态,这个值是当前 PC值加4或加8.

B、将CPSR复制到异常模式下的SPSR。

C、将CPU的工作模式位设为这个异常对应的工作模式。

D、令PC值等于这个异常模式在异常向量表中的地址,即跳转去执行异常向量表中的相应指令

⑨相反地,从异常工作模式退出回到之前工作模式时,完成如下:

A、连接寄存器中保存了前一工作模式的一个指令地址,将它减去一个适当的值后赋给PC寄存器。

B、将SPSR的值复制回CPSR。

2)S3C2440中断控制器

①如何知道各类外设发生了不预期事件:

A、查询法:反复查询设备状态,并作出反应。占用CPU资源过多,不适合多任务系统。

B、中断法:CPU通过查看相应寄存器,执行相应操作。

②中断处理过程:

A、中断控制器汇集各类外设发出的中断信号,然后告诉CPU

B、CPU保存当前程序运行环境,调用中断服务程序(ISR:Interrupt Service Routine)来处理中断。

C、在ISR识别是哪种中断,并进行处理

D、清除中断

E、恢复被中断程序的运行环境,继续执行

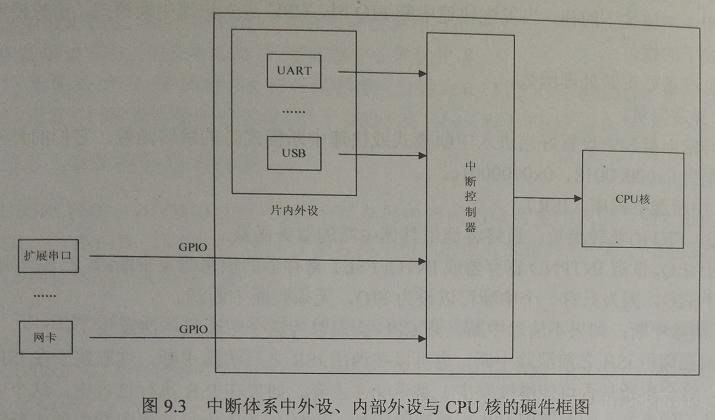

③中断体系硬件框图:

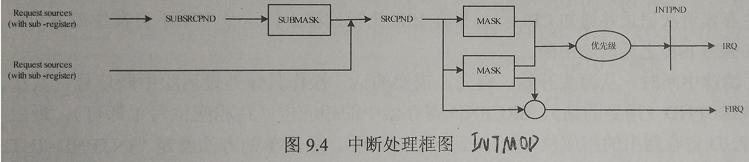

④中断处理框图:

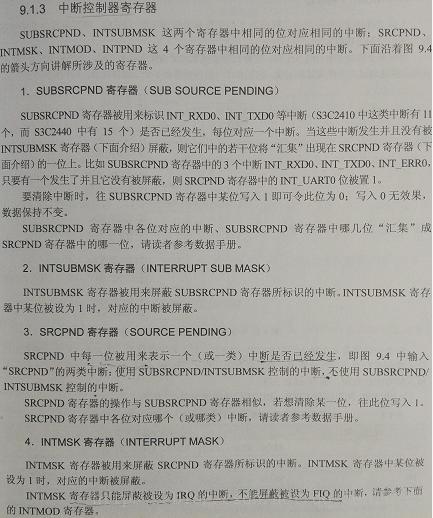

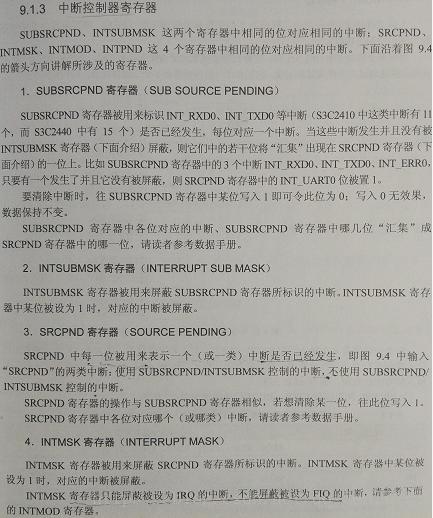

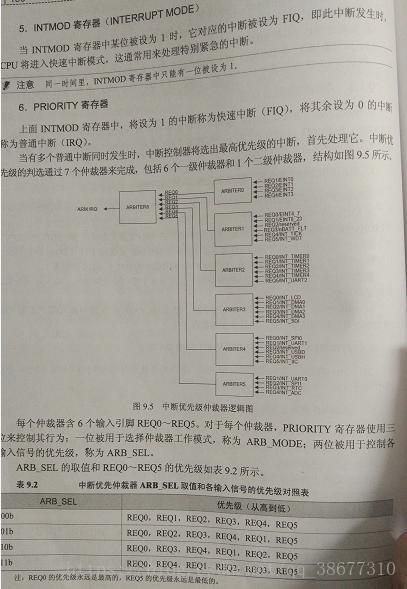

3)中断控制寄存器