网上搜了些资料,碍于智商和基础,看不懂,

只有将S5PV210 数据手册关于I2C的部分,翻译记录下,留到以后用。

1.OVERVIEW

The S5PV210 RISC microprocessor supports four multi-master I2C bus serial interfaces. To carry information between bus masters and peripheral devices connected to the I2C bus, a dedicated Serial Data Line (SDA) and an Serial Clock Line (SCL) is used. Both SDA and SCL lines are bi-directional.

210支持4个多主I2C串行接口。为了在主设备和从设备之间传输数据,需要使用一个专用的串行数据线和一个串行时钟线。SDA和SCL都是双向传输的。

In multi-master I2C-bus mode, multiple S5PV210 RISC microprocessors receive or transmit serial data to or from slave devices. The master S5PV210 initiates and terminates a data transfer over the I2C bus. The I2C bus in the S5PV210 uses a standard bus arbitration procedure.

在多主I2C总线模式中,多个210处理器接受或发送数据和从设备。主设备210开始和结束数据的发送在I2C总线上。I2C总线在210上使用一个标准的总线仲裁程序。

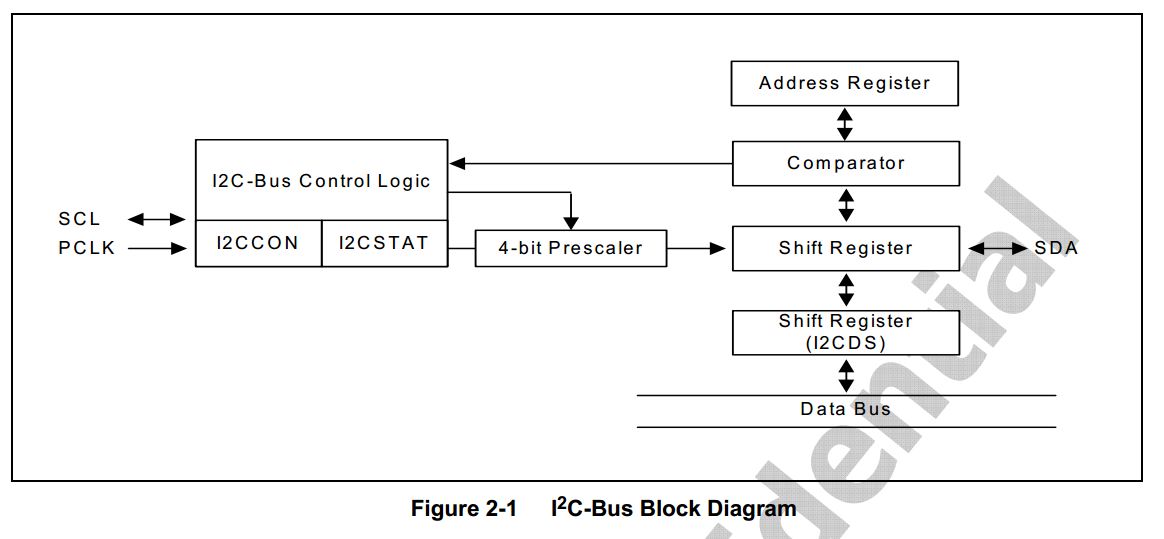

To control multi-master I2C-bus operations, values must be written to the following registers: • Multi-master I2C-bus control register- I2CCON • Multi-master I2C-bus control/status register- I2CSTAT • Multi-master I2C-bus Tx/Rx data shift register- I2CDS • Multi-master I2C-bus address register- I2CADD

为了使用I2C操作,下面的寄存器必须被写:

控制寄存器——I2CCON

控制/状态寄存器——I2CSTAT

输出/接受 移位寄存器——I2CDS

地址寄存器——I2CADD

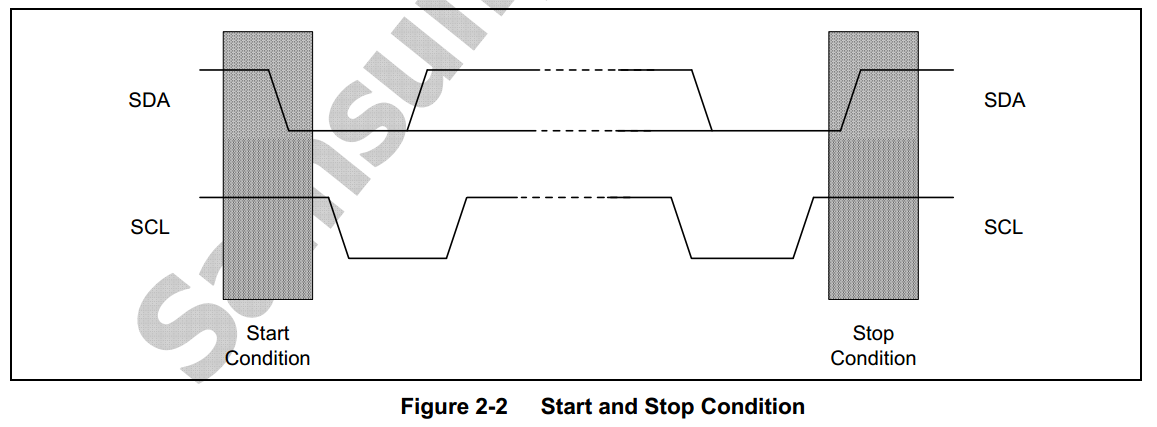

If the I2C-bus is free, both SDA and SCL lines should be both at High level. A High-to-Low transition of SDA initiates a Start condition. A Low-to-High transition of SDA initiates a Stop condition while SCL remains steady at High Level.

如果I2C总线是空闲的,那么SDA和SCL都应该处于高电平。SDA从高到低的转换发出一个开始条件。当SCL维持稳定的高电平时,SDA低到高变化发出一个停止信号。

The master device always generates Start and Stop conditions. First 7-bit address value in the data byte that is transferred via SDA line after the Start condition has been initiated, can determine the slave device which the bus master device has selected. The 8th bit determines the direction of the transfer (read or write).

主设备控制开始和结束。在起始信号之后,刚开始的7个bit表示地址值,通过SDA传输,用来确定从设备。第8bit确定传输的方向(读/写)

Every data byte put onto the SDA line should be eight bits in total. There is no limit to send or receive bytes during the bus transfer operation. Data is always sent from most-significant bit (MSB) first, and every byte should be immediately followed by acknowledge (ACK) bit.

所有放到SDA的字节数据都应该总共使用8bit表示。在总线转移操作期间,传输和接受字节没有限制。数据总是从最重要的字节开始发送,每字节数据后应该立即有ACK。

2.KEY FEATURES OF IIC-BUS INTEFACE

• Four channel Multi-Master, Slave I2C BUS interfaces (One channel for HDMI PHY is internally connected. Three channels can be used for general purpose. However, if the user wants to use HDMI, it is recommended to allocate one channel for HDMI use only among three channels) • 7-bit addressing mode • Serial, 8-bit oriented, and bidirectional data transfer • Supports up to 100kbit/s in the Standard mode • Supports up to 400kbit/s in the Fast mode. • Supports master transmit, master receive, slave transmit and slave receive operation • Supports interrupt or polling events

四个I2C接口(一个通道被内部连接,三个可以用于一般目的。然而,如果要使用HDMI,推荐在三个通道中分配一个用于HDMI)

7bit地址模式

串行,8bit单线,双向数据传输

支持主发送,主接受,从发送,从接受

支持中断、轮询

3.IIC-BUS INTERFACE OPERATION

The S5PV210 I2C-bus interface has four operation modes, namely: • Master Transmitter Mode • Master Receive Mode • Slave Transmitter Mode • Slave Receive Mode The functional relationships among these operating modes are described below

210 I2C 有四种操作模式,

主发送

主接受

从发送

从接受

这些模式的功能关系如下

5. START AND STOP CONDITIONS

If the I2C-bus interface is inactive, it is usually in Slave mode. In other words, the interface should be in Slave mode before detecting a Start condition on the SDA line (a Start condition is initiated with a High-to-Low transition of the SDA line while the clock signal of SCL is High). If the interface state is changed to Master mode, SDA line initiates data transfer and generates SCL signal.

如果I2C处于空闲,那么通常处于从模式。换句话,接口在检查到起始信号前应该处于从模式(当SCL处于高时,起始信号通过SDA高变低发出)。如果接口状态被改变成主模式,

SDA线发出数据,并产生SCL信号

A Start condition transfers one-byte serial data via SDA line, and a Stop condition terminates the data transfer. A Stop condition is a Low-to-High transition of the SDA line while SCL is High. The master generates Start and Stop conditions. The I2C-bus gets busy if a Start condition is generated. On the other hand, a Stop condition frees the I2C-bus.

一个起始信号后传输一个字节的串行数据通过SDA线,一个停止信号后数据传输结束。停止信号表现为SDA高变低,当SCL处于高时。主设备产生起始和停止信号。

如果起始信号参数,那么I2C总线处于忙状态。另一方面,停止信号后I2C处于空闲状态

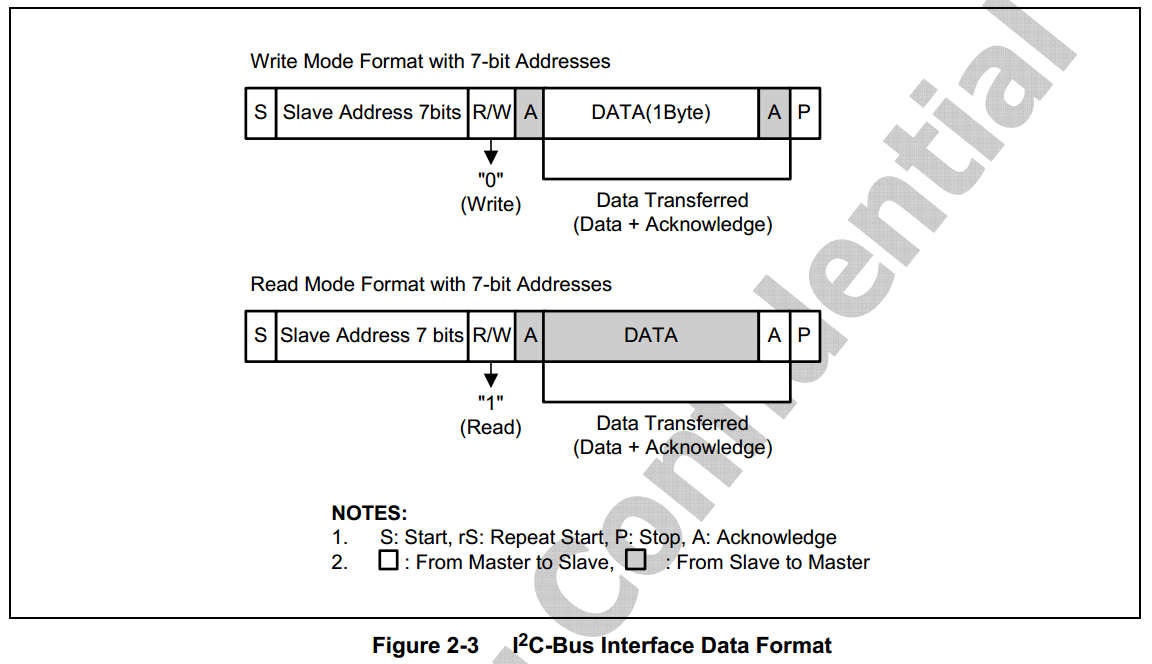

If a master initiates a Start condition, it should send a slave address to notify the slave device. One byte of address field consists of a 7-bit address and a 1-bit transfer direction indicator (that shows write or read). If bit 8 is 0, it indicates a write operation (Transmit Operation); if bit 8 is 1, it indicates a request for data read (Receive Operation).

如果主设备要发出一个开始信号,他需要传送一个从设备地址通知从设备。一个字节长度的地址域,包含7bit的地址和1bit的传输方向(表示读/写).

如果第8bit为0,则表示写操作,如果为1,表示读操作。

The master transmits Stop condition to complete the transfer operation. If the master wants to continue the data transmission to the bus, it should generate another Start condition as well as a slave address. In this way, the read-write operation is performed in various formats.

主设备发送停止信号表示传输完成。如果主设备想继续传输数据,他应该产生其他的起始信号以及从设备地址。这样,读写操作以各种方式执行。

6.DATA TRANSFER FORMAT

Every byte placed on the SDA line should be eight bits in length. There is no limit to transmit bytes per transfer. The first byte following a Start condition should have the address field. If the I2C-bus is operating in Master mode, master transmits the address field. Each byte should be followed by an acknowledgement (ACK) bit. The MSB bit of the serial data and addresses are sent first.

SDA上的字节长度应该为8bit。每一次传输,传输的字节们都没有限制。第一个字节紧跟在起始位后,并且有地址域。如果I2C处于主模式,主设备传输地址域。

每个字节之后应跟着一位ACK.串行数据的MSB和地址是首先被传输的。

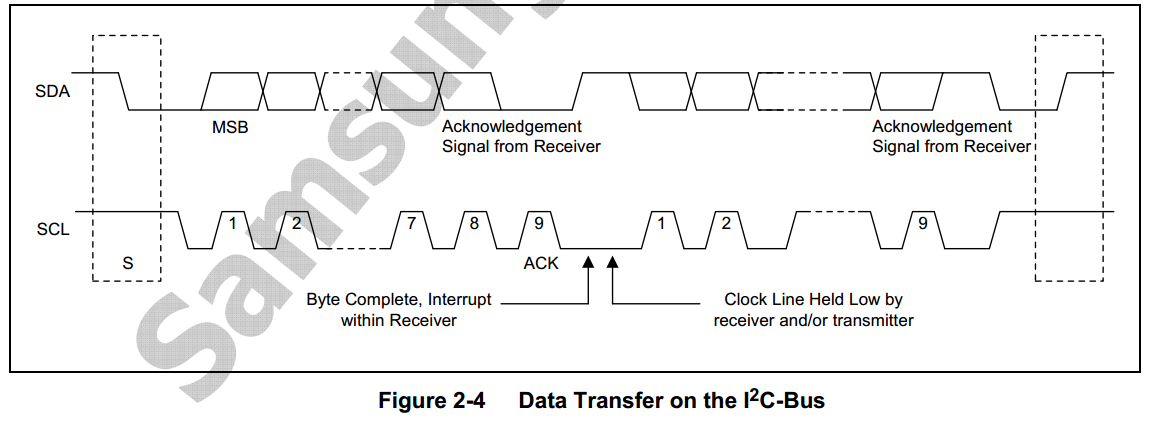

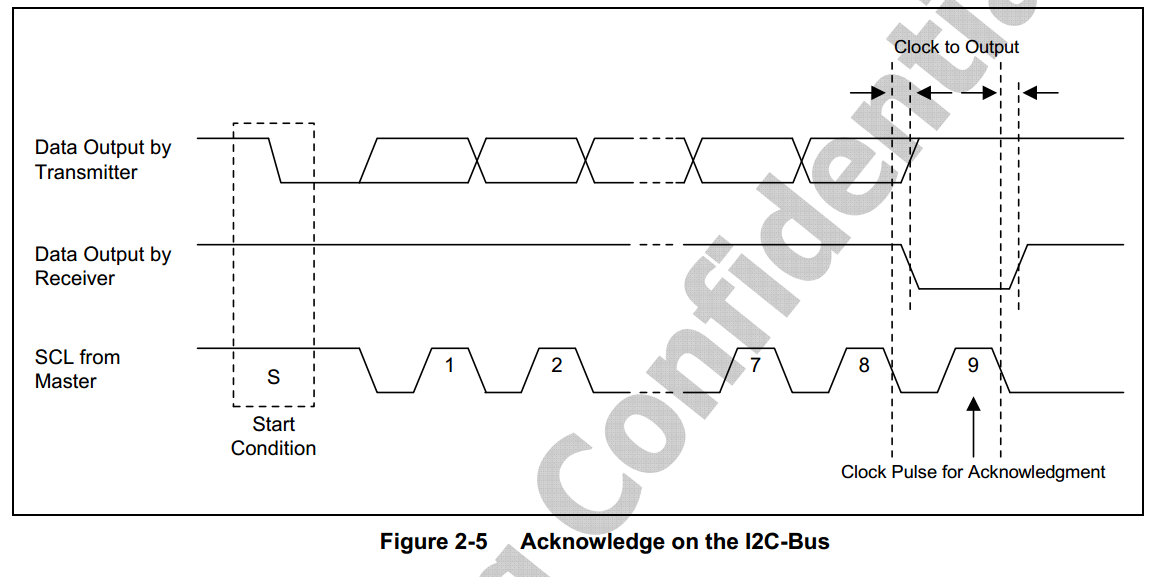

7.ACK SIGNAL TRANSMISSION

To complete a one-byte transfer operation, the receiver sends an ACK bit to the transmitter. The ACK pulse occurs at the ninth clock of the SCL line. Eight clocks are required for the one-byte data transfer. The master generates clock pulse required to transmit the ACK bit.

接收者发送一个ACK给传输这,表示完成一字节的传输操作。ACK脉冲发生在第九个SCL时钟处。第八个时钟被接受,为了一字节数据的传输。

主设备产生的时钟脉冲被接受用于传输ACKbit。

The transmitter sets the SDA line to High to release the SDA line if the ACK clock pulse is received. The receiver drives the SDA line Low during the ACK clock pulse so that the SDA keeps Low during the High period of the ninth SCL pulse. The software (I2CSTAT) enables or disables ACK bit transmit function. However, the ACK pulse on the ninth clock of SCL is required to complete the one-byte data transfer operation.

如果ACK时钟脉冲被接受,那么发送者拉高SDA来表示释放SDA。在ACK时钟脉冲期间,接收者驱动SDA拉低,因此,SDA本应该在SCL的第九个脉冲时期保持高 ,

但却保持低。软件方式(I2CSTAT)可以使能或禁止ACKbit传输功能。然而,在SCL的第九个脉冲时需要ACK脉冲用来表示一个字节数据传输操作完成。

8.READ-WRITE OPERATION

In data is transmitted in Transmitter mode, the I2C-bus interface waits until I2C-bus Data Shift (I2CDS) register receives the new data. Before the new data is written to the register, the SCL line is held low. The line is only released after the data has been written. S5PV210 holds the interrupt to identify the completion of current data transfer. After the CPU receives the interrupt request, it writes new data to the I2CDS register again.

当数据被传输完后,并处于发送模式,I2C接口会进行等待状态,直到I2C数据移位寄存器(I2CDS)收到新的数据。在新数据被写到寄存器之前,SCL保持低。

当数据被写完后,SCL才被释放。S5PV210使用中断来确定当前数据传输完成。CPU收到中断请求后,他会再次写新的数据到I2CDS寄存器。

If data is received in Receive mode, the I2C-bus interface waits until I2CDS register is read. Before the new data is read out, the SCL line is held low. The line is only released after the data has been read. S5PV210 holds the interrupt to identify the completion of new data reception. After the CPU receives the interrupt request, it reads the data from the I2CDS register.

当处于接受模式,数据被接受完后,I2C接口会进入等待模式,直到I2CDS寄存器被读。在新的数据被读出前,SCL会保持低。只有当数据已经被读后,SCL才被释放。

S5PV210使用中断取识别新数据接受完成。在CPU接受到中断请求后,他会从I2CDS寄存器中读数据。