模块(Module)从输入端口(input ports)接收输入,经过内部实现的转换逻辑,从输出端口(output ports)输出。

在Chisel3中,模块的输入输出端口,通过IO(new Bundle{...})的形式定义,其中定义了各种类型的数据变量。在实现模块内部转换逻辑的时候,也需要使用到各种类型的数据变量。这些变量如何加入到hardware graph中呢?就是通过WireBinding和RegBinding等。

1. WireBinding

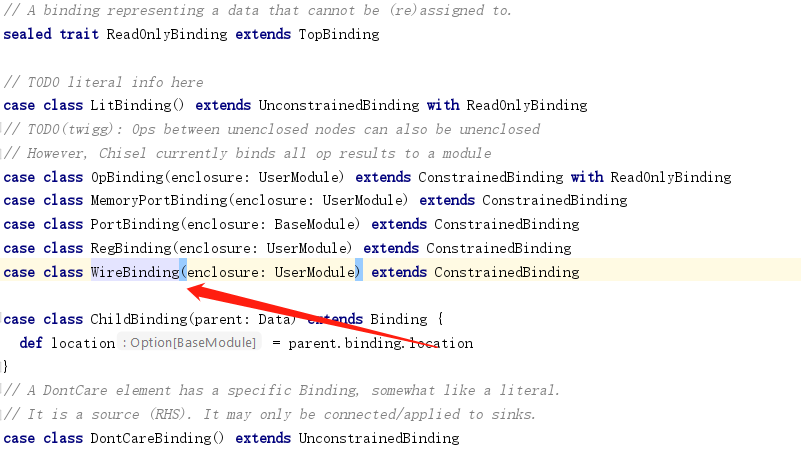

定义如下:

case class WireBinding(enclosure: UserModule) extends ConstrainedBinding

a. Wire()

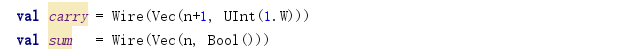

通过Wire()对一个变量进行Wire绑定,实例如下:

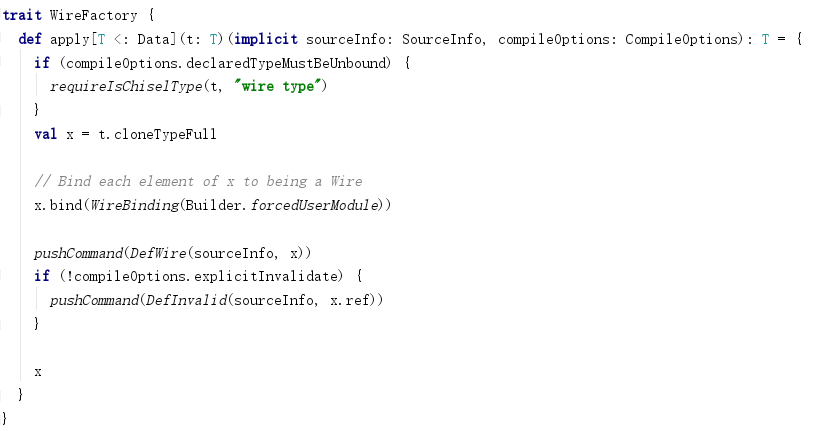

Wire继承自WireFactory:

object Wire extends WireFactory

b. WireFactory

a. 生成一个t的克隆x;

b. 对x进行绑定:x.bind(WireBinding(Builder.forcedUserModule))

c. 绑定的对象为WireBinding:WireBinding(Builder.forcedUserModule)

d. Builder.forcedUserModule可以理解为当前模块;

2. RegBinding

定义如下:

case class RegBinding(enclosure: UserModule) extends ConstrainedBinding

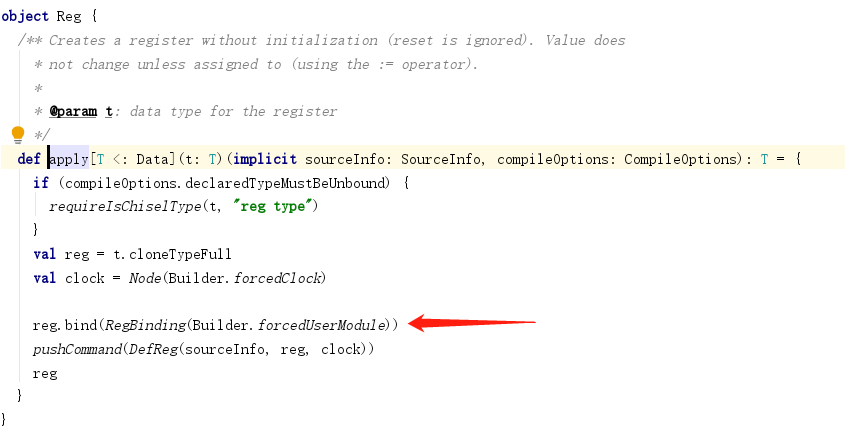

a. Reg()

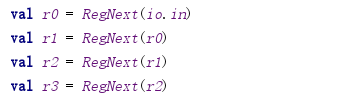

通过Reg()对变量进行寄存器绑定,实例如下:

a. 生成一个t的可能reg;

b. 对reg进行绑定:reg.bind(RegBinding(Builder.forcedUserModule))

c. 绑定的对象为RegBinding: RegBinding(Builder.forcedUserModule)

d. Builder.forcedUserModule可以理解为当前模块;

3. MemPortBinding

Mem中的每一个元素,在使用时都会使用MemPortBinding进行绑定。

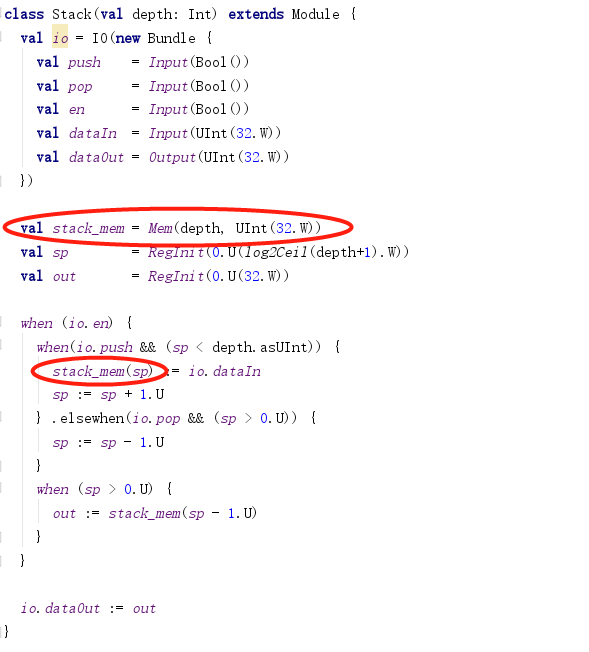

a. 使用实例如下:

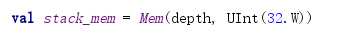

b. 创建Mem()时并不会绑定

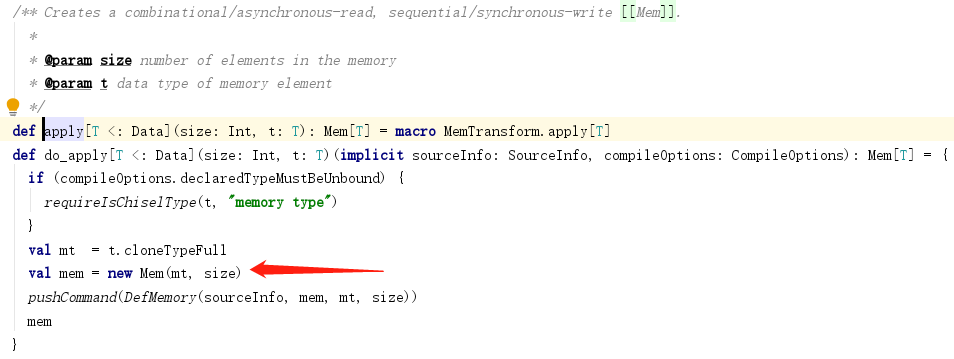

Mem()调用实现如下:

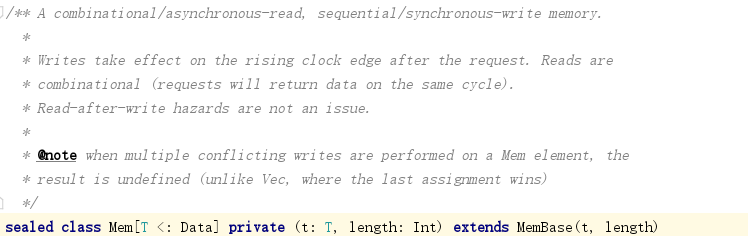

Mem类继承自MemBase:

MemBase在创建时并不会进行绑定;

c. 使用时进行绑定

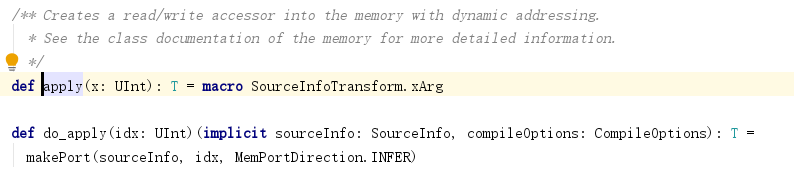

如:stack_mem(sp) := io.dataIn 中,stack_mem(sp)会调用方法:

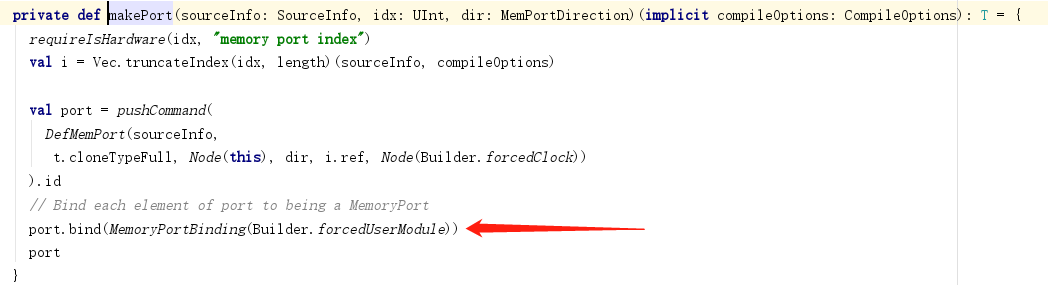

进而调用makePort进行绑定: