3.3 数据和控制接口

数据和控制界面使您可以访问nRF24L01 +中的所有功能。数据和控制接口由以下六个5V容差数字信号组成:

•IRQ(该信号低电平有效并由三个可屏蔽中断源控制)

•CE(该信号高电平有效,用于在RX或TX模式下激活芯片)

•CSN(SPI信号)

•SCK(SPI信号)

•MOSI(SPI信号)

•MISO(SPI信号)

使用1字节SPI命令,您可以在所有操作模式下激活nRF24L01 +数据FIFO或寄存器映射。

3.3.1 特性

•用于快速访问最常用功能的特殊SPI命令

•0-10Mbps 4线SPI

•8位指令集

•轻松配置寄存器映射

•TX和RX方向均为全三级FIFO

3.3.2 功能描述

SPI是一个标准SPI,最高数据速率为10Mbps。

3.3.3 SPI操作

本节介绍SPI命令和时序。

3.3.3.1 SPI命令

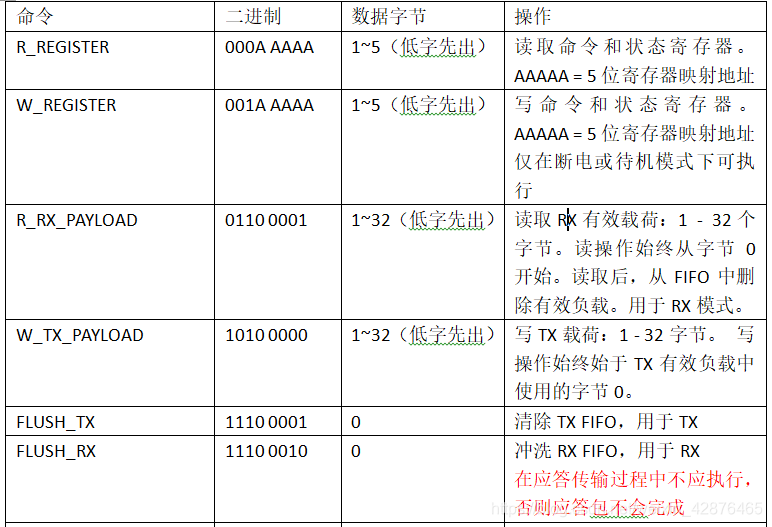

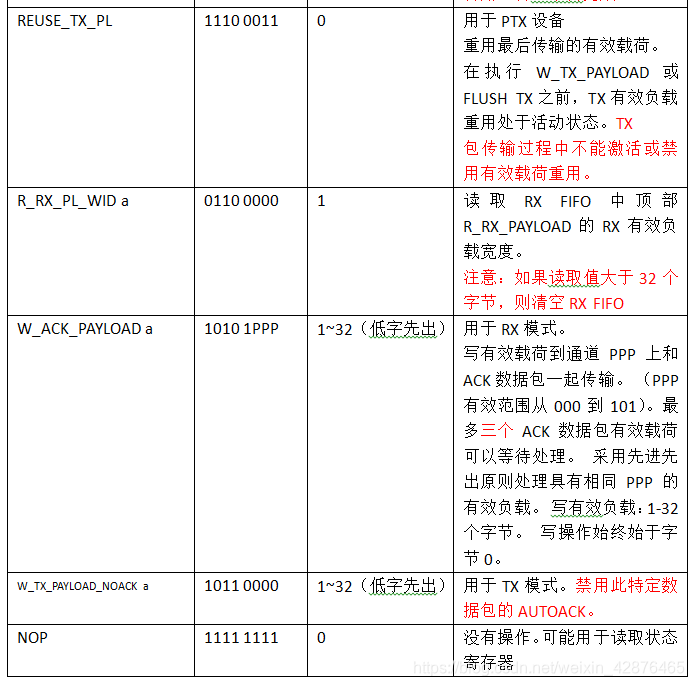

SPI命令如表20所示。每个新命令都必须在CSN上由高到低转换启动(译者注:其实就是有未选定器件(CSN为高电平)设置为选定器件(CSN为低电平),也就说每一条指令的执行代码都需要先选择器件,再不选定器件,不可以一直选定器件)。

STATUS寄存器在MISO引脚上串行移出,同时SPI命令字移入MOSI引脚。

串行移位SPI命令采用以下格式:

<命令字:MSBit到LSBit(一个字节)>

<数据字节:LSByte到MSByte,每个字节中的MSBit优先>

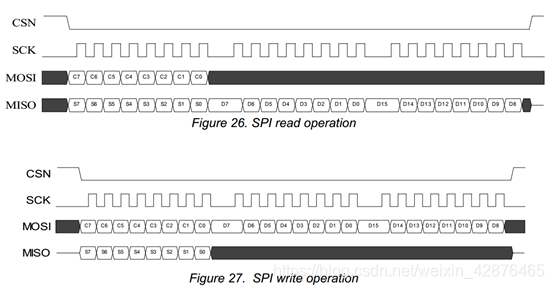

有关时序信息,请参见第52页上的图26.和第52页上的图27.。

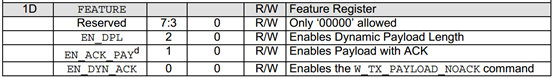

a.必须设置第62页的表28中所示的FEATURE寄存器中的位

W_REGISTER和R_REGISTER命令在单字节或多字节寄存器上运行。访问多字节寄存器时,首先读取或写入LSByte的MSBit。您可以在写入多字节寄存器中的所有字节之前终止写入,并保持未写入的MSByte不变。例如,可以通过向RX_ADDR_P0寄存器写入一个字节来修改RX_ADDR_P0的LSByte。状态寄存器的内容在CSN从高到低转换后总是读到MISO。

注:STATUS寄存器中的3位通道信息在IRQ引脚高电平至低电平转换期间更新。如果在IRQ引脚从高到低转换期间读取STATUS寄存器,则管道信息不可靠。

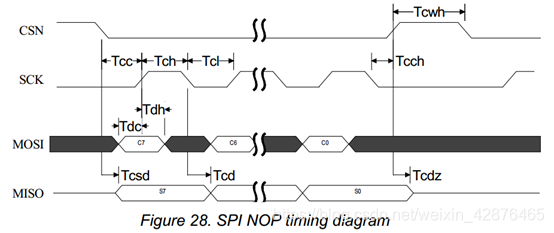

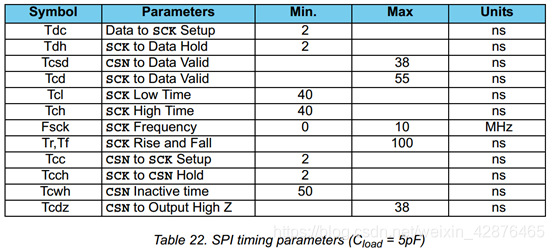

3.3.4 SPI时序

SPI操作和时序如图26至图28以及表22至表27所示。在写入配置寄存器之前,nRF24L01 +必须处于待机或掉电模式。

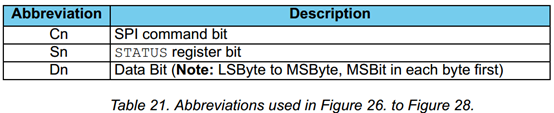

在图26至图28中,使用了以下缩写:

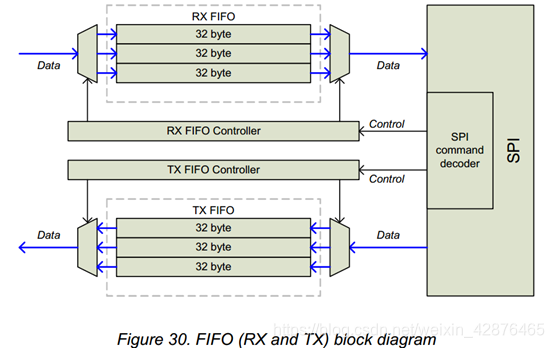

3.3.5 数据FIFO

数据FIFO存储已发送的有效负载(TX FIFO)或已准备好接收的有效负载(RX FIFO)。 FIFO可在PTX模式和PRX模式下访问。

以下FIFO存在于nRF24L01 +中:

•TX三级,32字节FIFO

•RX三级,32字节FIFO

两个FIFO都有一个控制器,可以通过SPI使用专用的SPI命令进行访问。PRX中的TX FIFO可以将ACK数据包的有效载荷存储到三个不同的PTX设备。如果TX FIFO包含多个到一个通道的有效负载,则使用先进先出原则处理有效负载。**如果所有挂起的有效载荷都发送到与PTX的链路丢失的管道,则PRX中的TX FIFO将被阻塞。**在这种情况下,MCU可以使用FLUSH_TX命令刷新TX FIFO。

PRX中的RX FIFO可以包含来自多达三个不同PTX设备的有效载荷,并且PTX中的TX FIFO最多可以存储三个有效载荷。

您可以使用这三个命令写入TX FIFO:PTX模式下的W_TX_PAYLOAD和W_TX_PAYLOAD_NO_ACK以及PRX模式下的W_ACK_PAYLOAD。所有这三个命令均可访问TX_PLD寄存器(有关该寄存器的详细信息,请参见第63页上的表28)。

RX FIFO可以通过PTX和PRX模式下的命令R_RX_PAYLOAD读取。该命令提供对RX_PLD寄存器的访问。

如果MAX_RT IRQ有效,PTX中TX FIFO中的有效载荷不会被移除。

您可以读取FIFO_STATUS寄存器中的TX和RX FIFO是满的还是空的。

3.3.6 中断

nRF24L01 +有一个低电平有效中断(IRQ)引脚。当状态机在STATUS寄存器中设置TX_DS IRQ,RX_DR IRQ或MAX_RT IRQ为高电平时,IRQ引脚被激活。当MCU向STATUS寄存器的IRQ源位写’1’时,IRQ引脚复位。CONFIG寄存器中的IRQ掩码用于选择允许断言IRQ引脚的IRQ源。通过设置其中一个MASK位为高电平,相应的IRQ源被禁止。 默认情况下,所有IRQ源都启用。

注:STATUS寄存器中的3位通道信息在IRQ引脚高电平至低电平转换期间更新。如果在IRQ引脚从高到低转换期间读取STATUS寄存器,则通道信息不可靠。

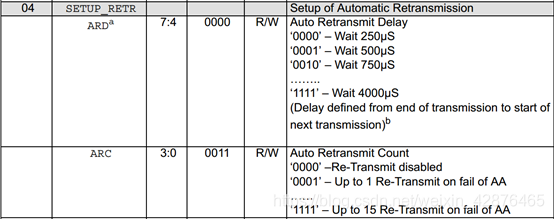

a.设置此参数时请小心。如果在2Mbps模式下ACK载荷大于15字节,则ARD必须为500μS或更多,如果在1Mbps模式下ACK载荷超过5字节,则ARD必须为500μS或更多。在250kbps模式下(即使有效负载不在ACK中),ARD必须为500μS或更高。有关更多信息,请参阅第33页上的第7.4.2节。

b.这是PTX在重新发送之前等待ACK分组的时间。 PTX处于RX模式250μs(250kbps模式下500μs)等待地址匹配。如果检测到地址匹配,则除非经过ARD,否则它会一直处于接收模式,直到数据包结束。然后它进入待机-II模式,用于指定ARD的其余部分。在ARD之后,它进入TX模式,然后重新发送数据包。

c. RX_DR IRQ由新的数据包到达事件声明。处理该中断的过程应该是:1)通过SPI读取有效载荷,2)清除RX_DR IRQ,3)读取FIFO_STATUS,检查RX FIFO中是否有更多有效负载可用,4)如果RX FIFO中有更多数据,从步骤1)开始。

d.如果激活ACK数据包有效负载,则ACK数据包具有动态有效负载长度,并且应为PTX和PRX上的管道0启用动态有效负载长度功能。这是为了确保他们收到带有有效载荷的ACK数据包。如果在2Mbps模式下ACK有效负载超过15字节,则ARD必须为500μS或更高,并且如果在1Mbps模式下ACK有效负载超过5字节,则ARD必须为500μS或更高。在250kbps模式下(即使有效负载不在ACK中),ARD必须为500μS或更高。

关注微信公众号,获取最新技术文章

下一篇:NRF24L01+中文翻译连载之四——附录与测试记录