转载至:https://www.cnblogs.com/zuilangsanshu/p/9888608.html

FPGA芯片一般有好几组时钟引脚 CLK [0..N] [p,n],我的理解是:首先,时钟必须由外部晶振通过CLK引脚输入到FPGA的时钟网络,至于选用哪一组CLK,主要看FPGA哪个bank对时钟要求最为苛刻;其次,一般用p端,n端由quartus置位三态;再次,对于简单的系统,只有一组CLK输入作为系统主时钟,其他时钟引脚空置,或者作为某些高带载能力的时钟的输出口(是否可作为输出口,要看芯片手册);然后,复杂系统,可以有不同源的时钟分别从不同CLK引脚输入,只是猜想,没实践过,个人认为这样不好,因为FPGA的核心就是同步;另外,不要把CLK引脚和全局时钟、区域时钟什么的混为一谈,一个是时钟输入引脚,一个是内部时钟走线;最后,CLK引脚进去的走线肯定进过优化的(H型铜皮,专用的、直达每个触发器的布线资源),所以能做到小的抖动和偏斜,带载能力。

- 全局时钟:FPGA内部的专用全局时钟布线资源,具有直达每一个触发器的能力,且布线资源经过优化,时钟经过它传输后具有高扇出、最小的偏斜和抖动等。但也因为是全局布线相较于区域时钟,会有较大的插入延时(手册也这么说),而且资源较少(且用且珍惜)。全局时钟网络:1)可由CLK引脚、内部PLL、高速串口(HSSI)、普通逻辑电路产生的时钟(一般不这么干)驱动;2)可驱动所有输出引脚(尤其是CLK引脚,输出作为其他芯片的基础时钟)、内部PLL、区域时钟。

- 区域时钟:只在他们自己所在的区域有效,相当于区域内的全局时钟,在区域内,具有全局时钟的优点,且插入延时比全局时钟小,布线资源也比较多。区域时钟网络:1)可由CLK引脚(注意区域)、内部PLL、高速串口(HSSI)、普通逻辑电路产生的时钟(一般不这么干)驱动;2)可驱动所有输出引脚(尤其是CLK引脚,输出作为其他芯片的基础时钟)、内部PLL。

******注意******

- 常规操作:外部晶振—>时钟引脚—>PLL—>区域时钟、各个模块、输出。

- 关于CLK引脚选择:不是所有的CLK引脚都可以连接到所有的全局/区域时钟网路。

- 关于PLL:不是所有始终都可以驱动PLL,详见手册。

*********************************************************************************************************

Altera 的 Cyclone IV 器件 PLL 具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制。 Altera 的 Quartus II 软件无需任何外部器件,就可以启用 Cyclone IV PLL 和相关功能。本文将介绍如何设计和使用 Cyclone IV PLL 功能。PLL 常用于同步内部器件时钟和外部时钟,使内部工作的时钟频率比外部时钟更高,时钟延迟和时钟偏移最小,减小或调整时钟到输出( TCO)和建立( TSU)时间。

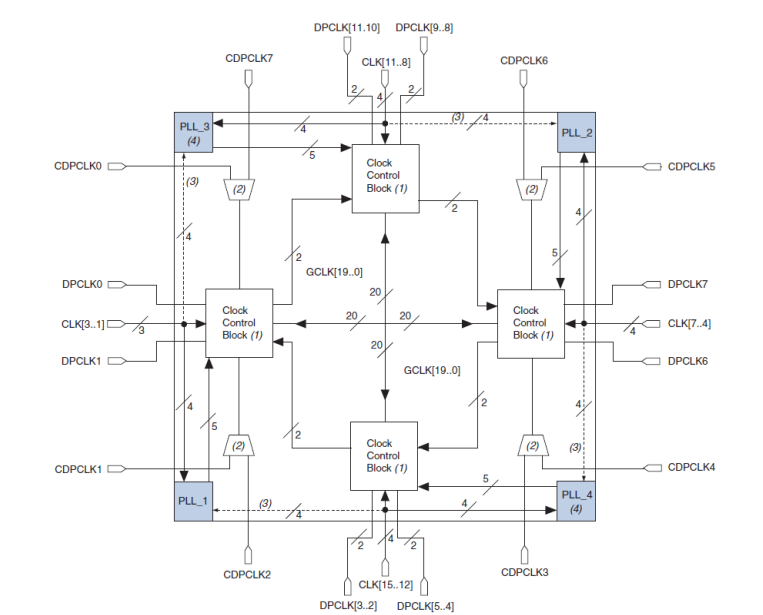

Cyclone IV E 器件提供了多达 15 个专用时钟管脚 (CLK[15..1]),以用于驱动高达 20 个GCLK 时钟网络和 4 个时钟锁相环单元(PLL)。 其中 EP4CE6 和 EP4CE10 为 2 个 PLL。

1. 时钟网络

GCLK 时钟网络驱动整个器件,并对器件各象限提供时钟。 器件中的所有资源(I/O 单元、逻辑阵列模块(LAB)、专用乘法器模块以及 M9K 存储器模块)都能够将 GCLK 用作时钟资源。这些全局网络资源可用于控制信号,例如:由外部管脚驱动的时钟使能及清零信号。另外,内部逻辑也能够驱动 GCLK,以用于内部生成的 GCLK 和异步清零、时钟使能,或者其它具有高扇出的控制信号。时钟控制模块( Clock Control Block) 用于驱动 GCLK 网路, 它们处于芯片的顶端、底部、 左侧及右侧四边, 每边为 5 个, 共 20 个, 位于靠近 FPGA 全局时钟的输入脚。

时钟输入信号通过时钟控制模块后抖动和时延会被优化。 时钟控制模块的输入信号可以分别为专用时钟管脚(CLK1~15), 双功能时(DPCLK 和 CDPCLK), PLL 的输出和 FPGA 内部的逻辑信号。

2. PLLs

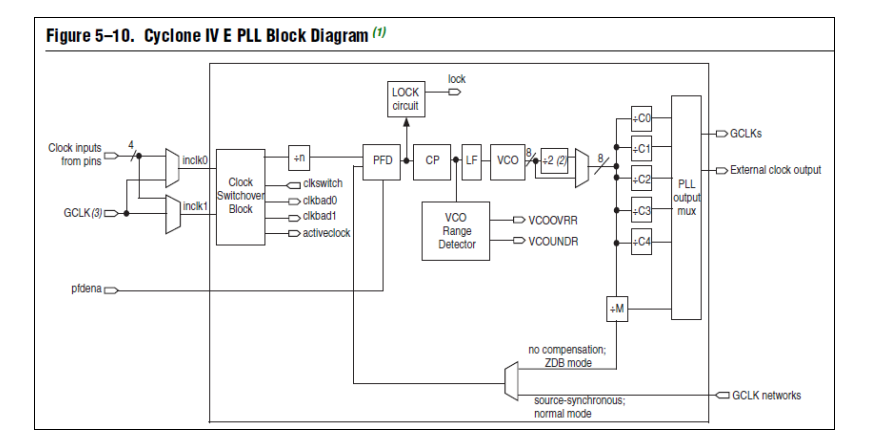

Cyclone IV E 提供了 4 个 PLLs(EP4CE6 和 EP4CE10 只有 2 个 PLLs)为设备提供强大的时钟管理和外部系统时钟管理及高速的 IO 通信, 通过时钟输入, 产生不同频率和不同相位的时钟信号供系统使用。

PLL 的时钟输入可以是 PLL 所在的 Bank 的四个时钟输入管脚, FPGA 内部产生的信号不能驱动 PLL。 Cyclone IV PLLs 产生的时钟可以为单端时钟信号或差分时钟信号, 可以通过GCLKs 网络直接驱动 FPGA 外部的 IO 口。每一个Cyclone IV PLL 均采用 M/(N* 后缩放计数器) 缩放因子为 PLL 输出端口提供时钟合成输出。输入时钟由预缩放因子 N 分频, 然后乘以反馈因子 M。控制环路驱动 VCO以匹配 fIN (M/N)。每一个输出端口均有一个唯一的后缩放计数器,对高频 VCO 进行分频。对于不同频率的多个 PLL 输出, VCO 值是输出频率的最小公倍数,以满足其频率规格。例如,如果一个 PLL 所要求的输出频率是 33 和 66 MHz, 那么 Quartus II 软件会将VCO 设置为 660 MHz(33 和 66 MHz 在 VCO 频率范围内的最小公倍数)。然后,后放大计数器会降低每个输出端口的 VCO 频率。每一个 PLL 上均有一个预缩放计数器 N 和一个乘法计数器 M,范围从 1 到 512。由于计数器 N 仅用于计算分频,因此该计数器不使用占空比控制。此外,每个 PLL 上有五个用于驱动 GCLK 或外部时钟输出的通用后缩放计数器。这些后缩放计数器的范围从 1 到512,并具有 50% 的占空比设置。后缩放计数器的范围从 1 到 256,具有非 50% 的占空比设置。设计所选择的高/ 低计数值的总和,将用于给定计数器分频值的选择。Quartus II 软件根据输入到 ALTPLL 宏功能的输入频率、乘法和除法值来自动选择相应的缩放因子。