碎碎念:

ZYNQ系列的FPGA从问世到如今已历经好几年。作为最先进的SOC系列之一,市场用实际行动证明了Xilinx公司在硬件架构上所具有的前瞻性,ZYNQ在越来越多的场景下发挥了其独具魅力的作用,雷达、人工智能、数据加速等等不计其数。博主不才,几个月前还一直在使用ISE14.7。机缘巧合,手头有个项目正好要用到ZYNQ,实验室也刚好买了706开发板,于是想以此为契机把ZYNQ系列产品好好研究一下。

由于博主一直从事VHDL的开发工作,早把C就抛之脑后。因此这一系列的博文可能会侧重以FPGA工程师的角色去看待ZYNQ。并且大部分博文都是边学习边总结,不免会有很多错误。

架构:

PS+PL架构不再赘述,网上资料排山倒海,下文有“ZYNQ资源简述”对架构的简要罗列。

有人说,ZYNQ并不能说是一个嵌入arm核的FPGA。因为从它的启动过程就可以发现,绝对是arm主导的,所以称它为以高性能FPGA为外设的双核arm或许更为合适。不管这句话对不对,可以肯定的就是ZYNQ不是单独的一个可编程个体了。

PL这一部分是传统的FPGA,他在这个系统里更多扮演的是一个硬件角色;PS是传统的ARM器件,他扮演的是软件实现的角色。PL和PS通过通过一个多层的AXI互连线相互连接。 ZYNQ总的来说就是软硬件协同工作的一个SOC器件。

开发环境:

PL—>Vivado

对于纯FPGA开发者而言,除了以前在ISE上的逻辑编程开发工作外,在对ZYNQ系列开发工作时,我们需要协助软件工程师(PS工程师)在BD(blockdesign)中进行PS的系统设置,然后导出Hardware文件,生成 .hdf 硬件描述文件给SDK搭建硬件系统。

Vivado是基于IP的设计,称为blockdesign(BD),调用已有的IP,用户自己编写的逻辑模块也封装成IP,然后在模块blcok中连线。逻辑开发完毕,再转到SDK,SDK会根据Vivado的硬件设计设置调用相应的内部驱动代码。(PL部分就如同ARM的总线AXI等挂的外设)。

PS(ARM)-->SDK(Xilinx)或者第三方ARM开发工具。

SDK根据VIVADO提供的hardware platform(HW Platform)硬件文件(XML文件)生成硬件所需的软件驱动库BSP(Board support packages)。然后才开始进行ARM软件的开发。可以把PS的这部分软件程序理解为,该程序是应用在HW上,运行在SW(software developer)上的软件程序。

当然,Xilinx还提供了一个SDSoC的集成开发环境。没详细了解。

所以,我们通过vivado软件可以用于搭建硬件系统,确定相应的PS的参数外设等等,要用SDK软件来实现在片上PS上,并且用片上PS运行程序。

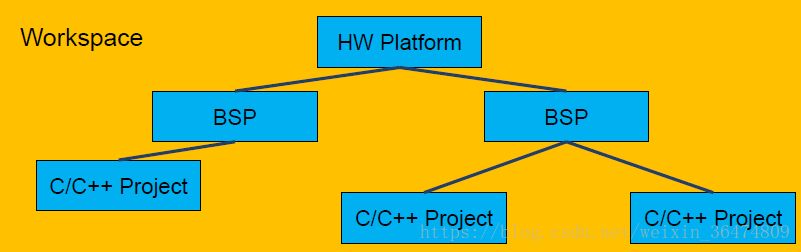

图: vivado和SDK的工作示意图

图:软硬件架构

常见文件:

- .hdf文件

由File -> Export ->Export Hardware 导出 。.hdf 硬件描述文件给SDK,SDK根据上述生成的.hdf文件和XML文件产生所匹配的FSBL文件。

2.FSBL文件

主要是用于bit文件烧录,启动引导程序。用FSBL,将bitstream集成到boot.bin,产生镜像文件进行程序的固化。其他功能还未了解。大概就是这个功能。该文件由XML生成。

3.BSP(board support package)文件

编译用到的库文件,拥有一系列用于具体的系统的驱动。系统会根据hdf配置好对应的板级支持包bsp,这个就是BSP库函数。在src里面添加main.c,写控制代码,保存的时候会自动编译。他和整个工作空间的关系如下图。

- 每个workspace中有一个hardware design,通过XML文件来确定,XML文件在上步中由vivado生成。

- 每个harkware design可以对应多个BSP(Board support packages)文件,BSP文件由XML生成。

- 每个BSP可以对应多个c/c++ projects

图:Workspace

4.XML文件

- 硬件描述语言,可用于生成FSBL与BSP。

- 自动由vivado生成,输出到SDK

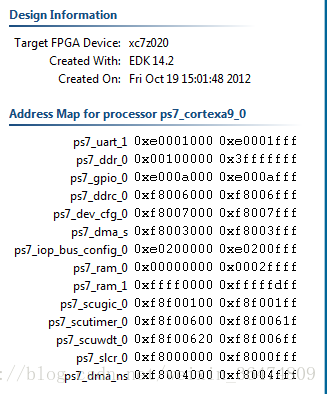

- 包含PS的初始化信息与相应的外设与地址

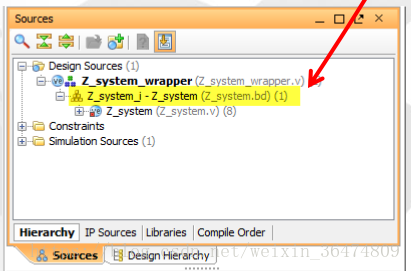

5.BD文件

- vivado创建

- 是IP集成器的block design

- 名字为<project>.bd

- 包含XML,前体文件为MHS文件

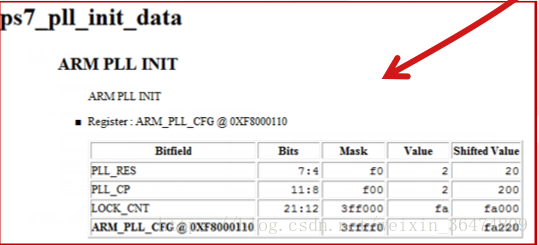

6.PS7_Init

PS7的描述文件,用于configure相应的DDR,PLL,JTAG,外设

会创建相应的C,TCL,HTML文件

资源简述:

ZYNQ从架构上可以划分为两大模块,一个是PS(处理器系统),另一个是PL(可编程逻辑)

PS由APU、内存接口、IO外设、互连线4大模块组成。

1、APU(Application Processor Unit)应用处理单元

即PS【可编程逻辑里面最最核心的东西】,它由两个双核心的Cortex-ARM A9、一些缓存和存储组成。

APU里面有几个比较重要的部分:

一个是ACP,全名Accelerator Coherency Port,加速器一致端口,作用是允许从PL到CPU存储空间的一致性访问,

另外一个是DMA,全名直接存储访问,它支持多种传输模式:内存到内存,内存到外设,外设到内存,有8个通道

下一个是中断控制器,GIC,通用中断控制器

2、内存接口

Memory Interfaces,包括两部分:一个是动态内存控制器(dynamic memory controller),一个是静态内存控制器(static memory controller)

3、IO外设(I/O Peripherals)

USB 2.0 OTG、Ethernet、CAN、SD/SDIO、SPI、UART、I2C、118个GPIO bit

4、互连线

APU、IOP、和内存单元互相连接,并通过一个多层的AXI互连线与PL连接

PS接口

PS外部接口

PS外部接口使用一些不能被赋值为PL引脚的专用引脚,包括:

时钟、复位、启动模式和参考电压

54个专用的多路复用引脚,可以通过软件来配置使其连接到任意的内 部I/O外设或静态内存控制器

32bit或16bit的DDR2/DDR3内存

PS-PL接口

进行数据通信的AXI 接口

2个32-bit的AXI控制接口

2个32-bit的AXI从属接口

4个64/32-bit的AXI从属接口来直接访问DDR内存和OCM,这个端口被称为高性能AXI端口

1个64-bit的AXI从接口(ACP PORT)支持到CPU内存的一致性访问

DMA、中断、事件信号

EMIO允许未映射的访问PL I/O

时钟和复位

4个PS时钟输出到PL进行开始、停止控制

4个PS复位输出到PL

配置和其他

处理器配置访问端口(PCAP)支持完全和部分PL配置,以及安全的PS启动镜像加密和认证

XADC接口

JTAG接口

PL部分包含:

可配置逻辑块

36Kb块RAM

DSP切片

可编程IO块

XADC

PL可配置模块

参考资料:

https://blog.csdn.net/weixin_36474809/article/details/81180514

https://blog.csdn.net/weixin_36474809/article/details/81170725