1. 阻塞赋值

使用一般使用的=进行赋值

always@(clk) begin

b = a;

c = b;

end

- 在前面的a赋值给b的语句没有完成之前,后面的赋值语句不进行操作,就像被阻塞了一样,称为阻塞赋值

- 以上代码会产生的电路结构:

2. 非阻塞赋值

使用一般使用的<=进行赋值

always@(clk) begin

b <= a;

c <= b;

end

- 非阻塞赋值是每条赋值语句的结果在always结尾才能看到,在整个always块结束时才完成一次赋值操作

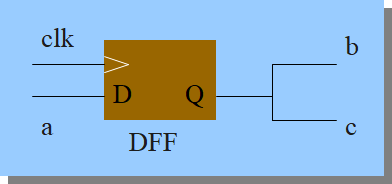

- 以上代码会产生的电路结构:

- 根据非阻塞赋值的特点,c的值要落后b一个时钟周期,因此会多一个D触发器

- 注意: always块中所有非阻塞赋值语句如果需要计算求得所赋的值,则用于计算的每个变量的值是进入always块时各个变量已经具有的值