前言:

5G时代已经到来,但2G、3G、4G解决方案仍有市场,这就带来了一个重大挑战——如何为一些客户提供5G服务的同时,仍满足其他客户的2G、3G和4G需求?

ADRV9009是业界首款支持现有全部蜂窝标准的RF收发器,可在75MHz至6GHz的范围内调谐,支持2G/3G/4G/5G服务,因此蜂窝设备制造商可以采用单一紧凑型无线电设计来满足所有频段和功率要求。

RFIC是无线接入网射频单元最重要的、最核心的芯片之一,本文以此芯片为例,介绍RFIC芯片外在的功能和接口,拆解RFIC芯片内部的工作原理、主要的功能模块与寄存器。

目录

第1章 ADRV9009、对外的主要功能

(1)概述

ADRV9009是业界首款支持现有全部蜂窝标准的多模RF收发器。

该器件可在75 MHz至6 GHz的范围内调谐,支持2G/3G/4G/5G服务,因此蜂窝设备制造商可以采用单一紧凑型无线电设计来满足所有频段和功率要求。

ADRV9009支持窄带应用、超宽带宽,单芯片解决方案可替代众多分立器件,降低设计复杂性,同时缩短产品上市时间。

- 超宽的频率范围:75 MHz至6 GHz

- 最大接收器带宽(单载波):200 MHz

- 最大可调谐发射器合成带宽(多载波):450 MHz

- 最大观察接收器带宽:450 MHz

- 全部蜂窝标准的多模RF收发器:支持2G/3G/4G/5G

- 全集成的时钟合成器

- 内置LO(本振),简化超大规模MIMO的时钟同步

- ADRV9009: 2个独立的射频通道,支持2T2R MIMO

- ADRV9010: 4个独立的射频通道,支持4T4R MIMO

- TDD与FDD的支持

(2)完善的解决方案

不仅仅是一颗芯片,还有配套齐全的开发工具、完备的文档、参考设计、收发器评估板、性能评估、软件驱动、成功案例、合作生态、技术支援社群及其他资源等。

第2章 ADRV9009对外的主要接口

2.1 天线接口

(1)双通道差分射频接收

- RX1_N, RX1_P;

- RX2_N, RX2_P;

- Rx1_Enable:接收通道1使能

- Rx2_Enable:接收通道2使能

(2)双通道差分射频发送

- TX1_OUT+, TX1_OUT-

- TX2_OUT+, TX2_OUT-

- Tx1_Enable:发送通道1使能

- Tx2_Enable:发送通道2使能

(3)天线接口:观测接收机observation receiver

- ORX1_N, RX1_P;

- ORX2_N, RX2_P;

2.2 FPGA数据接口

(1)JESD204B 数据接收:4个Lane标准的SerDes接口

- SERDOUT1+, SERDOUT1-

- SERDOUT2+, SERDOUT2-

- SERDOUT3+, SERDOUT3-

- SERDOUT4+, SERDOUT4-

- SYNCIN1+, SYNCIN1- ;通道1的SerDes接收同步信号

- SYNCIN2+, SYNCIN2- ;通道2的SerDes接收同步信号

(2)JESD204B数据发送:4个Lane标准的SerDes接口

- SERDIN1+, SERDIN1-

- SERDIN2+, SERDIN2-

- SERDIN3+, SERDIN3-

- SERDIN4+, SERDIN4-

- SYNCOUT1+, SYNCOUT1- ;通道1的SerDes发送同步信号

- SYNCOUT2+, SYNCOUT2 - ;通道2的SerDes发送同步信号

备注:

物联网终端射频芯片需要CPU构建物理层的帧结构,并把物理层的帧存放到RFIC内部指定的内存空间中。

RFIC ADI ADRV9009/ADRV9010与之完全不同,它不需要CPU直接给它提供用业务数据。

CPU只需要对RFIC芯片进行OAM配置、管理、维护相关的工作。

业务数据通过JESD204B SerDes接口直接在FPGA和RFIC之间进行传递,因此射频业务数据的接收和发送,都不需要CPU的参与。

2.3 CPU管理接口

(1)CPU接口:SPI管理接口:CS, SDO, SDI

(2)CPU接口:GPIO中断:GP_Interrupt,RFIC向CPU通知中断

2.4 其他控制接口

(1)射频本地晶振时钟LO: RF_EXT_LO_I/O+, RF_EXT_LO_I/O+

(2)芯片工作时钟: REF_CLK_IN+, REF_CLK_IN-

(3)GPIO

(4)复位

(5)电源

(6)Jtag调试

第3章 ADRV9009内部的主要功能模块与工作原理

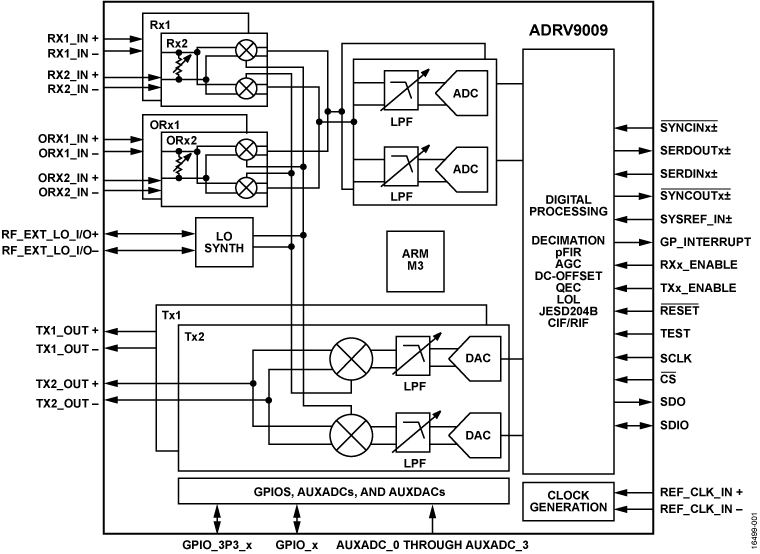

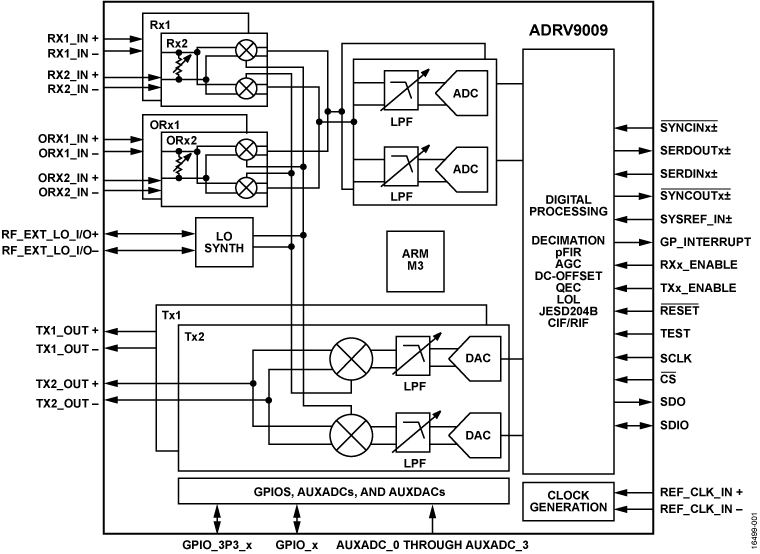

(1)ADRV9009内部功能框图

- 射频功能:射频信号放大、自动自增控制等、射频滤波、

- 混频功能:频谱搬移

- 数模转换与模数转换。

- 数字功能

(2)AD9361内部功能框图

虽然AD9361与ADRV9009与FPGA的接口不同,AD9361是12bit的并行接口,ADRV9009串行接口。虽然还有其他的接口也不相同,如AD9361不支持5G的带宽,最大带宽支持56M。

但AD9361与ADRV9009内部功能基本相似, 因此借助AD9361的更详细的内部功能框图来阐述ADRV9009的内部功能。

AD9361是ADI推出的面向3G和4G基站应用的高性能、高集成度的射频解决方案。该器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字接口。AD9361接收器LO工作频率范围为70 MHz至6.0 GHz,发射器LO工作频率范围为47 MHz至6.0 GHz,涵盖大部分特许执照和免执照频段,支持的通道带宽范围为200 kHz(GSM, NB-IoT)以下至56 MHz。

3.1 信号接收

(1)LO_SYNTH

本地晶振同步电路,用于根据本地晶振,生产内部的各路射频时钟 。

(2)![]() 混频器、射频调制、频谱搬移器

混频器、射频调制、频谱搬移器

变频,是将信号频率由一个量值变换为另一个量值的过程。具有这种功能的电路称为变频器(或混频器)。

混频器将天线上接收到的射频信号与本振产生的信号相乘,cosαcosβ=[cos(α+β)+cos(α-β)]/2。

混频器+低通滤波器LPF的组合,起到了射频解调的功能:相同于把调制在高频载波信号上的“中频信号”卸载下来。

混频器+低通滤波器LPF的组合,起到了频率搬移的功能:即把调制在高频信号上的“基带信号”,从高频载波上搬移到中频载波上。

(3)LPF: 低通滤波器

低通滤波器是容许低于截止频率的信号通过, 但高于截止频率的信号不能通过的电子滤波装置。

低通滤波器与混频器,一并完成模拟高频解调。

(4)模数转换ADC

对模拟信号进行采样,并转换成数字信号的过程。

(5)自动增益控制AGC(automatic gain control)

自动增益控制AGC是使放大电路的增益,自动地随信号强度而调整的自动控制方法。

自动增益控制是限幅输出的一种,它利用线性放大和压缩放大的有效组合对助昕器的输出信号进行调整。

当弱信号输入时,线性放大电路工作,保证输出信号的强度;

当输入信号达到一定强度时,启动压缩放大电路,使输出幅度降低。

也就是说,AGC功能可以通过改变输入输出压缩比例自动控制增益的幅度。AGC细分为AGCi(输入自动增益控制)和AGCo(输出自动增益控制)

实现这种功能的电路简称AGC环。

AGC环是闭环电子电路,是一个负反馈系统,它可以分成增益受控放大电路和控制电压形成电路两部分。

增益受控放大电路位于正向放大通路,其增益随控制电压而改变。控制电压形成电路的基本部件是AGC 检波器和低通平滑滤波器,有时也包含门电路和直流放大器等部件。放大电路的输出信号u0 经检波并经滤波器滤除低频调制分量和噪声后,产生用以控制增益受控放大器的电压uc 。当输入信号ui增大时,u0和uc亦随之增大。 uc 增大使放大电路的增益下降,从而使输出信号的变化量显著小于输入信号的变化量,达到自动增益控制的目的。

3.2 信号发送

(1)数模转换DAC

数模转换器,又称D/A转换器,简称DAC,它是把数字量转变成模拟的器件。

(2)![]() 混频器、射频调制、频谱搬移器

混频器、射频调制、频谱搬移器

把调制在中频中的基带信号,搬移到高频中相应的位置,或者说,把转换模拟信号后的中频信号调制到高频信号上。

(3)LPF: 低通滤波器

通过低通滤波器,滤除在混频过程中产生的更高频率的高频信号,得到一个干净的模拟射频信号!!!

3.3 模拟高频、数字中频、数字低频

这里涉及三个频率,为什么需要中频信号呢?为什么不直接把低频的基带信号调制到高频信号上呢?

这里涉及到在一个高频载波上,承载多个不同小区Cell中频载波信号的问题。

(1)数字低频:数字基带信号

二进制数据实际上是调制在数字基带信号上,也就是低频信号上。

(2)数字中频:

数字中频所谓中频,顾名思义,是指一种中间频率的信号形式。中频是相对于基带信号和射频信号来讲的,中频可以有一级或多级,它是基带和射频之间过渡的桥梁。

软件无线电的设计思想之一是将A/D 转换器尽可能靠近天线,即把A/D从基带移到中频甚至射频,把接收到的模拟信号尽早数字化。

由于数字信号处理器(DSP)的处理速度有限,往往难以对 A/D采样得到的高速率数字信号直接进行各种类别的实时处理。

为了解决这一矛盾,需要采用数字下变频(DDC)技术,将采样得到的高速率信号变成低速率基带信号,以便进行下一步的信号处理。

中频部分用数字方式来实现就称之为数字中频。数字中频技术通常包括上下变频(DUC/DDC)、波峰因子衰减(CFR)和数字预失真(DPD)。

数字中频在5G通信系统中,是由FPGA完成,这里不多阐述。

(3)模拟高频:

模拟高频调制,实际上是一种幅度调制的过程,也是频谱搬移的过程。

(4)最终效果

3.4 有限脉冲响应(FIR)滤波器

滤波器就是允许我们想要的频率分量通过,同时删减我们不想要的频率分量。

有限脉冲响应(FIR)是一种数字滤波器,用于数字信号处理时的滤波。

3.5 发送和接收本振LO的频率产生原理

第4章 ADRV9009常规配置

(1)发射通道设置

- Tx发送使能

- 发射通道频率设置:设置后会触发锁相环与LO本地进行进行重新同步

- 接收带宽设置

- 发射通道衰减

- Tx Clock & Data Delay

(2)接收通道设置

- Rx接收使能

- 中心频点,设置后会触发锁相环与LO本地进行进行重新同步

- 发送带宽设置

- Rx Clock & Data Delay

- 接收通道增益调整

(3)测试模式

- 内部产生发射或者接收信号

- 将内部输出信号直接作为输入

(4)基带锁相环控制

- 包括输出CLK_OUT输出信号选择

参考:

《官网参考手册》:https://www.analog.com/cn/products/adrv9009.html?ADICID=PRLS_CN_P42156