1、概述

在数字电路中时钟是整个电路的心脏,电路的的一举一动都是根据时钟节拍下进行的,随着信息量逐渐提高,对硬件信息处理能力提出了更大的需求,时钟作为数字硬件的关键成员,其性能需要我们关注,尤其在高速电路设计中对模拟转换芯片对时钟性能有很高的需求,因此正确选择时钟是很关键的一步,前提是我们要了解时钟的关键参数咯。在数字电路中最常见的时钟元件有晶振和锁相环、时钟缓冲器等,简单了解下~

2、晶振&晶体

2.1、原理

晶体具有压电效应,即在晶体两极增加电压,能使晶体发生机械变形,在晶体两极增加压力又能使晶体两极产生电场,因此如果在晶体两极加上交变电压就能使得晶振发生谐振,在共振的条件下产生稳定的单频信号。

2.2、分类

2.2.1 晶体:高速电路中常用到的的是石英晶体,其本身具有的压电效应使得其可以起振,根据不同的切割方式可以得到不同的固有频率,我们常用的无源晶振就是指晶体,其内部不具有电路只有晶片,因此需要外部振荡电路辅助起振,实际应用中常常需要对晶体两个引脚到地之间串联电容。

2.2.2 晶振: 晶振不同于晶体在于,晶振内部具备完整的振荡条件,不需要依赖外部提供振荡电路,使用时只需要对其进行供电,缺点在于其输出电平逻辑确定,不能通用到任意器件,需要注意逻辑匹配哦。常用的晶振又分为普通晶振、压控晶振、恒温晶振、温补晶振、电压控制温补晶振、电压控制恒温晶振等。

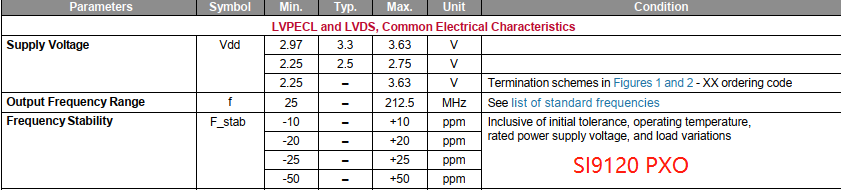

① 普通晶振PXO:未采取温度补偿等操作,价低,频率稳定度10^-5量级,应用在一般时钟稳定度要求不高的场合。

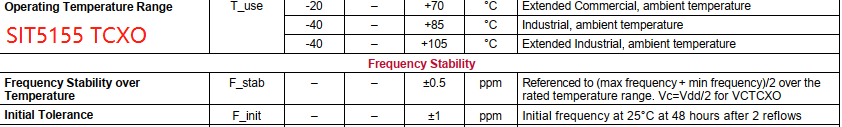

② 温补晶振TCXO:采用温度补偿技术,通过温度补偿受温度影响造成的频率漂移,精度可以达到10^-7。

③ 恒温晶振OCXO:采用恒温技术,将晶振置于恒定温度环境中,减少外部环境温度干扰,精度可达10^-9适合应用在时钟精度要求较高场合。

④ 压控晶振VCXO:通过电压改变晶振输出频率。

⑤ 电压控制温补晶振VC-TCXO: 压控晶振和温补晶振结合。

⑥ 电压控制恒温晶振VC-OCXO: 压控晶振和恒温晶振结合。

2.3、关键参数

常用的晶振参数:

SPXO\TCXO\OCXO:

① 中心频率:即输出标称频率;

② 频率稳定度:即频率误差,常用单位ppm表示,即百万分之一;

③ 输出电平逻辑及波形:LVTTL/LVCMOS/LVDS/LVPECL; 正弦波 /方波

④ 工作电压及启动功耗:1.8V/2.5V/3.3V/5.0V/12V,注意提供足够启动功耗,如大普晶振O55A系列,启动功耗高达8W。

⑤ 老化度:年老化、日老化;

⑥ 工作温度范围:民用级,工业级;

⑦ 启动时间:注意工作稳定后再启动电路工作

⑧ 时钟抖动:时钟抖动是时域的概念,指时钟每个周期之间的差距,边沿出现提前跳变或延迟跳变的情况,使用示波器余辉效应可以测得大致抖动,单位 fs。

⑨ 相位噪声:相位噪声是频域的概念,对应时域上的时钟抖动,使用好点的频谱仪可以测得,单位dBc/Hz@频率偏移。

VCXO特有

控制电压:改变控制电压,调整输出频率。

频率牵引范围:调整电压向最大或最小变化时可调整的频率输出范围。

绝对牵引范围:频率牵引范围减去温度、电压、老化率等影响。

3、锁相环

普通晶振虽然比较稳定,相位噪声等参数较好,但通常振荡频率不高,并且无法改变频率,不能满足需求,虽然有VCXO出现了,但是VCXO稳定度不高,且容易受到外部环境影响,这时候一种基于VCXO的闭环电路出现了,可以实现频率配置和输出高性能时钟,这就是锁相环。

3.1、原理

其基本原理框图如下。

OSC:外部振荡源;

R Divider:R预分频;

FPD:相位检测器,前提是同频才能鉴相,检测两个输入信号相位差驱动电流信号;

LPF:低通滤波器,滤去纹波和噪声等高频信号,并对鉴相器输出信号进行积分;

VCO:压控振荡器;

N Divider:N分频;

OSC提供外部基本振荡,这个频率通常比较低,首先经过R预分频得到鉴相频率(当然我们希望这个频率越大越好,以便得到较好的相位噪声),通过鉴相器对Fpd和VCO的N分频Fn进行相位比较得到相位差去驱动电荷泵输出一个电流信号,通过低通滤波器积分后,得到直流电压从而控制VCXO输出频率。输出电流CP总是向减小FPD相位差方向变化,这称为捕捉过程,直到Fpd和Fn 频率和相位相同后进入锁定状态。

设计关键:

鉴相频率确定:通常锁相环芯片内部集成的VCO都只有有限的频率输出范围,根据需要的输出频率,确定VCO输出频率,综合OSC频率和R/N分频得到合适的鉴相频率(Fvco=Fosc*N/R),我们希望鉴相频率尽可能大,以便得到较好的相位噪声,因为PLL相位噪声基本是由FOM+10log(Fpd)+20log(Fout/Fpd)-20log(DIV)决定。

LPF带宽确定:LPF带宽越小有利于减小带内噪声,但LPF也不能太窄,防止对VCO噪声抑制不够。

3.2、分类

小数分频:小数分频与整数分频的基本原理相同,其差别在于小数分频PLL的分频比N不仅仅具有整数部分,还具有小数部分,这样输出频率可以按照参考频率分数倍变化,有利于快速锁定和抑制相位噪声,

整数分频:即N为整数

3.2、关键参数

通常在锁相环锁定频率之后我们再通过通道分频器对这个锁定频率分频到目标频点,我们所需要关注的参数也就是整个输入经过锁相环通道分频之后到输出的各部分参数啦,以单锁相环为例子(有的锁相环芯片支持PLL级联以便得到更好的相位噪声),简要介绍其参数。

如上图,各模块涉及到的参数主要有以下:

① 参考输入频率范围

② 鉴相频率范围

③ R/N系数范围

④ 输出频率范围

⑤ VCO范围

⑥ 通道分频系数

⑦ 输出电平逻辑:LVTTL/LVCMOS/LVDS/LVPECL; 正弦波 /方波

⑧ 时钟抖动:时钟抖动是时域的概念,指时钟每个周期之间的差距,边沿出现提前跳变或延迟跳变的情况,使用示波器余辉效应可以测得大致抖动,单位 fs。

⑨ 相位噪声:相位噪声是频域的概念,对应时域上的时钟抖动,使用好点的频谱仪可以测得,单位dBc/Hz@频率偏移。

⑩ 通道偏斜SKEW :多输出通道之间的相位偏差。

工作电压功耗等