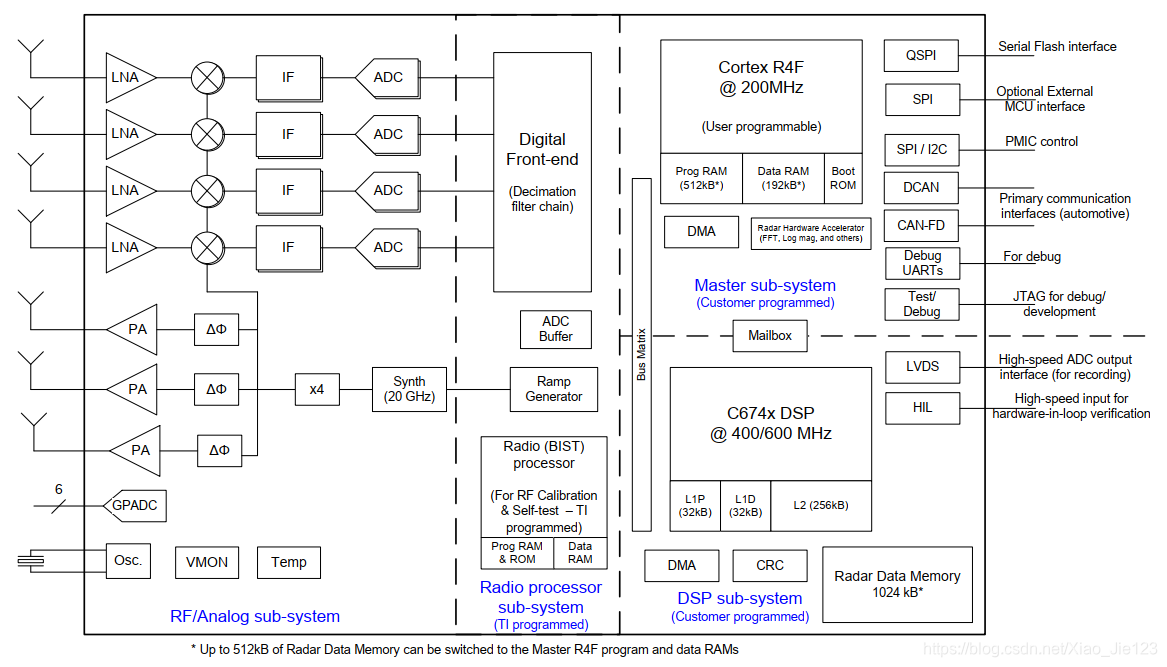

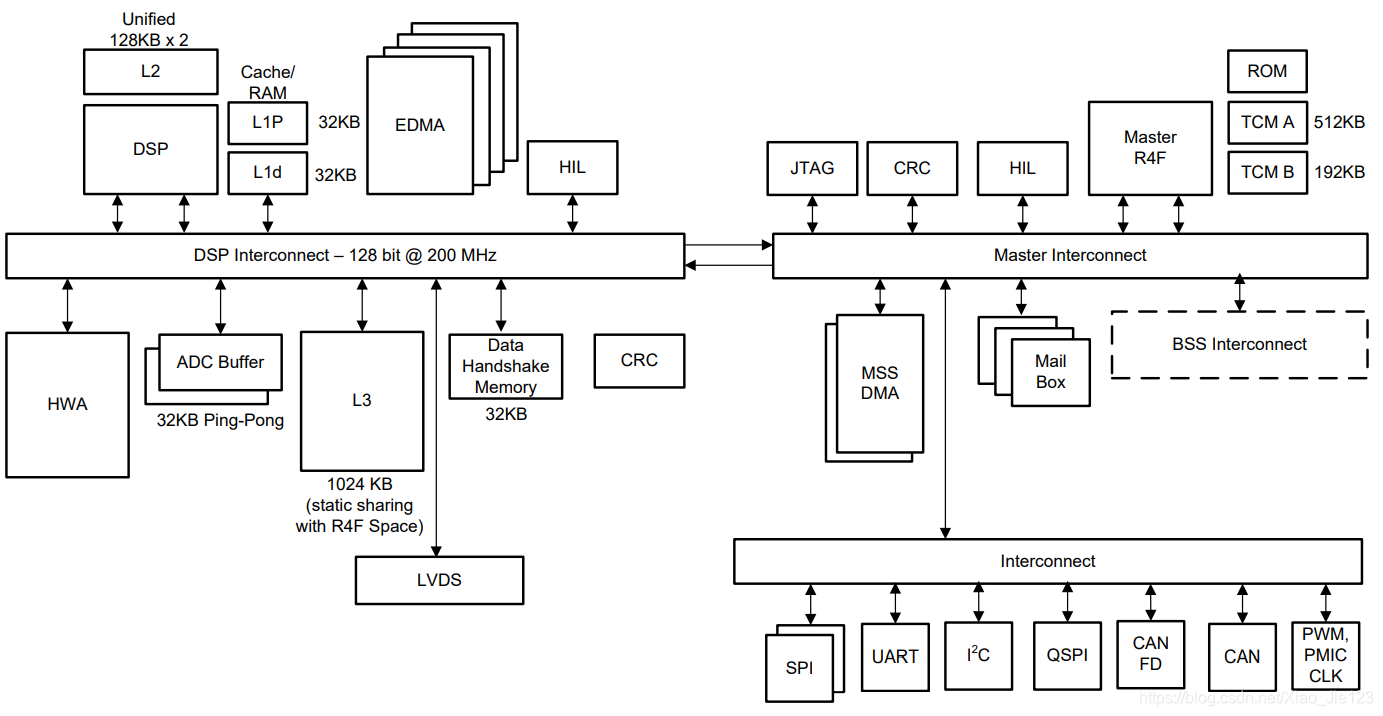

AWR1843集成了BIST处理器子系统:该子系统负责无线电配置、控制和校准,DSP子系统:包含TI用于雷达信号处理的高性能C674x DSP,还集成了用户可编程的ARM R4F,还包括硬件加速器(HWA)可执行雷达处理,并且有助于以更高级的算法在DSP上保存MIPS。

文章目录

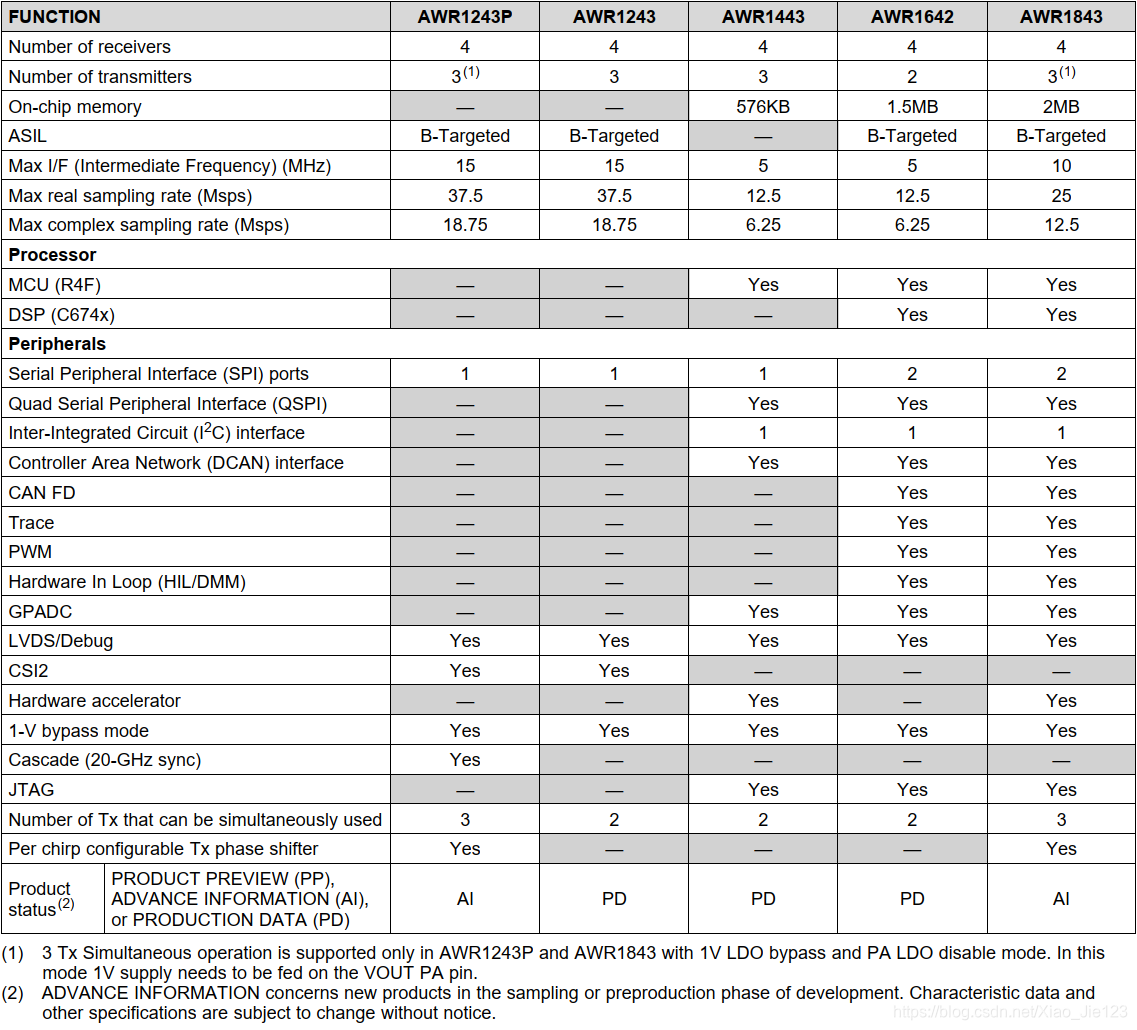

不同雷达设备的比较

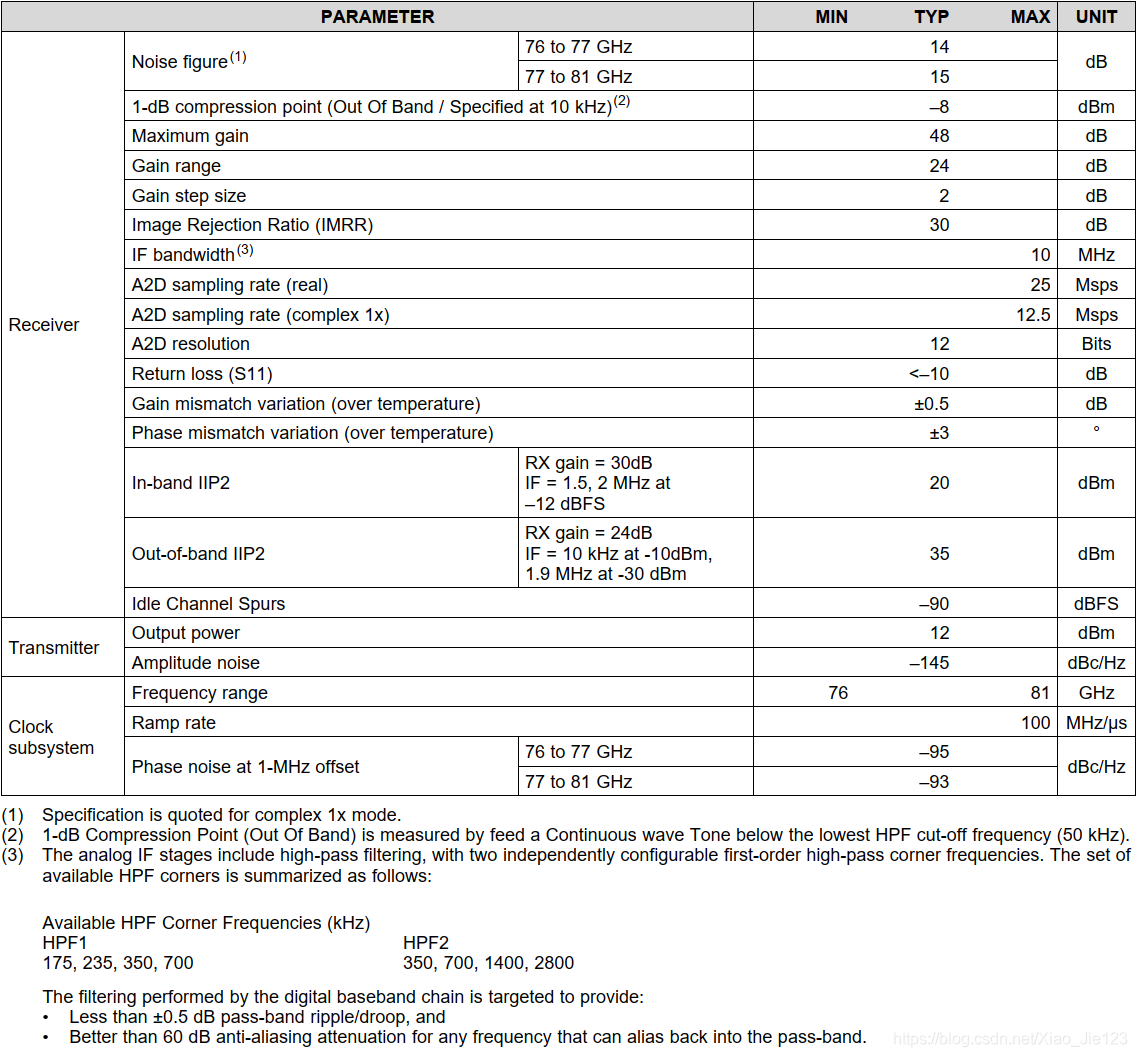

RF Specification

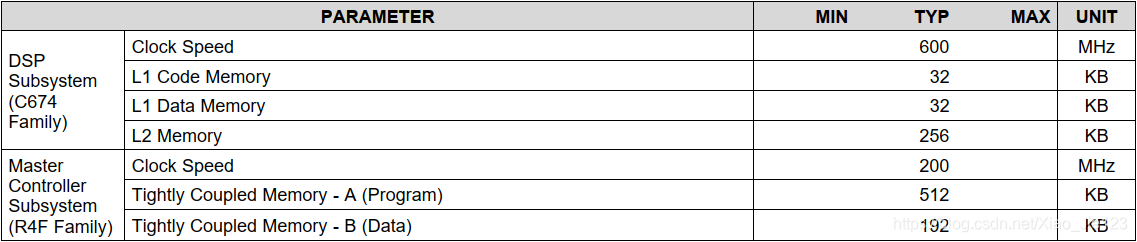

CPU Specifications

Functional Block Diagram

RF and Analog Subsystem

射频和模拟子系统包括射频和模拟电路,即合成器、PA、LNA、混频器、IF和ADC。该子系统还包括晶体振荡器和温度传感器。根据需要,三个发射通道一次最多可操作两个(同时)发射波束形成,而四个接收通道可同时操作。(只有在AWR1243P和AWR1843中,1V LDO旁路和PA LDO禁用模式下,才支持3 Tx同时操作。在这种模式下,需要在VOUT PA引脚上提供1V电源)

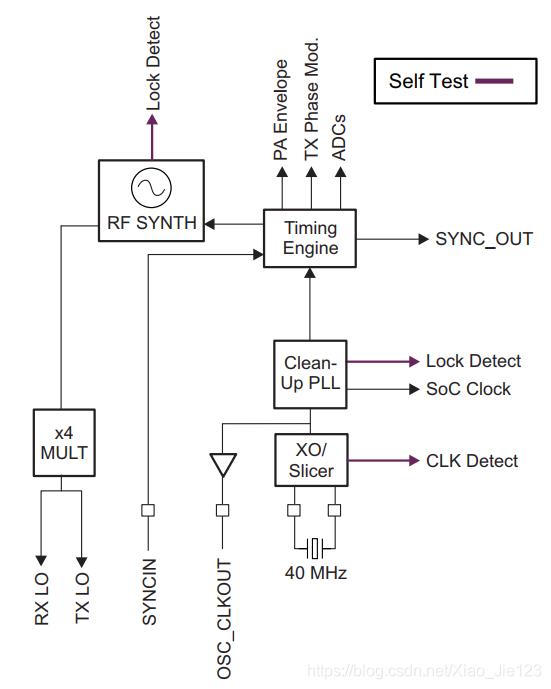

Clock Subsystem

AWR1843时钟子系统利用40MHz晶振产生76到81GHz的频率。内置振荡电路,然后是一个clean-up PLL和RF合成器电路,RF合成器的输出然后由X4倍频器处理,以在76到81GHz的频谱中产生所需要的频率。射频合成器的输出由定时引擎块调制,以产生有效传感器操作所需的波形。

clean-up PLL在主机处理器在系统唤醒后提供了一个参考时钟

时钟子系统还具有内置机制,用于检测晶体的存在并监控生成时钟的质量

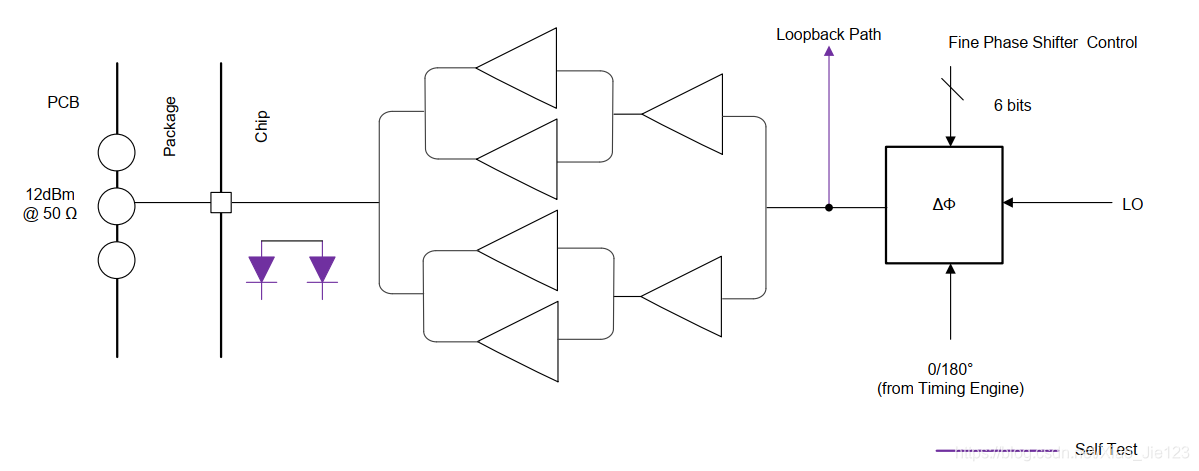

Transmit Subsystem

AWR1843传输子系统由三个并行传输链组成,每个链具有独立的相位和幅度控制。所有三个发射机可以同时使用。对于AWR1843,附加的移相器与Tx通道相关联,并且这些移相器可以按每个chirp为基础进行编程。

每个传输链可以在PCB上的天线端口传输最大12dBm。

下图为每个通道的发射子系统

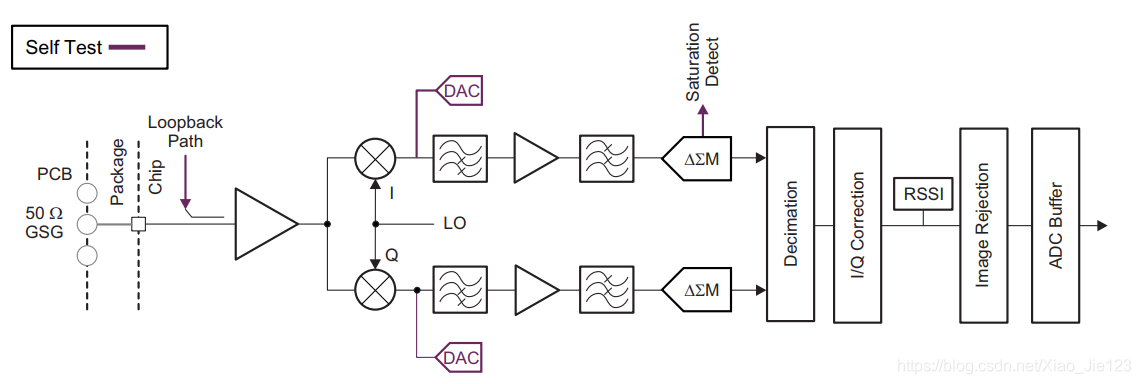

Receiver Subsystem

AWR1843接收子系统由四个并行的通道组成。单个接收通道包括低噪声放大器、混频器、中频滤波、A2D变换和抽取。所有四个接收通道都可以同时工作,一个单独的供电选项对系统优化是可用的。

与传统的纯实数接收机不同,AWR1843设备支持复杂的基带结构,它使用正交混频器和双IF和ADC链为每个接收通道提供复杂的I和Q的输出。AWR1843是针对快速的chirp系统。带通中频链具有可配置低于175kHz的截止频率,可支持高达10MHz的带宽。

下图为每个通道的接收子系统

Processor Subsystem

HIL模块在两个子系统中都有,用于执行雷达操作,将从捕获的数据从外部输入到设备,而不涉及子系统。在MSS上的HIL用于控制配置并且DSS上的HIL用于高速ADC数据输入到设备。

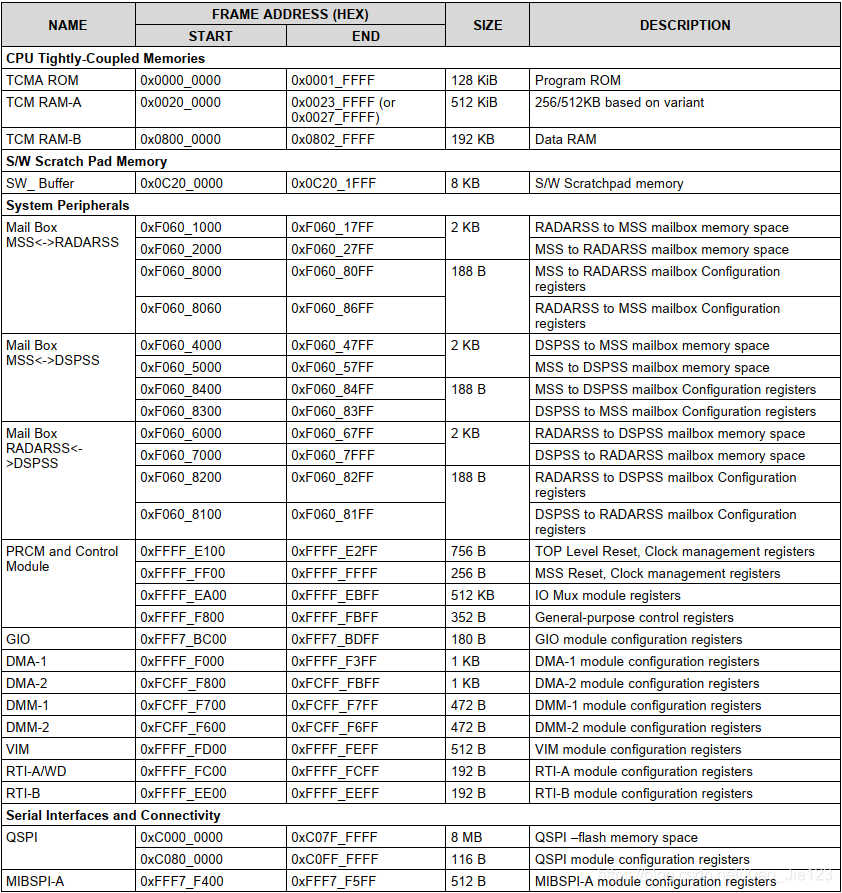

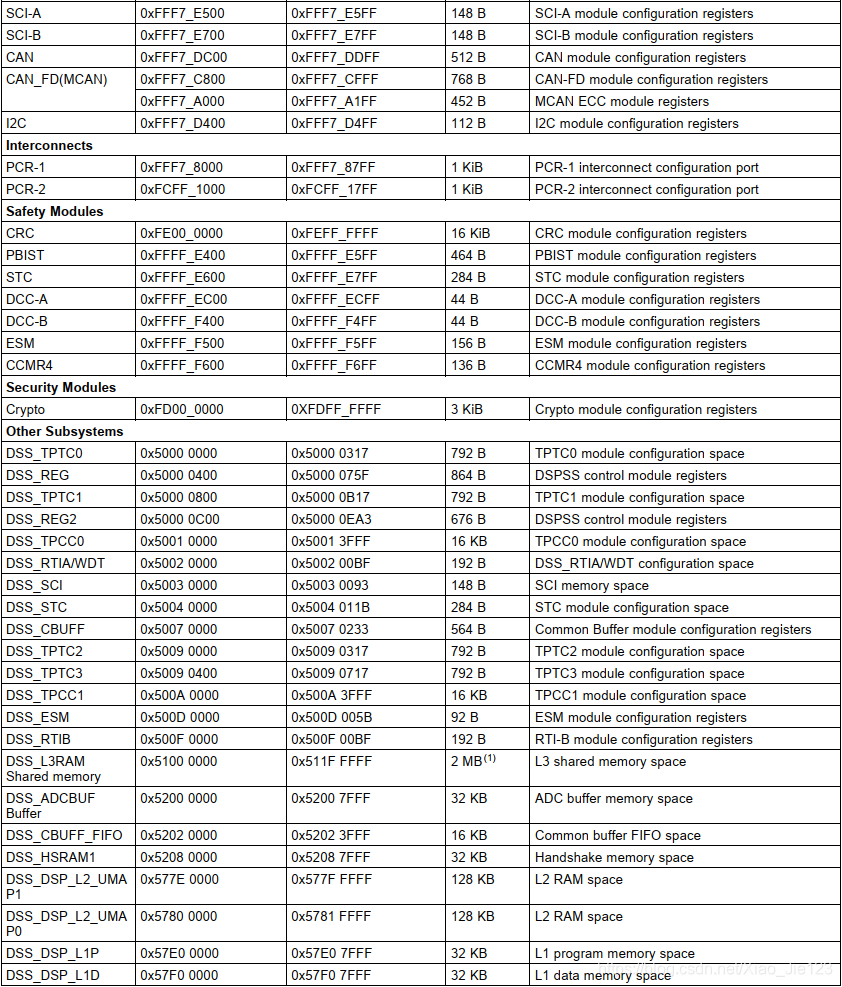

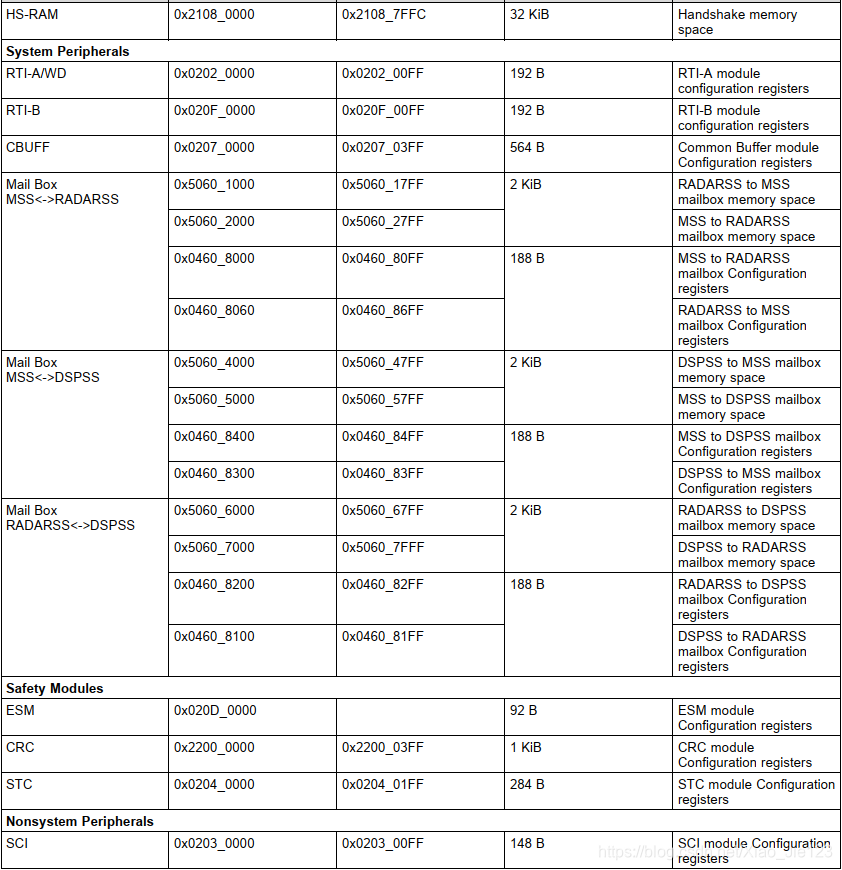

Master Subsystem Cortex-R4F Memory Map

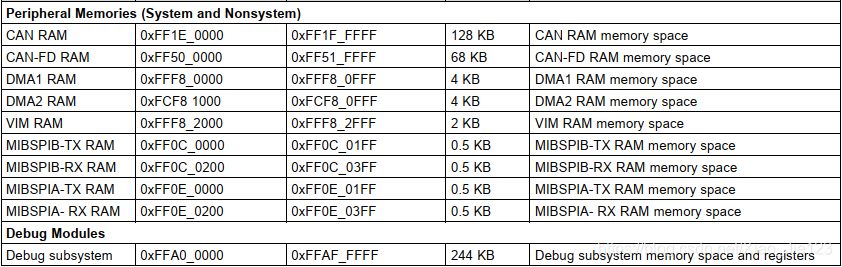

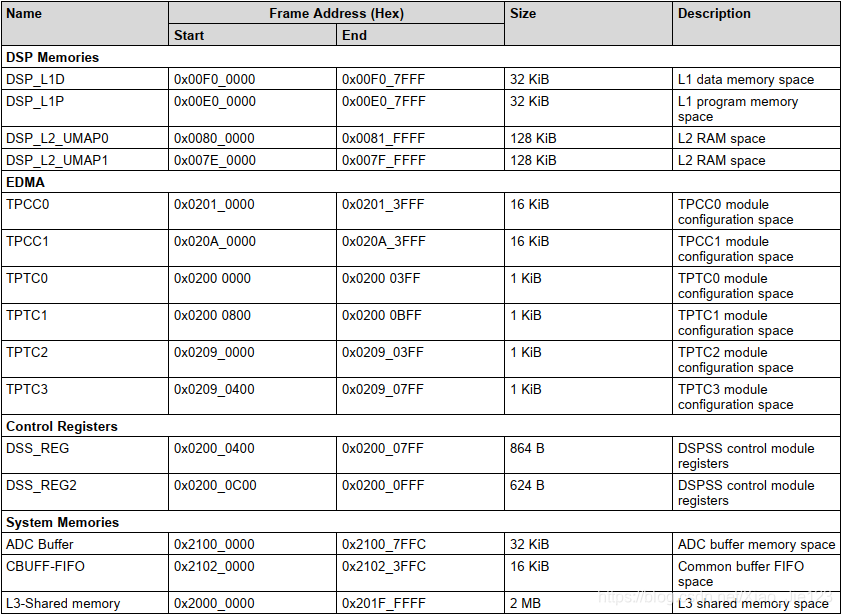

DSP Subsystem Memory Map

ADC Channels (Service) for User Application

AWR1843设备包括用于用户应用的ADC服务,其中设备内部的GPADC引擎可用于测量多达六个外部电压。ADC1、ADC2、ADC3、ADC4、ADC5和ADC6引脚用于这个目的。

ADC本身由运行在BIST子系统内的TI固件控制,通过路由到BIST子系统的"监控API"访问ADC,以便用户进行外部电压监测。这个API可以与Master R4F上运行的用户应用程序相连接。

BIST子系统固件将在内部安排这些测量以及其他射频和模拟监测操作。API允许配置设置时间(要跳过的ADC采样数)和要采集的连续采样数。在帧结束时,将报告每个监测电压的最小、最大和平均读数。

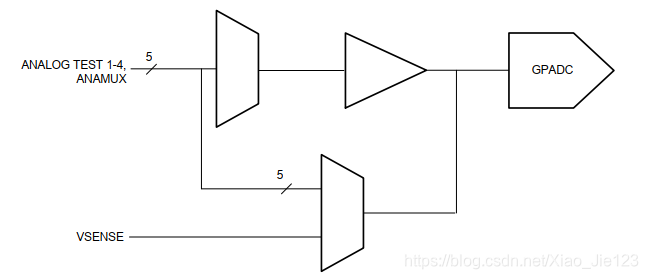

ADC Path

参考文档:

- 《AWR1843 单芯片 77GHz 和 79GHz FMCW 雷达传感器》