1.IIC总线介绍

第一:I2C(IIC,Inter-Integrated Circuit),两线式串行总线,由PHILIPS公司开发用于连接微控制器及其外围设备。

第二:IIC是半双工通信方式,只有2根链接线,一根是双向的数据线SDA,可发送和接收数据,I2C总线上的主设备与从设备之间以字节(8位)为单位进行双向的数据传输。半双工:意思一根线有收发功能叫双工,但是一根线只能在一个时刻收或者发,则就时办双工。

另一根是时钟线SCL,两条线可以挂多个设备,每个设备都可以作为主机也可以作为从机,但是在同一时刻只能有一个主机,通常我们为了方便把IIC设备分为主设备和从设备,基本上谁控制时钟线(即控制SCL的电平高低变换)谁就是主设备。

第三:IIC设备(绝大多数)里有个固有的地址,只有在两条线上传输的值等于IIC设备的固化地址时,其才会作出响应。在CPU与被控IC之间、IC与IC之间进行双向传送。

第四:I2C总线数据传输速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。一般通过I2C总线接口可编程时钟来实现传输速率的调整,同时也跟所接的上拉电阻的阻值有关。

2.IIC总线物理拓扑结构

第一:在总线空闲状态时,这两根线一般被上面所接的上拉电阻拉高,保持着高电平。

第二:由于IIC系统中每个设备都有固有的地址,地址又分为8位地址,使用8位地址模式,减去1位广播地址,是127位地址,2^7=128,但是地址0x00不用,那就是127个地址,所以理论上可以挂127个从器件 。使用7位地址模式时,要去掉16个保留地址,因此最多可带112个设备。

第三:但是规定了总线电容不能超过400pF。管脚都是有输入电容的,PCB上也会有寄生电容,所以会有一个限制。实际设计中经验值大概是不超过8个器件。总线之所以规定电容大小是因为,IIC的OD要求外部有电阻上拉,电阻和总线电容产生了一个RC延时效应,电容越大信号的边沿就越缓,有可能带来信号质量风险

3.IIC总线协议时序

3.1空闲状态

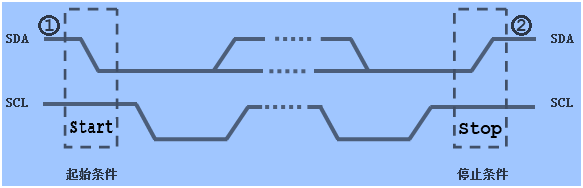

I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态,由两条信号线各自的上拉电阻把电平拉高。此时各个器件的输出级场效应管均处在截止状态,即释放总线。如图1号位置和2号位置.

3.2开始信号和停止信号

开始信号:总线的空闲状态下SCL为高电平而SDA由高到低的跳变,表示产生一个起始条件;如1号位置的跳变。

停止信号:当SCL为高而SDA由低到高的跳变,表示产生一个停止条件,如图2号位置的跳变。

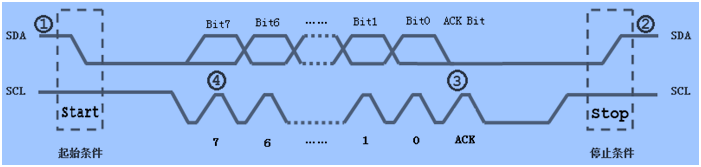

3.3应答信号

发送设备每发送一个字节,就在时钟的第9脉冲期间释放数据线,由接收设备反馈一个应答信号。 应答信号为低电平时,规定为有效应答位ACK,表示接收设备已经成功地接收了该字节;应答信号为高电平时,一般表示接收设备接收该字节没有成功NACK。如图3号位置。

对于反馈有效应答位ACK的要求是,接收设备在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。 如果接收设备是主控器,则在它收到最后一个字节后,发送一个应答信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收设备发送一个停止信号P。这里也就时说谁要发送数据谁就得获得SCL的控制权。

3.4数据的有效性

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,如4号位置。

只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化,如5号位置。

就是说数据在SCL的上升沿到来之前就需准备好。并在在下降沿到来之前必须稳定。

3.5数据传输

在前面提到过,I2C总线上设备(绝大多数)里有个固有的地址,主从设备之间的数据传输是建立在地址的匹配基础上,也就是说,主设备和从设备通信需要进行地址验证,大多数从设备的地址是7位的,然后协议规定再给地址添加一个最低位用来表示接下来数据传输的方向,0表示主设备向从设备写数据,1表示主设备向从设备读数据。传输数据的每一最小包由9bit组成,8bit内容+1bit ACK, 如果是地址数据,则8bit内容中包含1bit读写位7bit的地址数据。如下图6号位置,表示主机寻找从机。