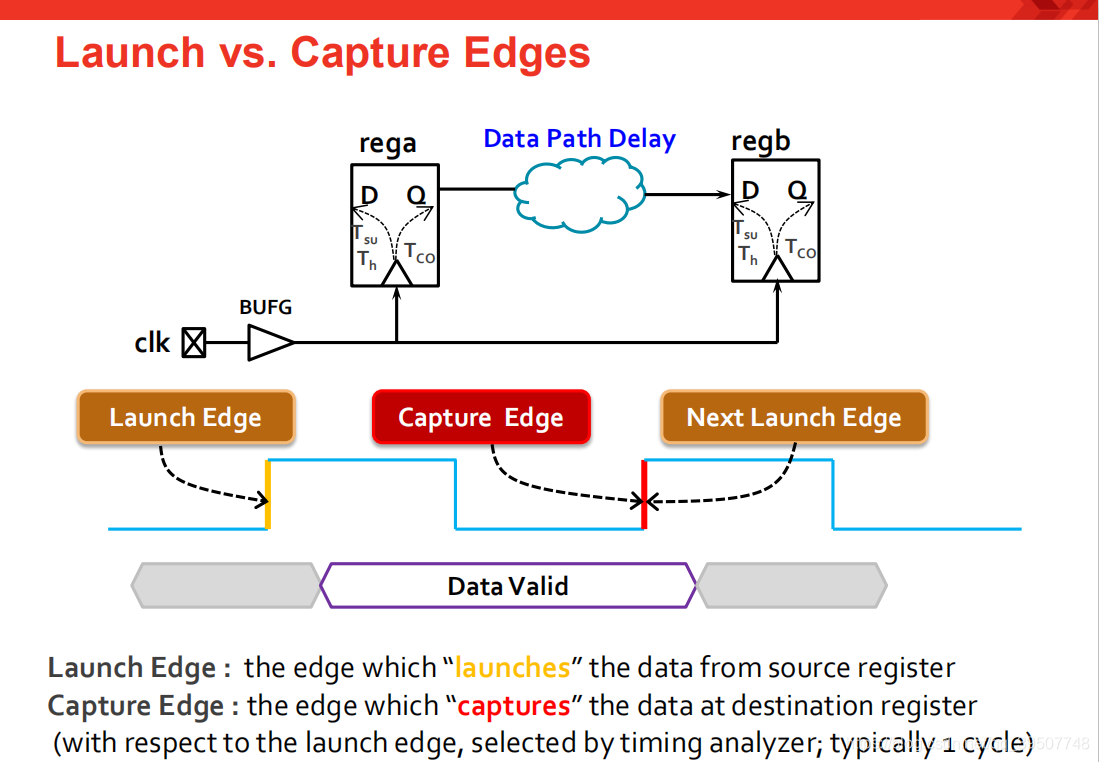

1、数据发起时间沿和捕获时间沿

数据的发起沿和数据的捕获沿相差一个CLK。

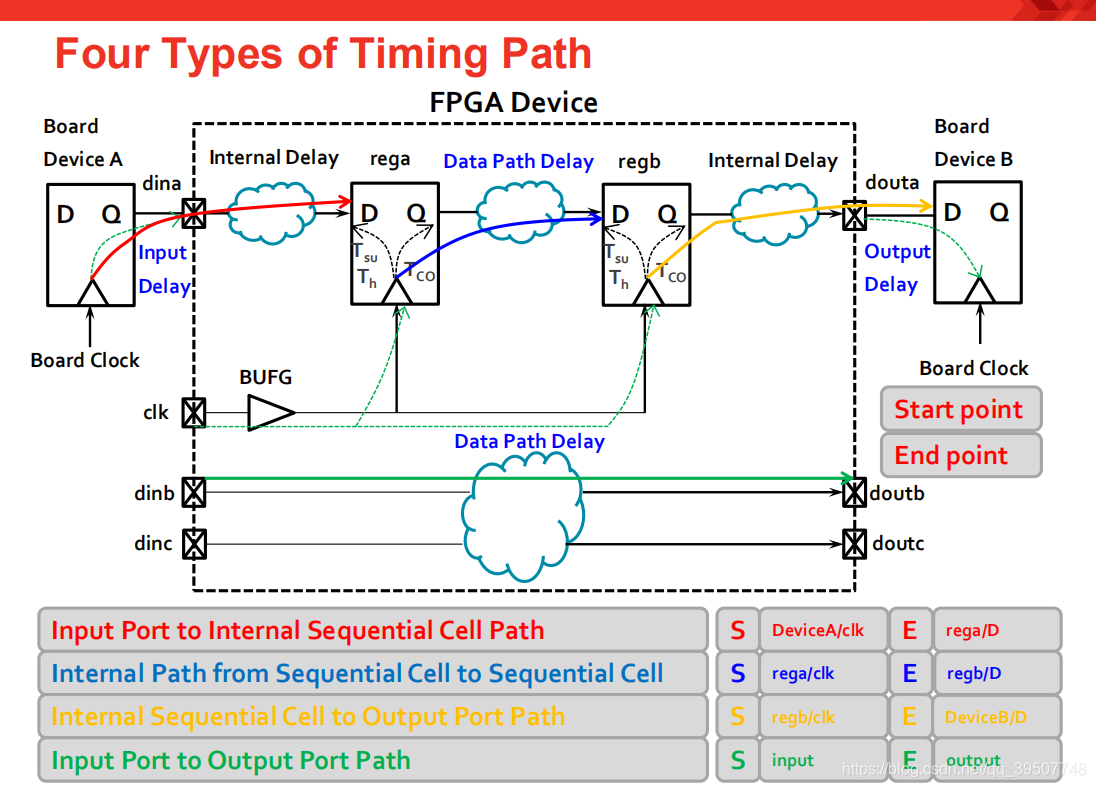

2、4种类型的时序路径

(1)输入端口到FPGA内部的第一级触发器;

(2)FPGA内部寄存器之间的路径;

(3)FPGA内部末级触发器到输出端口的路径;

(4)输入端口到输出端口的路径;

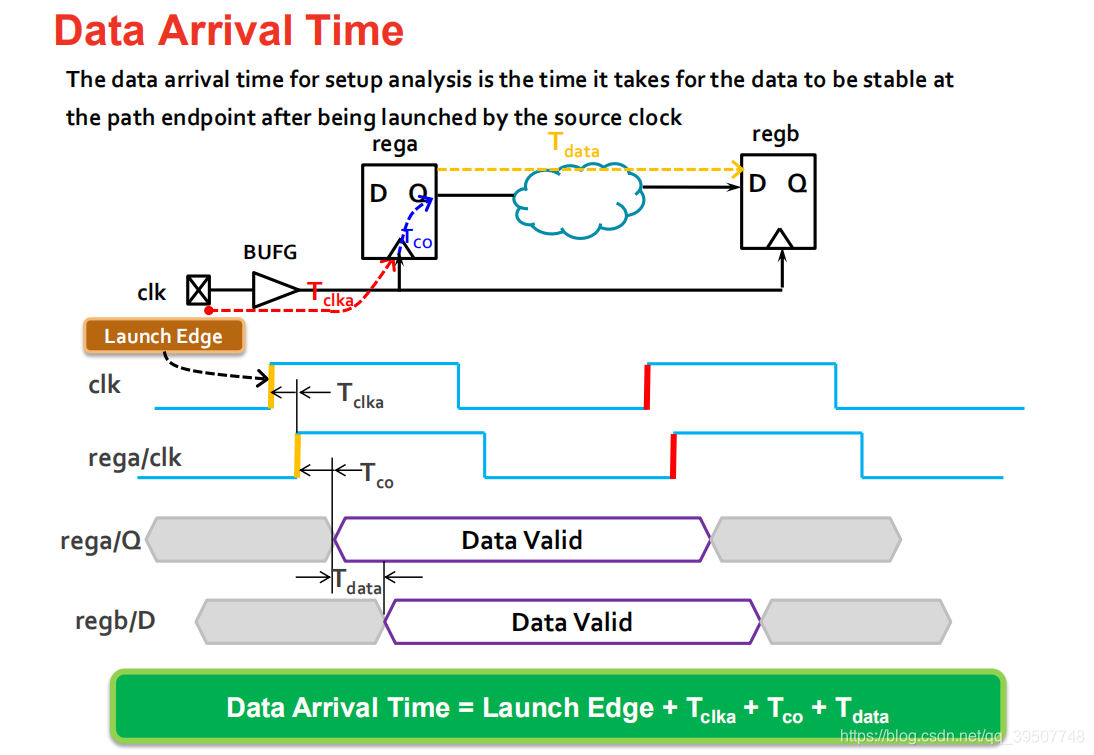

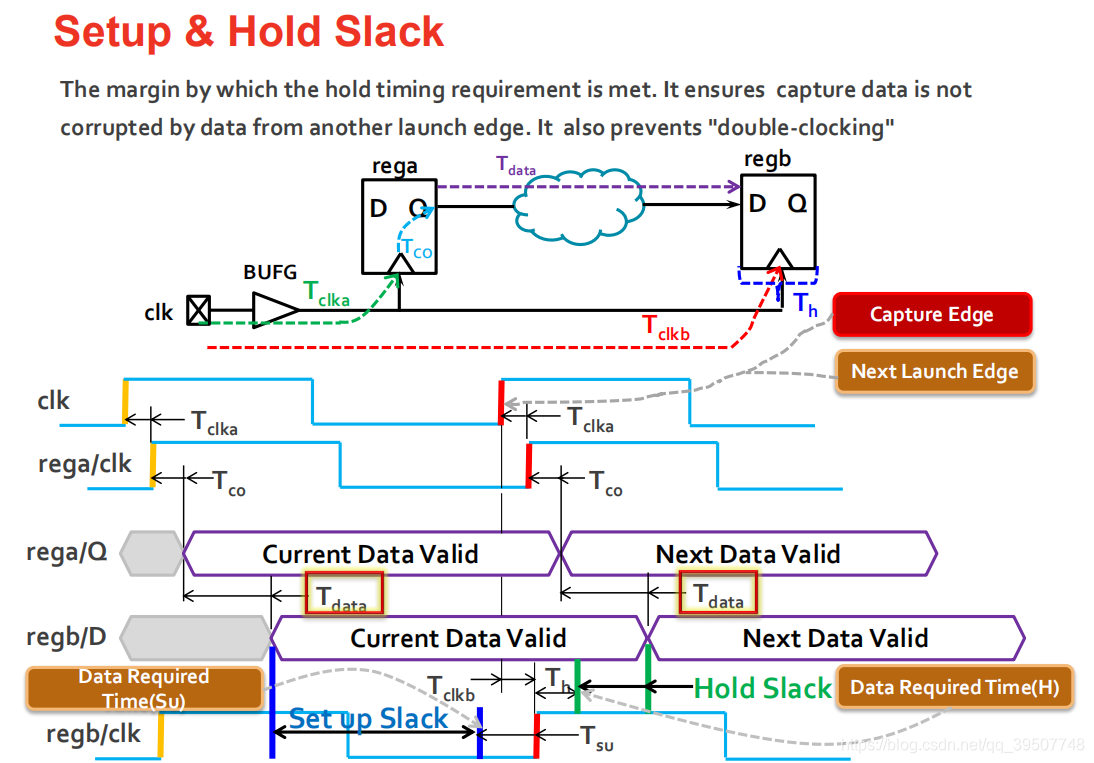

3、Data Arrival Time(setup): 建立时间数据到达时间

如果是hold的数据到达时间,则是从Capture Edge开始,再加上Tclka+Tco+Tdata;也即比setup的数据到达之间多了一个clk的时间。这里是需要区分的,因为后面计算setup和hold的裕量时会用到。

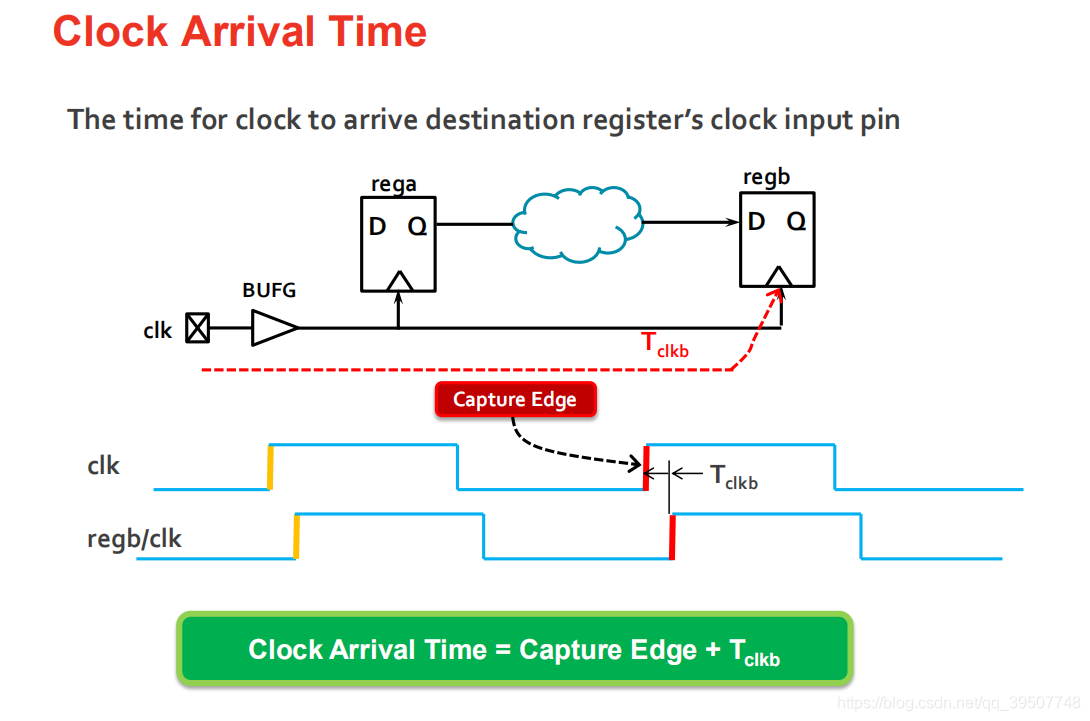

4、Clock Arrival Time: 目的寄存器时钟到达时间

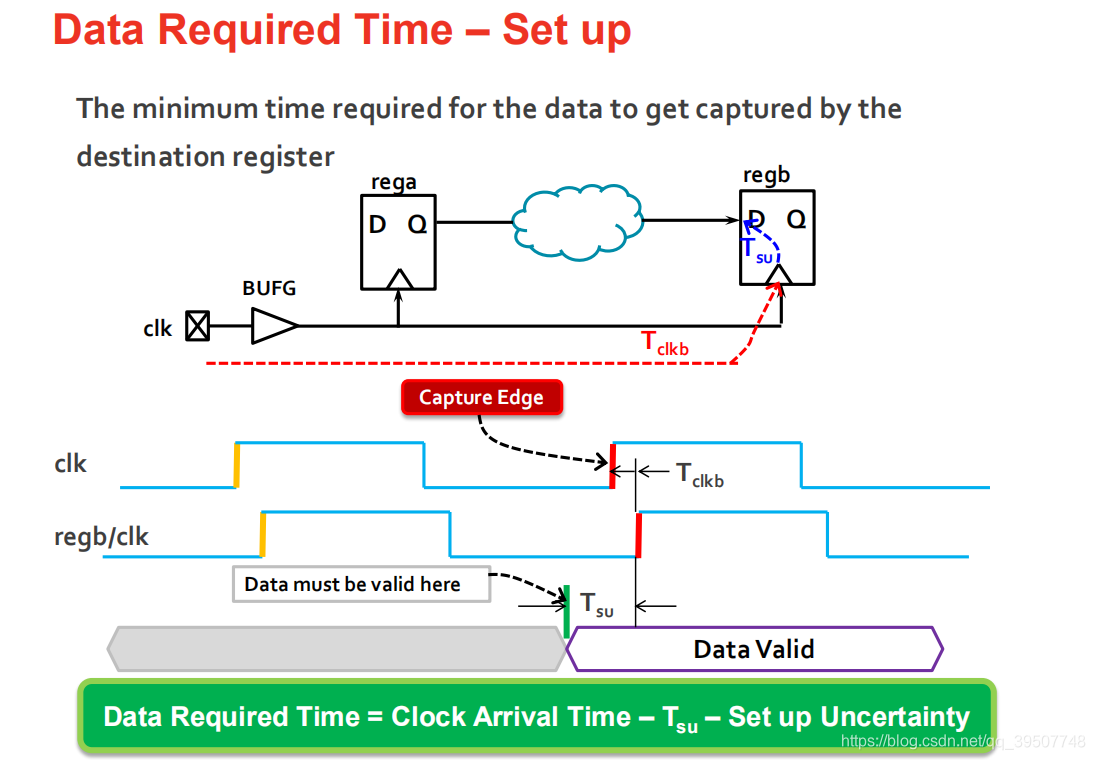

5、Data Required Time — Set up:建立时间的数据需求时间:

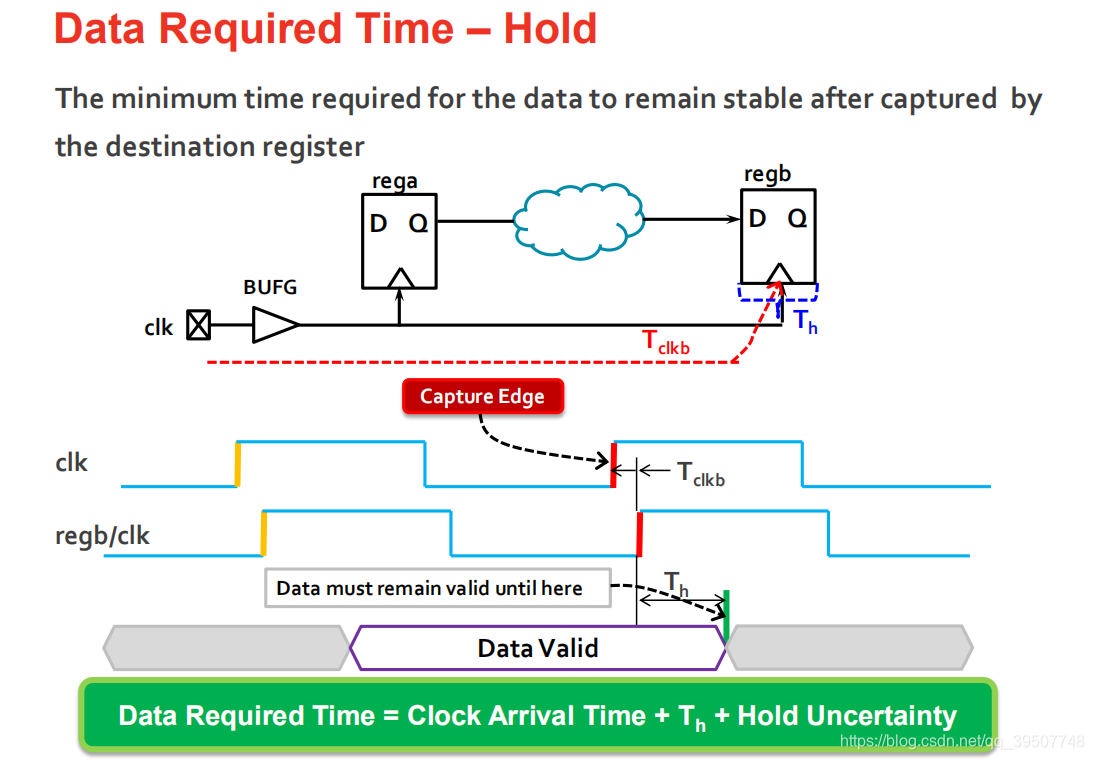

6、Data Required Time – Hold:保持时间的数据需求时间:

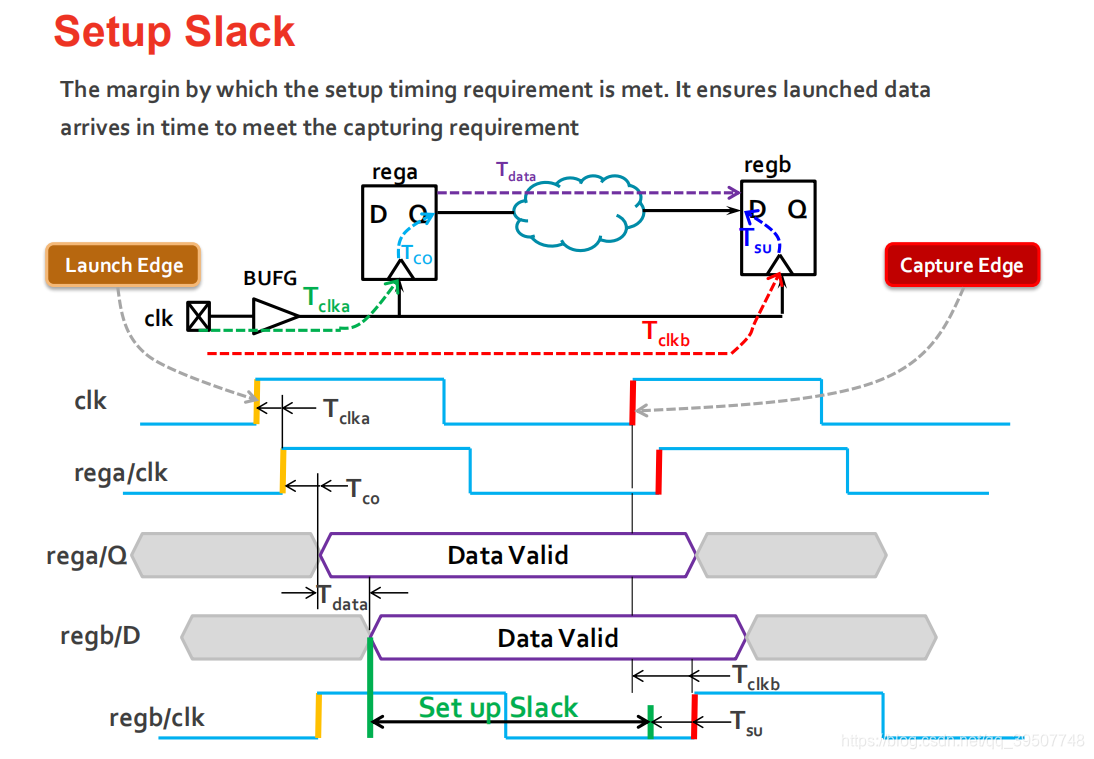

7、Setup Slack – 建立时间裕量

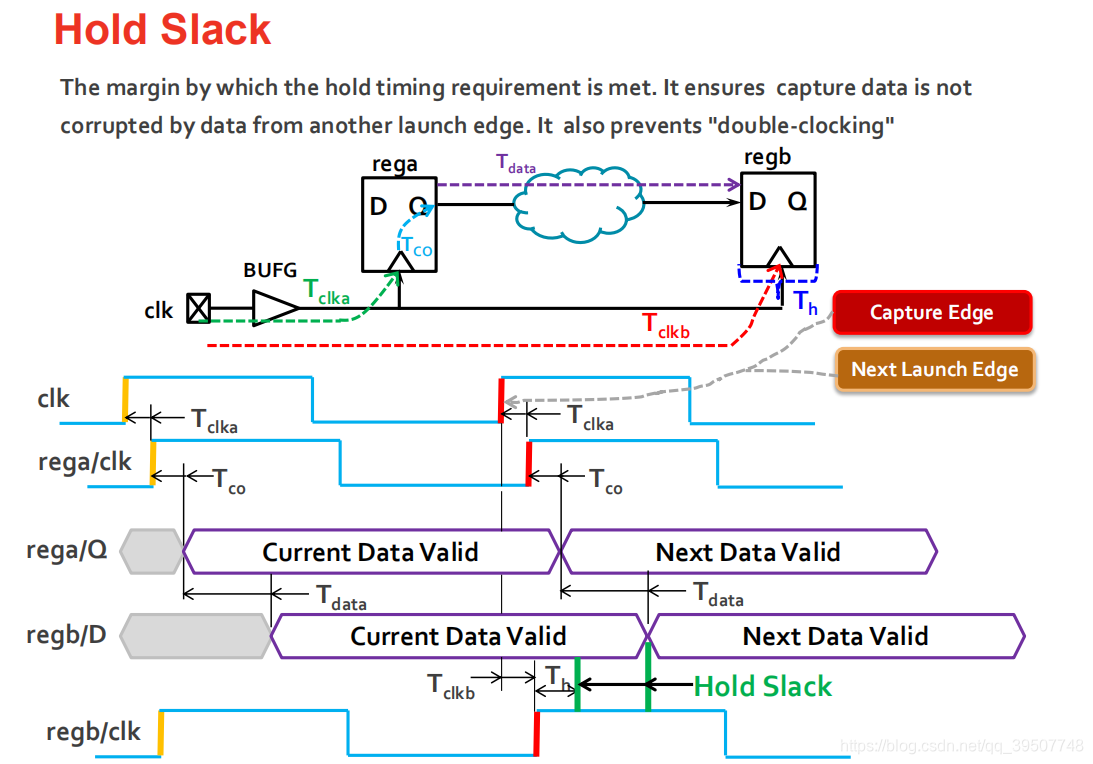

8、Hold Slack – 保持时间裕量

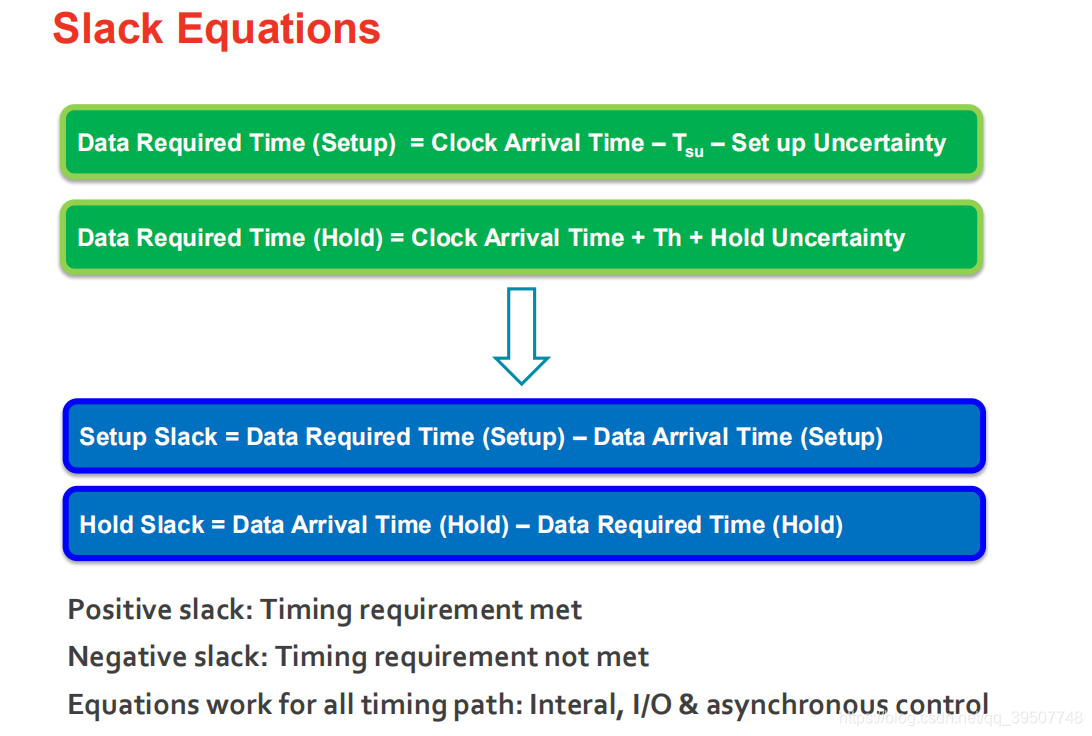

9、建立时间和保持时间裕量的公式

这里需要注意的是,Data Arrival Time(Setup)和Data Arrival Time(Hold)是不一样的,后者比前者多了一个clk,也即它代表的是下一个数据到达的时间,也即上一个数据无效的时间。

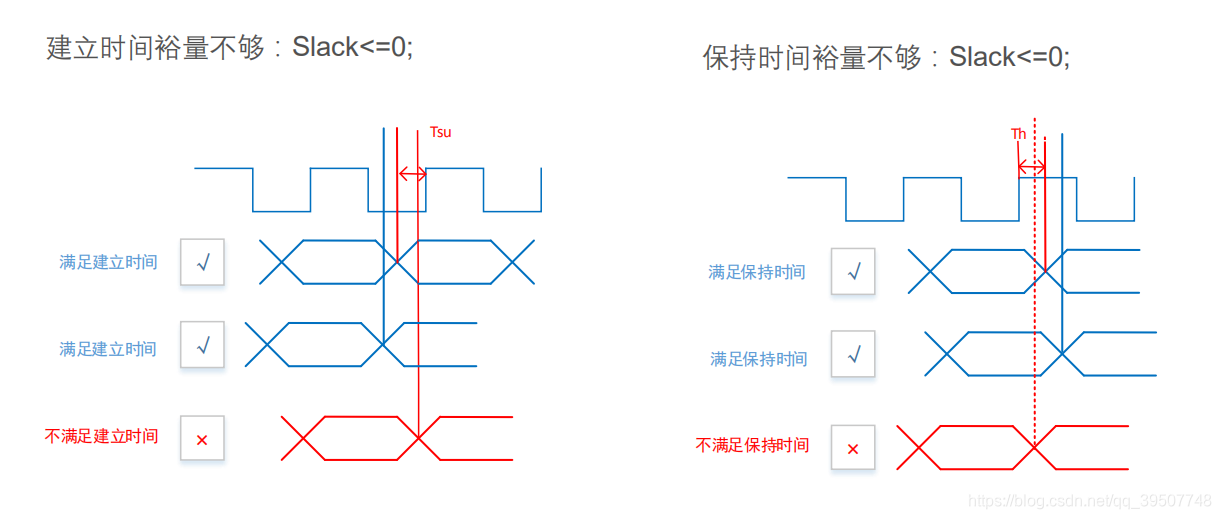

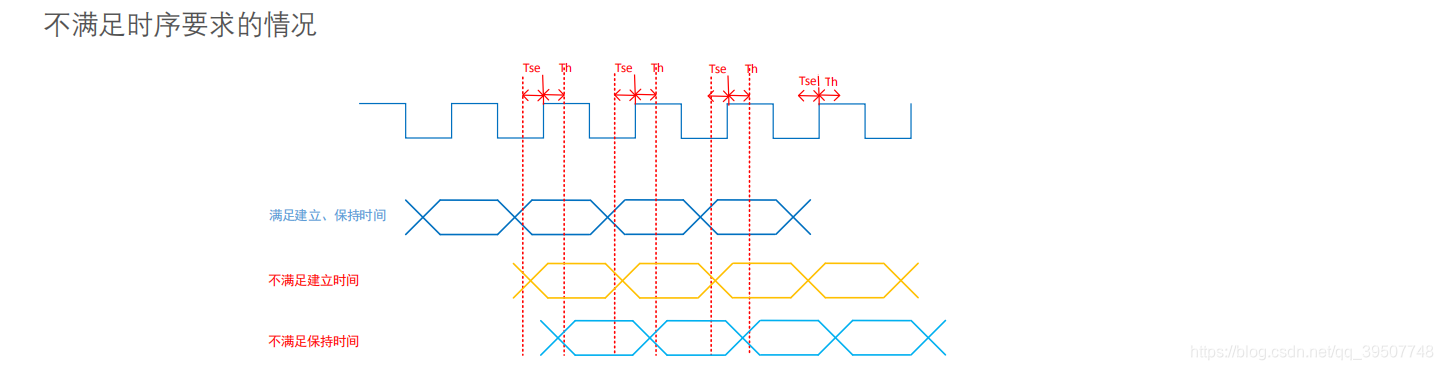

当时间裕量slack>0时满足时序要求,如果小于0则不满足,如下图所示:

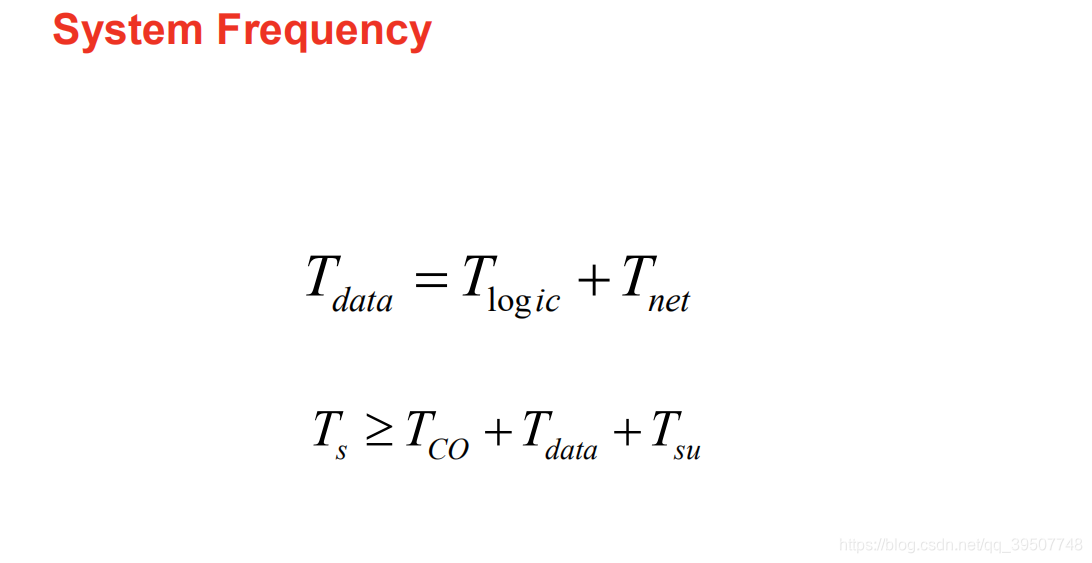

10、数据的延迟都有哪些?

| 参数名称 | 含义 |

|---|---|

| 建立时间Tsu | 器件工艺决定,是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。 |

| 保持时间Thold | 器件工艺决定,是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。 |

| Tco | 延迟由器件工艺决定,为寄存器时钟达到以后数据出现在输出端的延迟; |

| Tlogic | 组合逻辑处理时间,由用户的代码决定; |

| Tnet | 芯片内部布线延迟,由EDA工具决定; |

11、什么情况会出现建立时间不满足要求?

- 组合逻辑处理时间太长!

12、什么情况会出现保持时间不满足要求?

- 跨时钟域设计中;

- 数据源端由寄存器产生,并且数据到下一个寄存器几

乎是直接相连(出现的概率很低)。

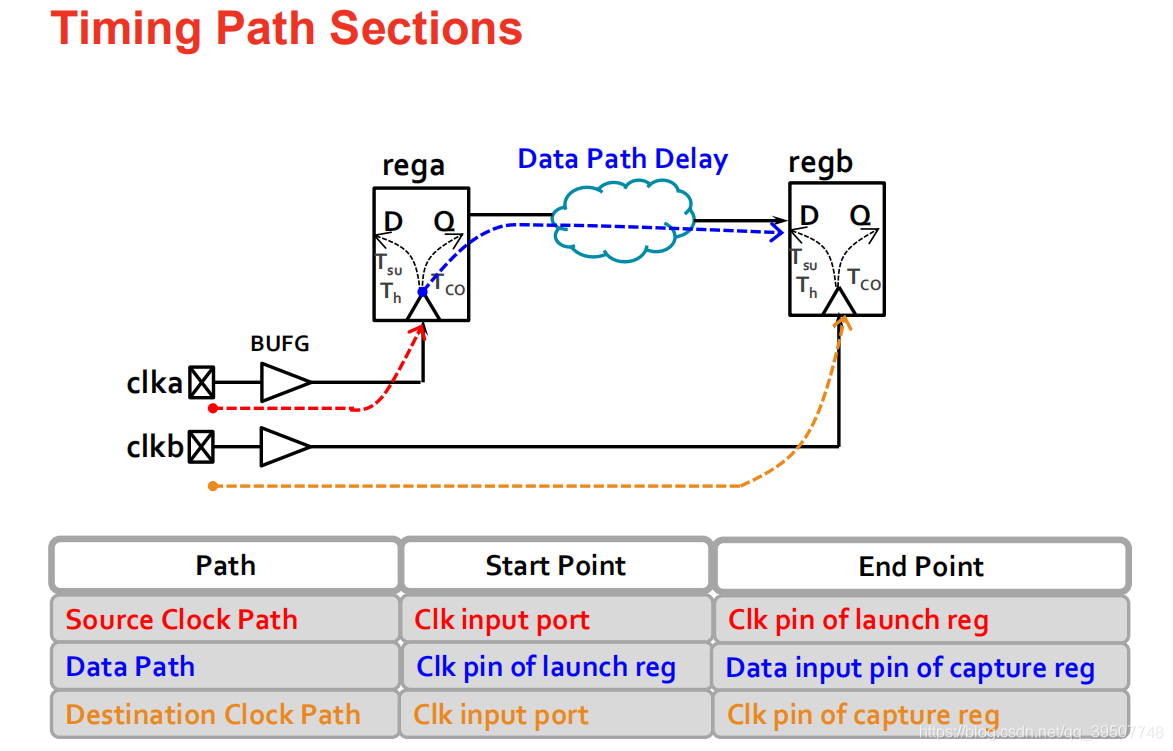

附:时序路径的三个部分

这里之所以要单独拿出来说,是因为你会发现在后面对某一个路径进行时序分析的时候,都是将时序路径分成这三部分;然后通过计算每一部分的延迟,再结合建立时间和保持时间,最终得到相应的slack(裕量),根据slack的值是否≥0以判断时序是否符合要求。

-

source clock path + data path = 实际的数据到达延迟路径;

-

T(destination clock path) - Ts(或者+Th) = 数据需求时间;

需要注意的是:

在计算数据需求时间时,如果是对建立时间进行时序分析,那么在T(destination clock path) - Ts中,destination clock path的初始时间就是一个clock周期;

而在对保持时间进行时序分析的时候,在T(destination clock path) +Th中,destination clock path的初始时间为0。