一、RTL代码

module edge_detect(

input clk ,

input rst_n,

input a ,

output y1 ,

output y2 ,

output y3

);

reg a_dly1 ;

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0)

a_dly1 <= 1'b0 ;

else

a_dly1 <= a ;

end

assign y1 = a & ( ~a_dly1 ) ;

assign y2 = ~a & a_dly1 ;

assign y3 = a ^ a_dly1 ;

endmodule

二、测试代码

`timescale 1ns / 1ps

module tb();

reg sys_clk;

reg sys_rst_n;

reg a ;

wire y1;

wire y2;

wire y3;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

a = 1'b0;

#200

sys_rst_n = 1'b1;

#100

a = 1'b1;

#100

a = 1'b0;

end

always #10 sys_clk = ~sys_clk;

edge_detect u_edge_test(

.clk (sys_clk ),

.rst_n (sys_rst_n),

.a (a ),

.y1 (y1 ),

.y2 (y2 ),

.y3 (y3 )

);

endmodule

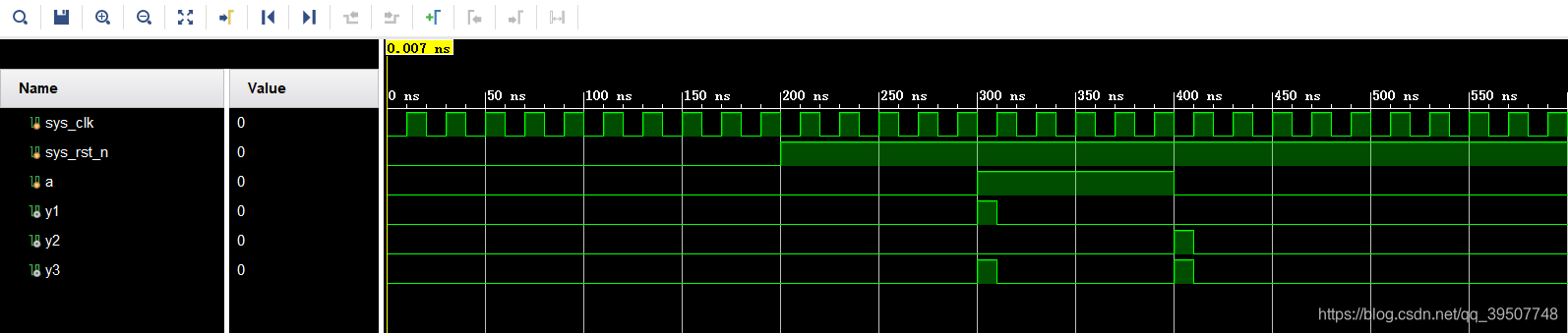

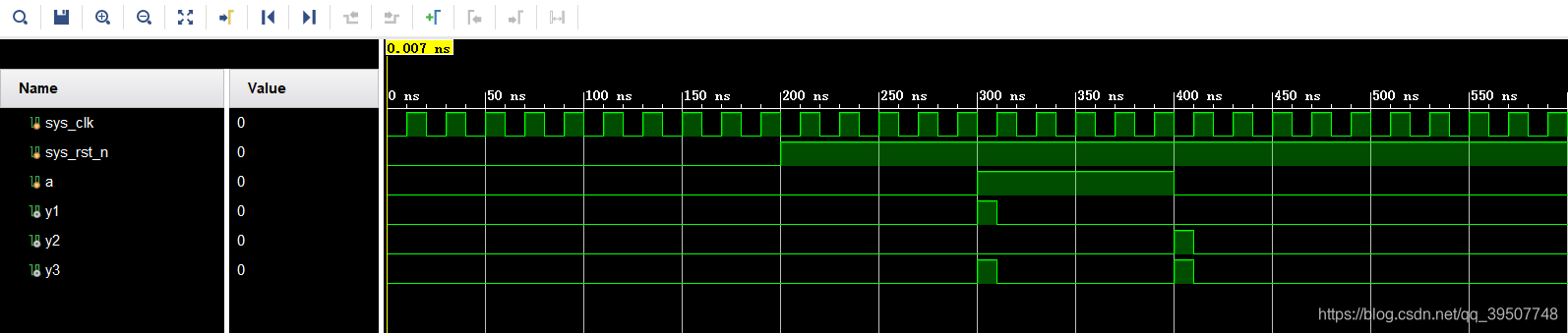

三、仿真结果