Linux下make/Makefile项目自动化构建工具

了解make和Makefile

-

Makefile:是一个文本文件,记录的是一个项目的构建规则流程。

-

make:是一个工具,用来执行Makefile文本中的相关动作,如编译、链接等。

-

简单来说就是用Makefile编辑好想要执行的命令,然后用make来执行Makefi里面的命令,不用再去一步一步的输入。

Makefile的编写规则

- 目标对象和依赖对象:比如一个test.c文件,要将它编译后生成一个test可执行文件,那么test.c就是依赖对象,可执行文件test就是目标对象。

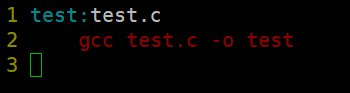

- 语法规则:目标对象:依赖对象,换行后,插入制表符tab键,然后输入要执行的命令。

test:test.c

生成命令

- $@:表示目标对象; $^:表示依赖对象; $<:表示依赖对象的第一个

make的执行规则

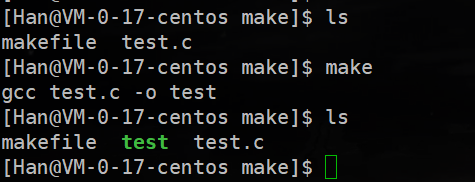

- 在命令行中执行make指令,表示运行make解释程序,程序会在当目录下找到Makefile这个文件,执行里面的项目构建规则。

- 在Makefile规则中,找到要生成的第一个目标对象。

- 先判断目标对象是否存在,如果不存在则执行对象生成的命令。

- 如果目标对象已经存在,判断是否重新生成。根据test.c源码文件最后一次修改时间来对比。

- make每次只会在Makefile中找到第一个目标对象进行生成,完成后就会退出,不会再去生成第二个对象。

- make在生成目标对象时,会先去查找依赖对象的生成规则,先生成依赖对象,然后再去生成目标对象。

第5、6点在后面会详细说

实际用法

-

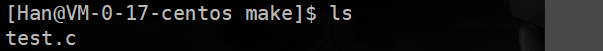

首先准备一个test.c文件。

-

vim Makefile编辑要执行的命令,注意换行后输入的是tab,不是空格。

-

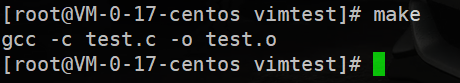

保存退出,命令行模式下执行make指令,系统就会找到Makefile中的项目构建规则进行对目标对象的生成。

项目构建的主要过程

程序的编译过程主要分为:预处理,编译,汇编,链接这四部。

在项目构建中,主要分为两步:编译与链接。

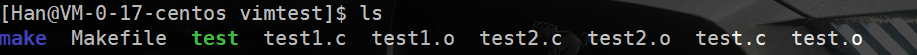

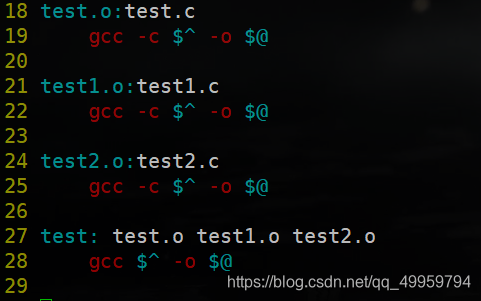

- 创建三个 .c文件,test.c、test1.c、test2.c

- 在Makefile中先个各自生成他们的 .o文件,就是先进行编译,然后将他们进行链接。

$@:表示目标对象;

$^:表示依赖对象;

$<:表示依赖对象的第一个

这时我们执行make指令会发现之执行了第一个目标对象的生成,就是只生成的test.o,没有执行后面的语句,这就是上面说到的make执行规则,每次只会在Makefile中找到第一个目标对象进行生成,完成后就会退出,不会再去生成第二个对象。

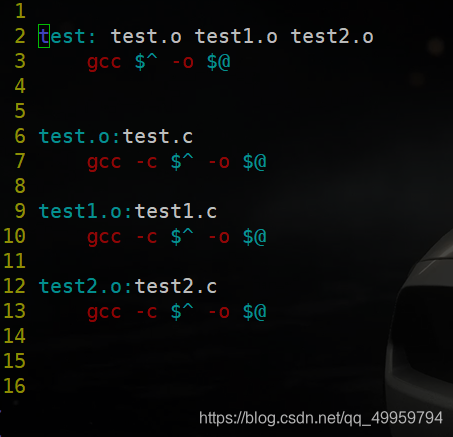

但是make在生成目标对象时,会先去查找依赖对象的生成规则,先生成依赖对象,然后再去生成目标对象。所以我们Makefile中进行修改。

这里先找到要生成的目标对象test,然后依赖对象有三个 .o文件,但是现在并没有生成 .o文件,所以会先执行依赖文件的生成规则,然后再进行链接,生成test这个目标对象。

这时我们再返回命令行输入make就可以发现他可以正常执行了。