典型共发射极放大电路设计

电路原理图

步骤1:确定性能指标参数

在进行电路设计时,首先要明确“设计什么样性能的电路”,这取决于实际需求。

本次设计的性能指标如下表所示

| 电压增益 | 5倍(14dB) |

| 输出电压范围 | ±1.5V |

| 频率特性 | 1MHz |

步骤2:确定 R E R_{E} RE上的直流压降

晶体管的基极-发射极之间等效为一个二极管,所以VBE同二极管一样具有 -2.5mV/℃ 的温度特性。

为了吸收基极-发射极间电压 VBE 随温度的变化(这里的吸收不是指减小 VBE 随温度的变化,而是减小因 VBE 随温度变化而导致的集电极电流变化),使工作点(集电极电流)稳定, RE 的直流压降必须比 ΔVBE(max) 大得多(一般为10倍以上)。

基极电流相对于集电极电流来说很小( IB 约等于 1/hFE 倍 IC ,hFE 通常为几十至几百),所以 IB 可以忽略不计,故而认为 I C = I E = V E R E I_{C}=I_{E}=\frac{V_{E}}{R_{E}} IC=IE=REVE。若 RE 上的直流压降 VE 十倍于 ΔVBE(max) ,则 IC 随温度的变化量ΔIC不会超过十分之一。

假设电路实际最大工作温度为50℃,则:

Δ V B E ( m a x ) = − 2.5 m V / ℃ × ( 50 ℃ − 25 ℃ ) = 0.0875 V \Delta V_{BE(max)}=-2.5mV/℃\times (50℃-25℃)=0.0875V ΔVBE(max)=−2.5mV/℃×(50℃−25℃)=0.0875V

为减小温度对静态工作点的影响,通常RE的直流压降必须在1V以上。

因输入电压 vi 通过基极-发射极间的等效二极管直接叠加在 RE 上,所以为了保证在输入信号 vi 的负峰值处晶体管不进入截止状态 ,VE 必须大于输入信号负峰值的绝对值。由步骤1中的设计指标可推算出输入电压负峰值为 -0.3V 。

本设计中我们取VE=1V。

步骤3:确定集电极电流的工作点

要考虑的因素主要有特征频率和功耗,特征频率表示交流放大系数为1时的频率。

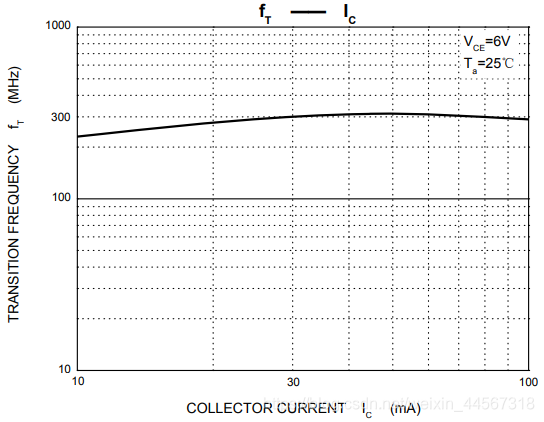

从低功耗方面考虑 IC 越小越好;从特征频率考虑 IC 必须在某一区间内,具体需查看晶体管的数据手册,下图为S9013三极管的特征频率和集电极电流的关系。

步骤1性能指标中给出的特征频率要求为1MHz,由上图可知, IC=10mA 时特征频率大于100MHz,可以满足我们的设计要求。

再考虑静态功耗,本设计取 IC=1mA。

步骤4:确定 R C R_{C} RC和 R E R_{E} RE

由于基极-发射极间存在的二极管是在导通情况下工作的(V-I曲线无限陡峭,交流电阻为0,导通压降0.6 ~ 0.7V),所以基极端子的交流电位(=vi )直接地出现在发射极。

故输入信号 vi 的电压变化在 RE 上转换成电流变化 Δ i e = v i R E \Delta i_{e}=\frac{v_{i}}{R_{E}} Δie=REvi ,因为 Δib 相对于 Δic 可以忽略,进而可认为 Δic= Δie。

利用集电极与电源之间的电阻RC, Δic 以在电阻RC上产生压降的形式再次变回到电压的变化 Δ v c = Δ i c × R C = v i R E × R C \Delta v_{c}=\Delta i_{c}\times R_{C}=\frac{v_{i}}{R_{E}}\times R_{C} Δvc=Δic×RC=REvi×RC。

因输出耦合电容将 vc 的直流成分截去,故输出交流信号 vo 即为 Δvc 本身。因此,该电路的交流电压放大倍数 A v = v o v i = R C R E A_{v}=\frac{v_{o}}{v_{i}}=\frac{R_{C}}{R_{E}} Av=vivo=RERC 。

步骤1性能指标中要求电压增益为5倍,所以 Rc:RE=5:1;

步骤2中为减小温度对工作点的影响,确定了 VE=1V;

步骤3中根据特征频率要求和功耗考虑确定了 IE=1mA;

故可得 R E = V E I E = 1 V 1 m A = 1 k Ω R_{E}=\frac{V_{E}}{I_{E}}=\frac{1V}{1mA}=1k\Omega RE=IEVE=1mA1V=1kΩ , R C = 5 R E = 5 k Ω R_{C}=5R_{E}=5k\Omega RC=5RE=5kΩ 。

步骤5:确定电源电压

要确定电源电压,最大输出电压是重点。为了输出步骤1性能指标中给出的 3Vp-p 输出电压,显然必须要3V以上的电源电压。

其次,步骤2中确定了 RE 上的直流压降 VE=1V,在静态工作点上, RC 上的压降为 AV·VE=5V,当输入电压 vi 为正峰值 0.3V 时,RC 上的最大压降为6.5V,所以电源电压必须要 7.8V(VE + vi(max) + vRc(max))以上。

再者,当晶体管进入饱和状态之后,hFE将减小,以至于基极电流相对于集电极电流来说不再可以忽略。所以为避免晶体管进入饱和状态,电源电压必须高于 VE + vi(max) + vRc(max) + VCE(sat) ,其中 VCE(sat) 为晶体管的集电极-发射极饱和电压。

本设计采用S9013三极管, VCE(sat)=0.6V ,所以电源电压要 8.4V 以上,这里决定采用12V电源供电。

晶体管的集电极-发射极间电压:

V C E = V C C − I C ⋅ R C − I E ⋅ R E V_{CE}=V_{CC}-I_{C}·R_{C}-I_{E}·R_{E} VCE=VCC−IC⋅RC−IE⋅RE

= 12 V − 1 m A ⋅ 5 k Ω − 1 V = 6 V =12V-1mA· 5k\Omega -1V=6V =12V−1mA⋅5kΩ−1V=6V

晶体管的集电极静态损耗:

P C = V C E ⋅ I C P_{C}=V_{CE}·I_{C} PC=VCE⋅IC

= 6 V × 1 m A = 6 m W =6V\times 1mA=6mW =6V×1mA=6mW

步骤6:基极偏置电路设计

步骤2中选定了 VE=1V,由于 VBE=0.6V,所以基极电位必须是1.6V(=1V+0.6V)。

如果 R1与R2 流过比基极电流大得多的电流,那么 IB 就可以忽略,基极电位就可以认为是 R1与R2 分压后的电位。

本设计选用 H档(放大倍数200 ~ 350)的S9013三极管,假设 hFE=200,因为 IC=1mA,则基极电流为 0.005mA。

这里 R1与R2 上流动的电流取 0.1mA (一般误差在十分之一以下是可以忽略的),即 R1与R2 :

R 1 = 10.4 V 0.1 m A = 104 k Ω R_{1}=\frac{10.4V}{0.1mA}=104k\Omega R1=0.1mA10.4V=104kΩ

R 2 = 1.6 V 0.1 m A = 16 k Ω R_{2}=\frac{1.6V}{0.1mA}=16k\Omega R2=0.1mA1.6V=16kΩ

计算所得的阻值可能是 E24 系列电阻中没有的,在这里选取 R1=100K,R2=15K(104:16≈100:15)。

步骤7:确定耦合电容 C 1 C_{1} C1与 C 2 C_{2} C2

C1 和 C2 分别是将基极、集电极的直流成分隔离仅让交流成分通过的耦合电容。

但是 C1 与输入阻抗、C2 与负载阻抗均形成了高通滤波器,当 C1 和 C2 取值不恰当时,难于通过低频信号。

高通滤波器的截止频率(振幅特性下降 3dB —— 即下降 1 2 \frac{1}{\sqrt{2}} 21)为:

f = 1 2 π ⋅ C ⋅ R f=\frac{1}{2\pi ·C·R} f=2π⋅C⋅R1

dB是一个比值,一种纯计数方式,增益 dB 是倍数的另一种说法,对于电压来说X倍可以记作 20lg(X) dB。

晶体管基极电流很小,所以晶体管的输入阻抗可以看作非常大,而电源阻抗可以看作为0Ω。

计算输入阻抗时,把电压源看作短路,电流源看作开路。则放大电路的输入阻抗为 R1 与 R2 的并联 R1//R2。

本设计取 C1=C2=47μF,输入截止频率为:

f c = 1 2 π ⋅ C ⋅ R = 1 2 π × 47 μ F × 13 k Ω = 0.26 H z f_{c}=\frac{1}{2\pi ·C·R}=\frac{1}{2\pi \times 47\mu F\times 13k\Omega }=0.26Hz fc=2π⋅C⋅R1=2π×47μF×13kΩ1=0.26Hz

由 C2 与负载形成的高通滤波器的 f e f_{e} fe,会因输出端接有不同的负载阻抗而发生变化,因此预先考虑一下接有什么样的负载是至关重要的。

步骤8:确定电源去耦电容 C 3 C_{3} C3与 C 4 C_{4} C4

C3 与 C4 是电源的去耦电容,当没有这个电容时,电路的交流特性会变得很奇特,严重时电路产生振荡。

理想电容的容抗是 f = 1 2 π ⋅ C ⋅ R f=\frac{1}{2\pi ·C·R} f=2π⋅C⋅R1 ,理论上频率越高,容抗应该越小。但由于实际电容内部存在感抗成分,从某个频率开始,容抗反而变高。下图所示为某品牌 47μF 陶瓷电容的阻抗频率曲线。

小电容在高频率处容抗最低,而大电容在低频率处容抗最低。为了在很宽的频率范围内降低电源对GND的容抗,通常在电源上并联一大一小两个电容。

关于更多电容阻抗-频率曲线的内容,请参考另一位博主的文章如何理解电容的阻抗-频率曲线。

大电容即使离电源远一些也没有问题,为了减小布线的阻抗,小电容要紧靠电路安置。

小电容是在高频情况下降低阻抗用的,高频下的导线等效于电感和电阻串联,如果小电容不紧靠电路安置,由于引线本身的阻抗,电源的阻抗已经不能为零了。

在低频电路中即使没有小电容,电路也能正常工作。但是在高频电路中,小电容起着更为重要的作用。

本设计采用 10μF 铝电解电容和 0.1μF 叠层陶瓷电容作为电源去耦电容。